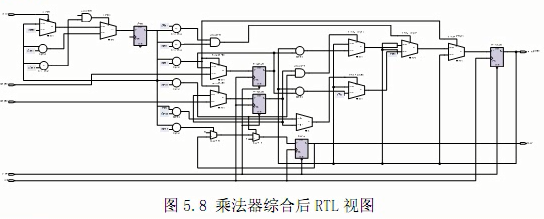

乘法器可以通過使用一系列計(jì)算機(jī)算數(shù)技術(shù)來(lái)實(shí)現(xiàn)。乘法器不僅作為乘法、除法、乘方和開方等模擬運(yùn)算的主要基本單元,而且還廣泛用于電子通信系統(tǒng)作為調(diào)制、解調(diào)、混頻、鑒相和自動(dòng)增益控制;另外還可用于濾波、波形形成和頻率控制等場(chǎng)合,因此是一種用途廣泛的功能電路。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

606012 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7536瀏覽量

88641 -

乘法器

+關(guān)注

關(guān)注

8文章

206瀏覽量

37193

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

#硬聲創(chuàng)作季 #FPGA 玩轉(zhuǎn)FPGA-12 BJ-EPM240實(shí)驗(yàn)5-乘法器設(shè)計(jì)實(shí)驗(yàn)-1

#硬聲創(chuàng)作季 #FPGA 玩轉(zhuǎn)FPGA-12 BJ-EPM240實(shí)驗(yàn)5-乘法器設(shè)計(jì)實(shí)驗(yàn)-2

怎么設(shè)計(jì)基于FPGA的WALLACETREE乘法器?

基于FPGA的WALLACE TREE乘法器設(shè)計(jì)

基于BJ-EPMCPLD 開發(fā)板的串口通信實(shí)驗(yàn)

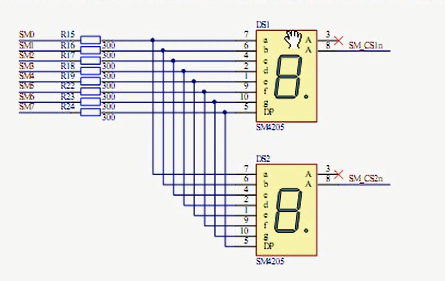

FPGA視頻教程之使用BJ-EPM240學(xué)習(xí)板進(jìn)行數(shù)碼管顯示實(shí)驗(yàn)的資料說明

FPGA視頻教程之BJ-EPM240學(xué)習(xí)板的詳細(xì)資料介紹

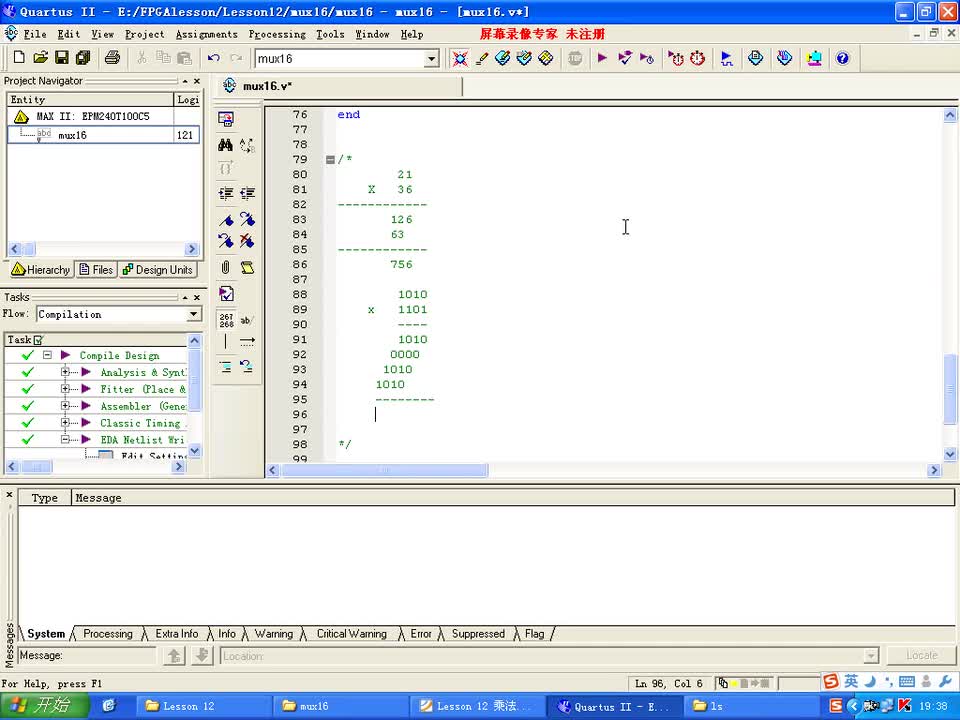

FPGA視頻教程之BJ-EPM240學(xué)習(xí)板乘法器設(shè)計(jì)實(shí)驗(yàn)的詳細(xì)資料說明

BJ-EPM240學(xué)習(xí)板介紹

BJ-EPM240學(xué)習(xí)板之Johnson.計(jì)數(shù)器實(shí)驗(yàn)

BJ-EPM240學(xué)習(xí)板之乘法器設(shè)計(jì)實(shí)驗(yàn)

課程5:BJ-EPM240學(xué)習(xí)板介紹

深入淺出玩轉(zhuǎn)FPGA視頻:BJ-EPM240學(xué)習(xí)板介紹

FPGA視頻教程:BJ-EPM240學(xué)習(xí)板介紹

BJ-EPM240學(xué)習(xí)板:乘法器設(shè)計(jì)實(shí)驗(yàn)

FPGA視頻教程:BJ-EPM240學(xué)習(xí)板-乘法器設(shè)計(jì)實(shí)驗(yàn)

FPGA視頻教程:BJ-EPM240學(xué)習(xí)板-乘法器設(shè)計(jì)實(shí)驗(yàn)

評(píng)論