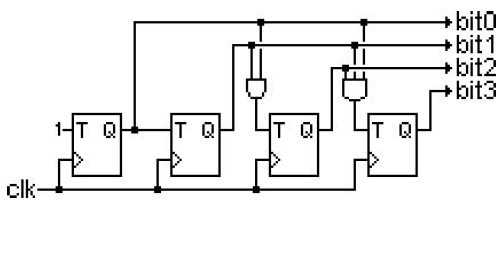

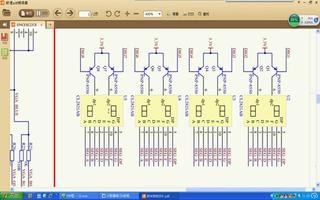

計(jì)數(shù)是一種最簡(jiǎn)單基本的運(yùn)算,計(jì)數(shù)器就是實(shí)現(xiàn)這種運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對(duì)脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測(cè)量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能.

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605999 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2261瀏覽量

94983 -

邏輯

+關(guān)注

關(guān)注

2文章

833瀏覽量

29515

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于FPGA的PWM計(jì)數(shù)器改進(jìn)設(shè)計(jì)

EDA實(shí)驗(yàn)4-10進(jìn)制計(jì)數(shù)器

集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)

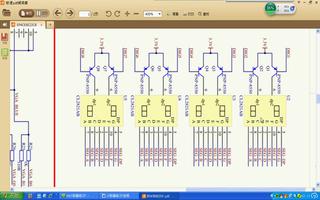

采用FPGA DIYK開(kāi)發(fā)板控制模為60的計(jì)數(shù)器數(shù)碼管動(dòng)態(tài)顯示

FPGA基礎(chǔ)應(yīng)用計(jì)數(shù)器的實(shí)例詳細(xì)說(shuō)明

采用FPGA技術(shù)實(shí)現(xiàn)計(jì)數(shù)器的設(shè)計(jì)(4)

采用FPGA技術(shù)實(shí)現(xiàn)計(jì)數(shù)器的設(shè)計(jì)(4)

評(píng)論