本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎應用、綜合應用和進階應用。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606037 -

Verilog HDL

+關(guān)注

關(guān)注

17文章

126瀏覽量

50478 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66892

發(fā)布評論請先 登錄

相關(guān)推薦

淺析嵌入式FPGA與HDL硬件描述語言

)領域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。HDL硬件描述語言(HDL)是一種用來設計數(shù)字邏輯系統(tǒng)和描述

發(fā)表于 12-22 07:39

Verilog硬件描述語言描述.

本書簡要介紹了Verilog硬件描述語言的基礎知識,包括語言的基本內(nèi)容和基本結(jié)構(gòu) ,以及利用該語言在各種層次上對數(shù)字系統(tǒng)的建模方法

發(fā)表于 03-27 23:44

?101次下載

vhdl硬件描述語言(教材課件)

數(shù)字系統(tǒng)設計分為硬件設計和軟件設計, 但是隨著計算機技術(shù)、超大規(guī)模集成電路(CPLD、FPGA)的發(fā)展和硬件描述語言(HDL, Hardwa

發(fā)表于 09-11 15:15

?91次下載

VHDL硬件描述語言與數(shù)字邏輯電路設計

VHDL硬件描述語言與數(shù)字邏輯電路設計:本書系統(tǒng)地介紹了一種硬件描述語言,即VHDL語言設計

發(fā)表于 02-06 16:55

?363次下載

FPGA教程之AHDL硬件描述語言的詳細資料說明

本文檔詳細介紹的是FPGA教程之AHDL硬件描述語言的詳細資料說明主要內(nèi)容包括了:1 硬件描述語言(HDL)概述,2 Altera 的

發(fā)表于 02-27 17:27

?22次下載

基于Verilog硬件描述語言的IEEE標準硬件描述語言資料合集免費下載

本文檔的主要內(nèi)容詳細介紹的是基于Verilog硬件描述語言的IEEE標準硬件描述語言資料合集免費下載:1995、2001、2005;SystemVerilog標準:2005、2009

發(fā)表于 06-18 08:00

?10次下載

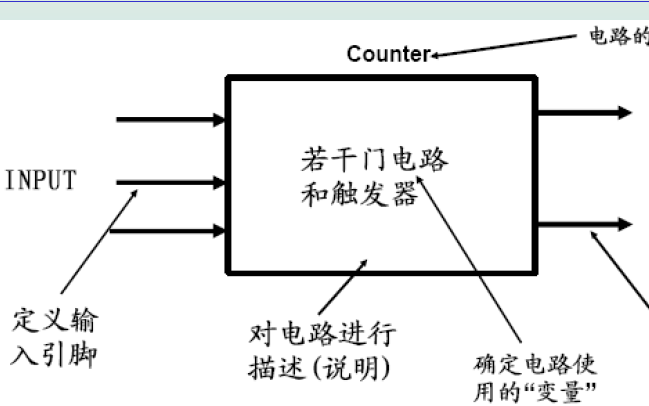

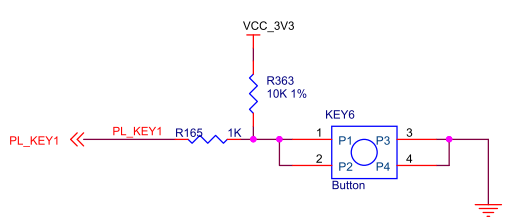

硬件描述語言和FPGA的具體關(guān)系

按鍵是FPGA設計當中最常用也是最簡單的外設,本章通過按鍵檢測實驗,檢測開發(fā)板的按鍵功能是否正常,并了解硬件描述語言和FPGA的具體關(guān)系,學習Viv

使用Verilog/SystemVerilog硬件描述語言練習數(shù)字硬件設計

HDLBits 是一組小型電路設計習題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習數(shù)字硬件設計~

基于硬件描述語言HDL的FPGA開發(fā)

基于硬件描述語言HDL,抽象出HLS(High-Level Synthesis)(翻譯為高層次綜合?怎么聽起來都沉得別扭)技術(shù),通過高層設計去隱藏很多底層邏輯和細節(jié),讓FPGA的開發(fā)更加簡單。

發(fā)表于 09-05 09:12

?894次閱讀

數(shù)字設計FPGA應用:硬件描述語言與VIVADO

數(shù)字設計FPGA應用:硬件描述語言與VIVADO

評論