對全新芯片堆疊技術的全面支持確保實現最高性能的3D-IC解決方案

解決方案包括多裸晶芯片版圖設計實現、寄生參數提取和時序分析,以及物理驗證

幫助早期合作伙伴加速高度集成的新一代產品投放市場

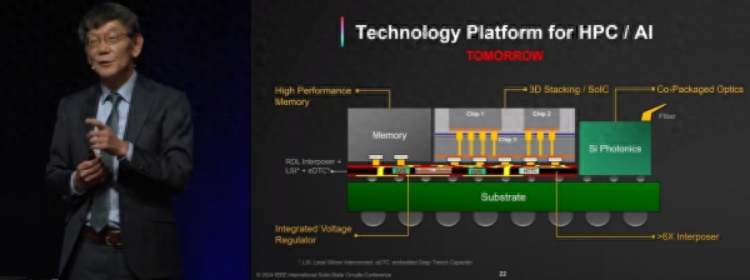

新思科技(Synopsys, Inc. 納斯達克股票代碼:SNPS)近日宣布,新思科技設計平臺已通過臺積電(TSMC)最新系統整合單晶片(TSMC-SoIC?)3D芯片堆疊技術認證。該平臺將全面支持這一技術,并與高度靈活的設計參考流程相結合,可立即為用戶部署高性能、高連接性的多裸晶芯片技術解決方案,涵蓋移動計算、網絡通信、消費和汽車電子等多種應用。

以新思科技設計實現和signoff解決方案為中心,高容量設計參考方法包括先進的電介質通孔(TDV)建模、多裸晶芯片版圖繪制、物理布局規劃和實現、寄生參數提取和時序分析,以及高度可擴展的物理驗證。

新思科技設計平臺

支持臺積電先進的SoIC芯片堆疊技術

其主要產品和功能包括:

●IC Compiler? II布局布線:用于高度復雜的多裸晶芯片IC(集成電路)的高效設計繪制和靈活規劃。高質量的布線支持包括硅通孔(TSV)、TDV,凸塊(Bump)和再分布引線層(RDL)連接解決方案。

●PrimeTime?時序signoff:全系統靜態時序分析,支持多裸晶芯片靜態時序分析(STA)。

●StarRC?提取signoff:3D-IC設計方法包含先進功能,可處理多裸晶芯片寄生參數交互以及新的TDV和TSV建模。

●IC Validator物理signoff:DRC和LVS驗證,包括對SoIC跨裸晶芯片接口DRC/LVS檢查的支持。

“系統帶寬不斷提高,加上日益增加的復雜性需要我們拿出新的創新方案。因此,臺積電再次以全新的3D集成技術和極高的實現效率,幫助用戶將高度差異化的產品推向市場。我們一直保持與新思科技的良好合作,由此打造出以臺積電創新SoIC先進芯片堆疊技術為支撐的可擴展的設計方法。我們期待雙方用戶都能從這些先進的技術和服務中受益,真正實現系統級封裝。”

——Suk Lee

臺積電設計基礎架構市場部高級總監

“與臺積電最新合作成果有望在系統規模和系統有效性能方面取得突破性進展。新思科技數字設計平臺和共同開發出的相關方法學將幫助設計人員在部署新一代多裸晶芯片解決方案時更有把握地滿足時間進度要求。”

——Sassine Ghazi

新思科技芯片設計事業部聯席總經理

-

臺積電

+關注

關注

44文章

5687瀏覽量

167002 -

新思科技

+關注

關注

5文章

808瀏覽量

50424

原文標題:新思科技設計平臺通過臺積電創新SoIC芯片堆疊技術認證

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

臺積電擴大先進封裝設施,南科等地將增建新廠

消息稱臺積電完成CPO與先進封裝技術整合,預計明年有望送樣

臺積電CoWoS產能將提升4倍

臺積電SoIC封裝技術再獲蘋果青睞,2025年或迎量產新篇章

臺積電成功集成CFET架構,預計2025年2nm技術實現量產,將支持A

臺積電跨制程整合晶體管架構并引入CFET,發布新一代芯片技術

新思科技與臺積公司深度合作,推動芯片設計創新

新思科技面向臺積公司先進工藝加速下一代芯片創新

新思科技設計平臺 支持臺積電先進的SoIC芯片堆疊技術

新思科技設計平臺 支持臺積電先進的SoIC芯片堆疊技術

評論