三個步驟,PCB設(shè)計信號等長分析

01什么是PCB信號等長處理?

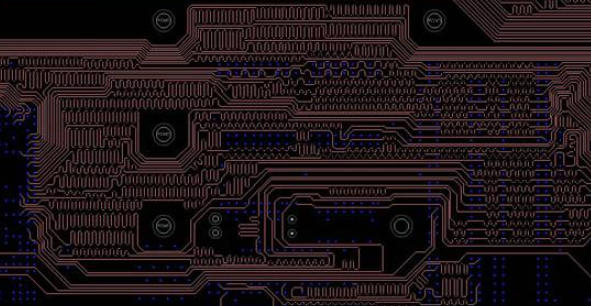

在做pcb設(shè)計時,為了滿足某一組所有信號線的總長度滿足在一個公差范圍內(nèi),通常要使用蛇形走線將總長度較短的信號線繞到與組內(nèi)最長的信號線長度公差范圍內(nèi),這個用蛇形走線繞長信號線的處理過程,就是我們俗稱的PCB信號等長處理。

02為什么要等長?

一般在PCB設(shè)計時,進(jìn)行信號等長處理的原因有以下幾個。

? 一般做等長是為了滿足系統(tǒng)對信號組的等時,即為了滿足此組內(nèi)信號的時序須滿足系統(tǒng)要求。比如對于DDR,其數(shù)據(jù)信號每8位一組,做+/-25mil處理,如果此組信號等長沒有在此公差范圍內(nèi),信號線長度相差太大,會導(dǎo)致其相對延時較長,最終導(dǎo)致DDR運(yùn)行速率不高。

但是我們做設(shè)計時有時發(fā)現(xiàn)DDR器件等長沒有做,其成品也可正常運(yùn)行,并沒產(chǎn)生影響,原因一般是系統(tǒng)軟件對此信號做了延時處理,軟件上做了時序控制。對于帶狀線來說,每1ps延時對應(yīng)的走線長度是6mil左右,所以一般信號組長度每相差6mil,其總延時在1ps。一般我們做設(shè)計時等長并不用控制的太小,控制到+/-10mil左右就已經(jīng)很好了。+/-10mil 等長和+/-1mil 等長,在時間上的差異不超過 4ps,一般的IC信號裕量都不止4ps,所以做等長時沒必要控制的過小,從而導(dǎo)致自己設(shè)計走線困難。

?差分信號(差分信號分析可查看我們的公眾號往期文章)等長是為了滿足相位,一對差分信號相位相差180度,如果長度相差太大,會導(dǎo)致其相位偏移過大。

03PCB設(shè)計時等長處理方法

?設(shè)計時我們首先要看器件的數(shù)據(jù)手冊,根據(jù)數(shù)據(jù)手冊獲取需要等長的信號及其等長范圍。對于常規(guī)的信號,如DDR、網(wǎng)口、HDMI信號等內(nèi)容,可根據(jù)設(shè)計經(jīng)驗進(jìn)行等長。

?在做等長之前,要先找到需要做等長的信號組中的最長的信號線,想辦法將其縮短,以減短此組內(nèi)所有信號線的長度及其他信號線所需要繞線的長度。

?等長處理時要考慮好空間較小位置信號的繞線,盡量先調(diào)走其附近信號,將此部分信號處理,以免做到最后其繞線空間不夠,等長不出來。

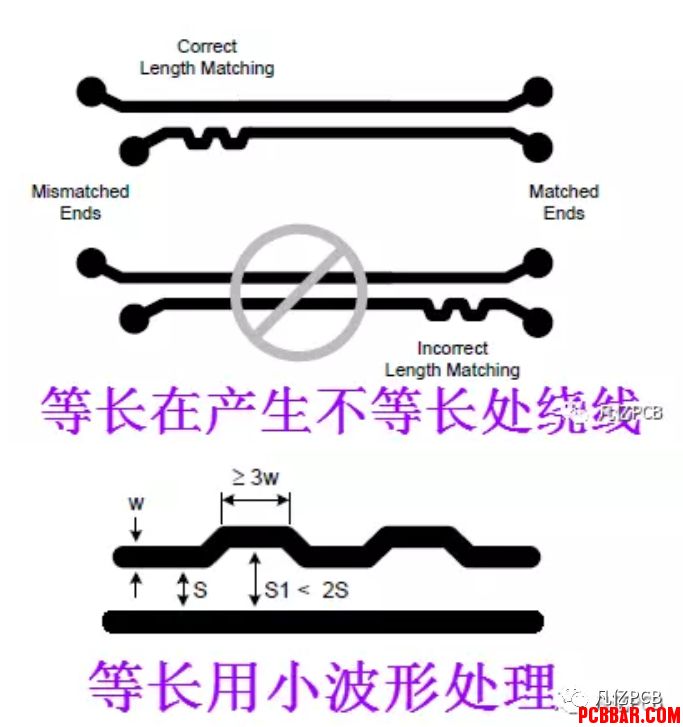

? 繞等長時,其蛇形線邊緣間距一般要保持3W,即3倍線寬大小,如果空間限制,至少要做到2W。

?對于差分信號,其等長誤差一般控制為+/-5mil,繞等長的位置在產(chǎn)生長度誤差的一端,繞的波形為小波形。

-

pcb

+關(guān)注

關(guān)注

4326文章

23161瀏覽量

399998 -

信號線

+關(guān)注

關(guān)注

2文章

176瀏覽量

21580 -

差分信號

+關(guān)注

關(guān)注

3文章

378瀏覽量

27774

原文標(biāo)題:【技術(shù)干貨】PCB設(shè)計信號等長分析——鄭振宇老師分享

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

降低PCB設(shè)計風(fēng)險的三個技巧

PCB設(shè)計規(guī)則——等長 的體會

三個方面介紹EMC的PCB設(shè)計技術(shù)

基于信號完整性分析的PCB設(shè)計解析

PCB設(shè)計的三個原則之間的影響與優(yōu)勢分析

展示PCB設(shè)計的三個R是如何相互作用

PCB設(shè)計做等長走線的目的是什么

PCB設(shè)計工程師淺談繞等長的概念

PCB設(shè)計中如何實現(xiàn)等長走線

PCB設(shè)計:為什么要繞等長?資料下載

三個步驟,PCB設(shè)計信號等長分析

三個步驟,PCB設(shè)計信號等長分析

評論