Testbench

testbench是一種驗證的手段。首先,任何設計都是會有輸入輸出的。但是在軟環境中沒有激勵輸入,也不會對你設計的輸出正確性進行評估。那么此時便有一種,模擬實際環境的輸入激勵和輸出校驗的一種“虛擬平臺”的產生。在這個平臺上你可以對你的設計從軟件層面上進行分析和校驗,這個就是testbench的含義。

簡單的Testbench設計

//timescale 仿真時間單位/時間精度(時間精度不能比時間單位還要大)

timescale 1ns/1ps

//定義一個無輸入無輸出的Moudle

module Led_clg_tst();

//被測設計的輸入信號,對應測試腳本的輸出信號(注意要定義成reg)

reg clk;

reg rst_n;

//被測設計的輸出信號,對應測試腳本的輸入信號(注意要定義成wire)

wire led;

//例化待測模塊

Led led_test

(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

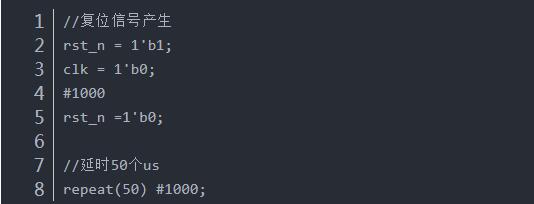

//使用Initail生成rst_n激勵

initial

begin

//監控Led信號變化

monitor(monitor(time,”led value= %b\n”,led);

end

//使用alwasys模擬產生25M的時鐘信號

always #20 clk = ~clk;

endmodule

-

設計

+關注

關注

4文章

818瀏覽量

69952

發布評論請先 登錄

相關推薦

編寫高效Testbench的指南和示例

簡單的Testbench設計

簡單的Testbench設計

評論