這兩天嵌入式領(lǐng)域最大新聞就是MIPS架構(gòu)宣布開(kāi)源了!昨天:曾經(jīng)收購(gòu)MIPS公司的美國(guó)AI公司W(wǎng)ave Computing宣布了一則重磅消息:正式啟動(dòng)MIPS Open項(xiàng)目,MIPS架構(gòu)完全開(kāi)源,免費(fèi)提供給全球的開(kāi)發(fā)者、合作伙伴、高校研究機(jī)構(gòu)、客戶。

MIPS開(kāi)源社區(qū)將在2019年第一季度上線,屆時(shí)會(huì)免費(fèi)提供的MIPS IP和技術(shù)資源包括:32/64位指令集Releas 6版本、SIMD擴(kuò)展、DSP擴(kuò)展、MT多線程、MCU微控制器、VZ虛擬化、microMIPS架構(gòu)。

未來(lái),任何人都可以自由獲得以上資源,無(wú)需任何授權(quán)費(fèi)、版權(quán)費(fèi),并能在全球范圍內(nèi)得到幾百項(xiàng)專利的保護(hù)。Wave Computing表示,更多的開(kāi)源計(jì)劃細(xì)節(jié)將在明年第一季度公布。

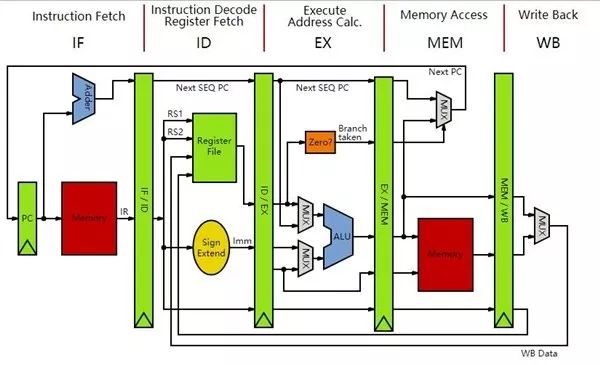

MIPS架構(gòu)流水線簡(jiǎn)圖

雖然之前的授權(quán)和新的開(kāi)源計(jì)劃并不能完全混合,但是Wave Comuting已經(jīng)明確表示,會(huì)向授權(quán)客戶提供開(kāi)發(fā)工具、第三方IP資源,以構(gòu)建更強(qiáng)壯、更完整的生態(tài)系統(tǒng),再加上開(kāi)源的豐富資源和全世界的努力。

01

MIPS指令集歷史沿革

此次開(kāi)源的是 MIPS 32/64位指令集Releas 6版本,MIPS指令集架構(gòu)自上世紀(jì)80年代出現(xiàn)已經(jīng)有35年歷史了,其指令集一直在更新?lián)Q代,從最初的MIPS I到MIPS V,發(fā)展到可支持?jǐn)U展模塊的MIPS32、MIPS64系列,再到集成代碼壓縮技術(shù)的microMIPS32、microMIPS64。每一個(gè)MIPS ISA都是其前一個(gè)的超集,沒(méi)有不論什么遺漏,僅僅有添加新的功能。

1、MIPS Ⅰ

提供載入/存儲(chǔ)、計(jì)算、跳轉(zhuǎn)、分支、協(xié)處理及其他特殊指令。該指令集架構(gòu)用于最初的MIPS處理器R2000/R3000。R2000是1985年推出的首款MIPS CPU,由110000個(gè)晶體管組成,是一個(gè)8MHz的32位處理器。R3000是R2000的下一代產(chǎn)品。與前者相比不過(guò)時(shí)鐘頻率不同。

2、MIPS Ⅱ

添加了自陷指令、鏈接載入指令、條件存儲(chǔ)指令、同步指令、可能分支指令、平方根指令。最初計(jì)劃用在MIPS 處理器R6000上,但因?yàn)楣に囘x擇的問(wèn)題,R6000從1988年開(kāi)始設(shè)計(jì)后,就一直問(wèn)題不斷,終于未能大規(guī)模生產(chǎn)。但MIPSⅡ指令集架構(gòu)是后期MIPS32指令集架構(gòu)的直接先驅(qū)。

3、MIPS Ⅲ

提供了32位指令集,同一時(shí)候支持64位指令集。最初用于MIPS處理器R4000。R4000是于1991年推出的64位處理器,首次增加了浮點(diǎn)處理器單元,主時(shí)鐘頻率提高到了100MHz。后來(lái)出現(xiàn)了一系列的R4000處理器。

4、MIPS Ⅳ

在MIPS III基礎(chǔ)上添加了條件移動(dòng)指令、預(yù)取指令以及一些浮點(diǎn)指令。最初用于MIPS處理器R8000,后來(lái)應(yīng)用于R5000/R10000。R5000與R10000盡管使用同樣的指令集架構(gòu)。可是兩者微架構(gòu)的設(shè)計(jì)理念全然不同。R5000于1995年推出。採(cǎi)用的是經(jīng)典的五級(jí)流水線、順序運(yùn)行。R10000于1996年推出,採(cǎi)用的是亂序運(yùn)行。

MIPS IV是該架構(gòu)的第四個(gè)版本。它是MIPS III的超集,與所有現(xiàn)有版本的MIPS兼容。 MIPS IV旨在主要改善浮點(diǎn)(FP)性能。為了改善對(duì)操作數(shù)的訪問(wèn),添加了用于FP加載和存儲(chǔ)的索引尋址模式(base + index,均來(lái)自GPR),以及用于執(zhí)行內(nèi)存預(yù)取和指定緩存提示的預(yù)取指令(這些指令支持基數(shù)+偏移量和基數(shù)) +索引尋址模式)。

MIPS IV增加了幾個(gè)功能來(lái)改善指令級(jí)并行性。為了緩解由單個(gè)條件位引起的瓶頸,將七個(gè)條件碼位添加到浮點(diǎn)控制和狀態(tài)寄存器,使總數(shù)達(dá)到8。重新定義FP比較和分支指令,以便它們可以指定分別寫入或讀取哪個(gè)條件位;并且去除了讀取通過(guò)先前FP比較寫入的條件位的FP分支之間的延遲時(shí)隙。對(duì)GPR和FPR的條件移動(dòng)指令形式增加了對(duì)部分預(yù)測(cè)的支持;并且實(shí)現(xiàn)可以選擇具有IEEE 754陷阱的精確或不精確的異常。

MIPS IV為單精度和雙精度FPN添加了幾個(gè)新的FP算術(shù)指令:融合乘法加法或減法,倒數(shù)和倒數(shù)平方根。 FP融合乘法加或減指令執(zhí)行一個(gè)或兩個(gè)舍入(它是實(shí)現(xiàn)定義的),以超過(guò)或滿足IEEE 754精度要求(分別)。 FP倒數(shù)和倒數(shù)平方根指令不符合IEEE 754精度要求,并且產(chǎn)生的結(jié)果與最后一個(gè)位置的一個(gè)或兩個(gè)單位(所實(shí)現(xiàn)定義)的要求精度不同。這些指令適用于指令延遲比準(zhǔn)確性更重要的應(yīng)用。

第一個(gè)MIPS IV實(shí)施是MIPS科技R8000微處理器芯片組(1994)。 R8000的設(shè)計(jì)始于Silicon Graphics,Inc。,它僅用于高端工作站和服務(wù)器,用于科學(xué)和技術(shù)應(yīng)用,其中大型浮點(diǎn)工作負(fù)載的高性能非常重要。后來(lái)的實(shí)施是MIPS Technologies R10000(1996)和Quantum Effect Devices R5000(1996)和RM7000(1998)。由NEC電子和東芝制造和銷售的R10000及其衍生產(chǎn)品被NEC,Pyramid Technology,Silicon Graphics,Inc。和Tandem Computers(以及其他公司)用于工作站,服務(wù)器和超級(jí)計(jì)算機(jī)。 R5000和R7000可用于高端嵌入式系統(tǒng),個(gè)人計(jì)算機(jī)以及低端工作站和服務(wù)器。東芝R5000的衍生產(chǎn)品R5900用于索尼電腦娛樂(lè)公司的Emotion Engine,后者為其PlayStation 2游戲機(jī)提供動(dòng)力。

5、MIPS Ⅴ

在MIPS IV的基礎(chǔ)上添加了能夠提高代碼生產(chǎn)效率和數(shù)據(jù)轉(zhuǎn)移效率的指令。可是沒(méi)有不論什么一個(gè)處理器基于該架構(gòu)。MIPS V指令集架構(gòu)是后期MIPS64指令集架構(gòu)的直接先驅(qū)。

6、MIPS32/64

MIPS32/64于1998年提出,MIPS32以MIPS II架構(gòu)為基礎(chǔ),選擇性地增加了MIPS III、MIPS IV、MIPS V,提高了代碼生成和數(shù)據(jù)移動(dòng)的效率。

MIPS64以MIPS V架構(gòu)為基礎(chǔ),同一時(shí)候兼容MIPS32。

該架構(gòu)第一次包括了被稱為協(xié)處理器0的“CPU控制”功能。1999年以后設(shè)計(jì)的大多數(shù)MIPS處理器都與該標(biāo)準(zhǔn)兼容。2003年。公布了MIPS32/64指令集架構(gòu)的第二版(Release 2),也稱為MIPS32/64 R2。最新的是第六版(Release 6),也稱為MIPS32/64R6。

而廣泛使用的是第二版。很成功的MIPS 4K、24K系列處理器遵循的就是MIPS32 R2架構(gòu)。MIPS32/64在基本指令的基礎(chǔ)上,還提供了一些面向特定應(yīng)用的指令。這些指令採(cǎi)用特定應(yīng)用擴(kuò)展(ASE:Application-SpecificExtensions)的形式。

一種處理器是否實(shí)現(xiàn)了某種擴(kuò)展。能夠通過(guò)設(shè)置標(biāo)準(zhǔn)的配置寄存器指明。基本的擴(kuò)展列舉例如以下。

MIPS 16e:是專門為嵌入式系統(tǒng)及存儲(chǔ)空間有限情況下的應(yīng)用而設(shè)計(jì)的,能夠在一個(gè)程序中運(yùn)行16位和32位兩種混合長(zhǎng)度的指令,能使終于代碼長(zhǎng)度降低40%。MIPS32、MIPS64都支持MIPS 16e。

SmartMIPS:是為了滿足智能卡和靈活小系統(tǒng)的市場(chǎng)須要而設(shè)計(jì)的。是一套能高效節(jié)省存儲(chǔ)空間的擴(kuò)展指令集,此外還能提高智能卡領(lǐng)域很關(guān)鍵的加密運(yùn)算的性能。MIPS32支持SmartMIPS。

MIPS-3D:提供了更好的幾何運(yùn)算處理,具有成對(duì)單精度數(shù)據(jù)類型,還提供專用指令來(lái)加快對(duì)該類型數(shù)據(jù)的處理。MIPS64支持MIPS-3D, MIPS32第二版也支持MIPS-3D。

MCU:Micro-Control Unit微控制單元,增強(qiáng)了內(nèi)存映射I/O的處理、提供了更低的中斷延遲。MIPS32、MIPS64都支持MCU。

7、microMIPS32/64

microMIPS32/64指令集架構(gòu)集成了16位和32位優(yōu)化指令的高性能代碼壓縮技術(shù),保持了98%的MIPS32性能,同一時(shí)候減少了至少30%的代碼體積,從而減少芯片成本,也有助于減少系統(tǒng)功耗。MIPS M14K內(nèi)核是MIPS科技于2009年公布的首款遵循microMIPS指令集架構(gòu)的MIPS32兼容內(nèi)核。

注意其序列中沒(méi)有Release 4,這是由于對(duì)于非常多人來(lái)說(shuō)。4是個(gè)不吉利的數(shù)字。所以MIPS沒(méi)有公布Release 4,而是直接公布Release 5。

MIPS32 / MIPS64R6

2014年MIPS32 / MIPS64第6版增加了以下內(nèi)容:

一個(gè)沒(méi)有延遲槽的新分支系列:

具有26位偏移的無(wú)條件分支(BC)和分支鏈接(BALC),

具有21位偏移的零/非零條件分支,

兩組寄存器(例如BGTUC)或零寄存器(例如BGTZC)之間的全套有符號(hào)和無(wú)符號(hào)條件分支比較,

全套分支和鏈接,將寄存器與零進(jìn)行比較(例如BGTZALC)。

索引跳轉(zhuǎn)指令沒(méi)有延遲槽,旨在支持大的絕對(duì)地址。

指令在位位置16,32或48處加載16位立即數(shù),允許輕松生成大常量。

PC相對(duì)負(fù)載指令,以及具有大(PC相對(duì))偏移的地址生成。

位反轉(zhuǎn)和字節(jié)對(duì)齊指令(以前僅適用于DSP擴(kuò)展)。

乘法和除法指令重新定義,以便他們使用單個(gè)寄存器作為結(jié)果)。

生成真值的指令現(xiàn)在生成全零或全1,而不是僅清除/設(shè)置0位,

使用真值的指令現(xiàn)在只將全零解釋為假而不是僅僅查看0位。

刪除了不經(jīng)常使用的說(shuō)明:

一些有條件的舉動(dòng)

分支可能的指令(在以前的版本中已棄用)。

16位立即數(shù)的整數(shù)溢出陷阱指令

整數(shù)累加器指令(一起HI / LO寄存器,移動(dòng)到DSP應(yīng)用專用擴(kuò)展)

未對(duì)齊的加載指令(LWL和LWR),(要求大多數(shù)普通的加載和存儲(chǔ)支持未對(duì)齊的訪問(wèn),可能通過(guò)陷阱和添加新指令(BALIGN))

重新組織指令編碼,為將來(lái)的擴(kuò)展釋放空間。

02

MIPS CPU架構(gòu)開(kāi)源打擊了誰(shuí)?

在業(yè)界,雖然MIPS架構(gòu)的生態(tài)系統(tǒng)成熟度比不過(guò)ARM,但超過(guò)RISC-V是綽綽有余了,作為一種全新的、簡(jiǎn)且開(kāi)源的指令集架構(gòu),RISC-V 因開(kāi)源且沒(méi)有版稅而被眾多企業(yè)、研究機(jī)構(gòu)所采納,2018堪稱RISC-V爆發(fā)的元年,各種有關(guān)RISC-V的研討會(huì)不斷,同時(shí),中國(guó)RISC-V產(chǎn)業(yè)聯(lián)盟也宣告成立,為RISC-V在中國(guó)的全面應(yīng)用打下了基礎(chǔ)。

SiFive CEO NaveedSherwani在近日ICCAD2018上接受采訪時(shí)表示RISC-V生態(tài)趨于成熟和完善,并透露許多半導(dǎo)體廠家發(fā)布了產(chǎn)品或者宣布了產(chǎn)品推出的計(jì)劃,比如西部數(shù)據(jù),高通,英偉達(dá),F(xiàn)ADU,以及國(guó)內(nèi)的華米,比特大陸,嘉楠耘智等。Naveed Sherwani還指出今年10月份微軟就只花費(fèi)兩個(gè)月時(shí)間便開(kāi)發(fā)出了一款芯片,未來(lái)幾年RISC-V的發(fā)展將會(huì)不斷的提速,將有更多的公司更快地發(fā)布他們的芯片。詳見(jiàn)《目前形勢(shì)下本土IC該如何做強(qiáng)做大?》但即便如此,RISC-V的IP積累還是不夠。

另外,可能大家對(duì)RISC-V的free有點(diǎn)誤解,其實(shí)這里的free不是免費(fèi)是自由的意思,對(duì)于RISC-V指令集,如果你是個(gè)人或者科研機(jī)構(gòu)可以下載其源代碼用于研究,如果要進(jìn)行商業(yè)化操作比如大批量的量產(chǎn),這就需要SiFive的授權(quán)了,只是RISC-V指令集的授權(quán)費(fèi)要比ARM低很多而起不收芯片版稅。所以RISC-V并不是一個(gè)完全免費(fèi)的指令集。

還有,有本土IC設(shè)計(jì)公司老大提出了不同意見(jiàn),他認(rèn)為縱觀CPU技術(shù)發(fā)展歷史任何一款CPU的走熱或者存在都是因?yàn)橐源罅繎?yīng)用為基礎(chǔ) ,對(duì)于RISC-V 目前至今還未看到有爆量的單一產(chǎn)品出現(xiàn),另外,RISC-V雖然免費(fèi)降低了IC開(kāi)發(fā)者的難度,提升了最終系統(tǒng)開(kāi)發(fā)者的難度,而一些商用CPU已經(jīng)很好的開(kāi)發(fā)基礎(chǔ)和生態(tài),例如X86只要簡(jiǎn)單的編程就可以開(kāi)發(fā)應(yīng)用,對(duì)此,RISC-V還沒(méi)有形成自己的成熟的開(kāi)發(fā)環(huán)境,如果單純讓應(yīng)用端的開(kāi)發(fā)人員去買單花時(shí)間去學(xué)習(xí)開(kāi)發(fā)這不符合商業(yè)規(guī)律。

他認(rèn)為應(yīng)用的碎片化不能代表參與者的碎片化,對(duì)于很多中小公司來(lái)說(shuō)如果盲目跟進(jìn)RISC-V則可能遭遇很大風(fēng)險(xiǎn),他算了一筆賬一款芯片從定義到應(yīng)用走量至少5年時(shí)間,如果一個(gè)20人的團(tuán)隊(duì)要開(kāi)發(fā)一款RISC-V應(yīng)用則至少需要投入近一個(gè)億的資金,“誰(shuí)愿意一次性給你一個(gè)億讓你來(lái)燒?”他表示。所以他認(rèn)為RISC-V最終是一場(chǎng)開(kāi)源鬧劇,不看好其未來(lái)。詳見(jiàn)《RISC-V是振興中國(guó)芯CPU的一劑良藥嗎?》

而現(xiàn)在隨著MIPS宣布開(kāi)源,ARM Cortex-M0免費(fèi)(1000顆以內(nèi)免費(fèi)),RISC-V的生存環(huán)境可能遭遇進(jìn)一步擠壓,所以有業(yè)者戲稱:“RISC-V使命完成了。”大家咋么看?

-

微控制器

+關(guān)注

關(guān)注

48文章

7649瀏覽量

152107 -

cpu

+關(guān)注

關(guān)注

68文章

10902瀏覽量

213007 -

mips

+關(guān)注

關(guān)注

1文章

239瀏覽量

47853

原文標(biāo)題:MIPS CPU架構(gòu)宣布開(kāi)源,RISC-V使命完成了?

文章出處:【微信號(hào):mcuworld,微信公眾號(hào):嵌入式資訊精選】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

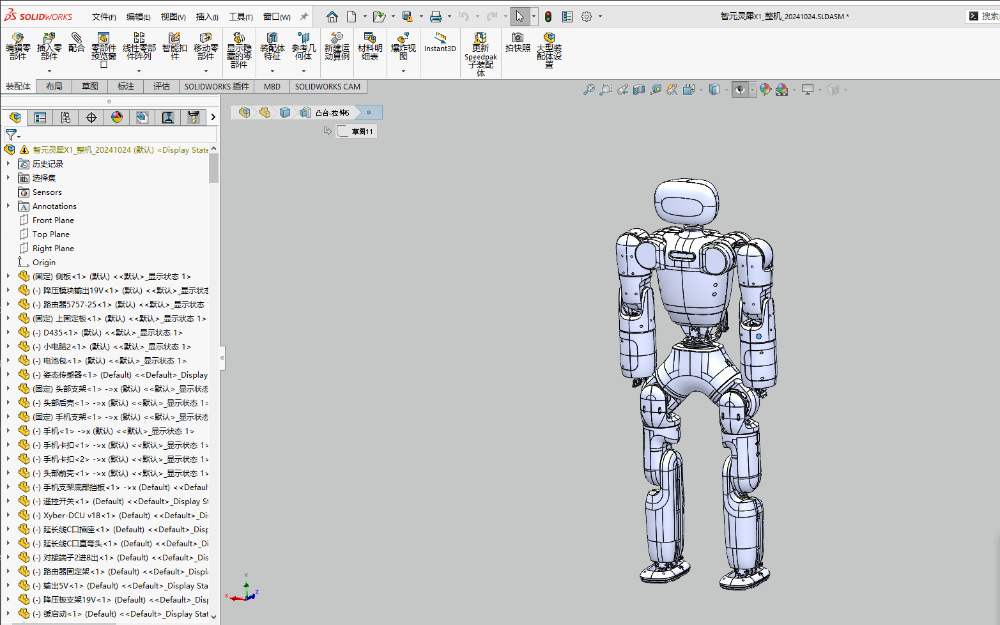

圖紙代碼完全開(kāi)源!稚暉君:人人都能造人形機(jī)器人!

芯科科技Z-Wave設(shè)備測(cè)試工具介紹

一則消息引爆激光雷達(dá)行業(yè)!特斯拉竟然在自研激光雷達(dá)?

開(kāi)源鴻蒙應(yīng)用案例重磅發(fā)布

Z-Wave無(wú)線協(xié)議的特性和優(yōu)勢(shì)

你聽(tīng)說(shuō)過(guò)MIPS嗎?它和ARM有何區(qū)別?

Wave Computing宣布了一則重磅消息:正式啟動(dòng)MIPS Open項(xiàng)目,MIPS架構(gòu)完全開(kāi)源

Wave Computing宣布了一則重磅消息:正式啟動(dòng)MIPS Open項(xiàng)目,MIPS架構(gòu)完全開(kāi)源

評(píng)論