項(xiàng)目的設(shè)計(jì)初期,我們需要選型FPGA后進(jìn)行FPGA原理圖設(shè)計(jì),F(xiàn)PGA的原理圖設(shè)計(jì)和單片機(jī)的原理圖設(shè)計(jì)有很大的區(qū)別:?jiǎn)纹瑱C(jī)的外設(shè)是固定的引腳,我們只需要根據(jù)數(shù)據(jù)手冊(cè)確定各個(gè)外設(shè)的引腳就行,但是,F(xiàn)PGA卻大不相同同,引腳外設(shè)既靈活又有很多約束條件,靈活是不同的UART/SPI等外設(shè)引腳的確定可以根據(jù)需求改變,很多約束條件指:配置引腳、時(shí)鐘等有很多約束條件。下面來(lái)介紹不是常規(guī)的通過(guò)大量單一的查閱數(shù)據(jù)手冊(cè)來(lái)初步進(jìn)行引腳分配,而是在Vivado中新建IO Planning工程來(lái)初步引腳分配,這樣會(huì)大大提高開(kāi)發(fā)效率,目前只在Vivado中發(fā)現(xiàn)此功能,現(xiàn)在分享給大家。

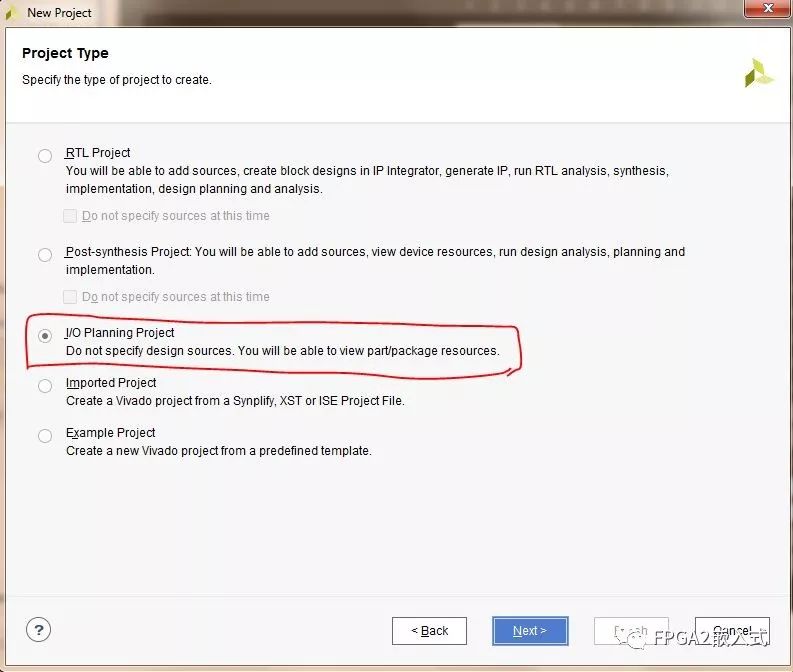

如上圖所示,打開(kāi)Vivado后,新建工程,選擇IO Planning工程,IO Planning工程不需要任何設(shè)計(jì)的源文件就可以查看FPGA的引腳資源。當(dāng)然,其它幾項(xiàng)就是新建RTL工程、導(dǎo)入以前的XST、ISE工程文件、新建例程工程。接下來(lái),就是:

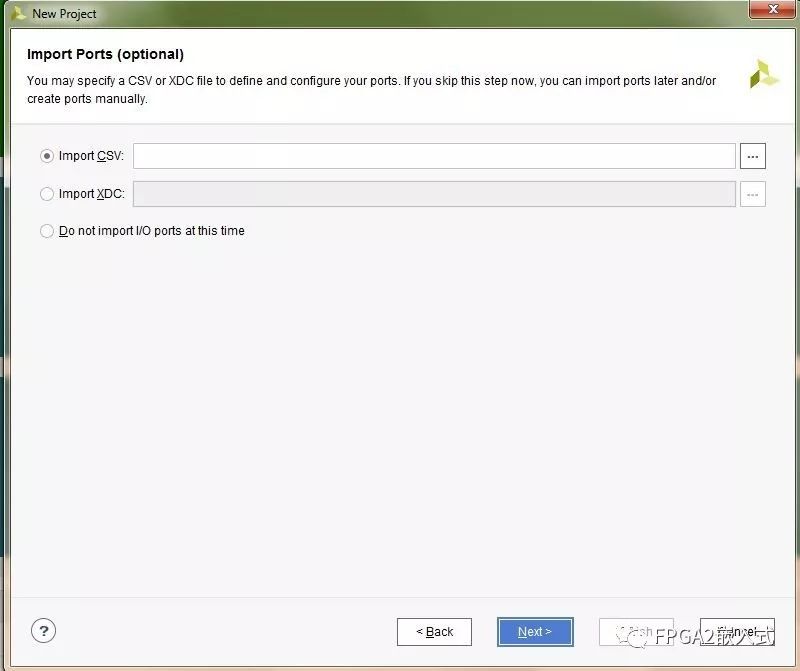

可選的導(dǎo)入IO分配文件,可以是CSV或XDC格式的文件,其中,CSV和XDC文件可以由Candance原理圖設(shè)計(jì)軟件直接導(dǎo)出后使用,如果你一直是手動(dòng)的編寫(xiě)CSV或XDC文件,那就太OUT了。接著,自然到了型號(hào)選擇了:

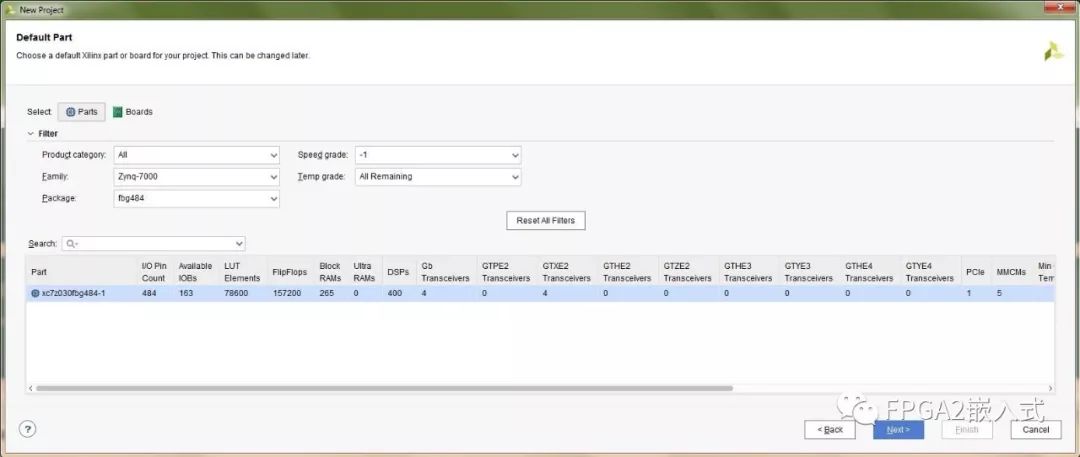

在這里,你可以選擇最右側(cè)的開(kāi)發(fā)板型號(hào),也可以選擇Part,具體的FPGA的型號(hào),選擇完后,我們可以很清晰的看到該型號(hào)的資源列表:包括IO數(shù)、可用的IO數(shù)、內(nèi)部BRAM大小、時(shí)鐘資源等。最終確定后,我們可以很直觀的看到FPGA的引腳視圖,如下圖:

下面,我們看看到這里,他有那些用處,查看不同屬性的引腳分配,指導(dǎo)PCB設(shè)計(jì),如下圖:只查看各個(gè)BANK及電源引腳的分布圖:

查看Transceiver Pins的分布圖:

專用的配置引腳分布圖:

通過(guò)右側(cè)的篩選框來(lái)篩選查看某類引腳分布圖。當(dāng)然除了這個(gè)功能,還可以根據(jù)導(dǎo)入的CSV或XDC文件來(lái)生成頂層文件來(lái)驗(yàn)證引腳分配的合理性,檢查DRC等:

同樣,可以手動(dòng)添加分配引腳,并查看差分對(duì)引腳情況。

總之,通過(guò)IO Planning工程可以很好的幫助我們?cè)O(shè)計(jì)原理圖、PCB和項(xiàng)目選型評(píng)估.

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606065 -

引腳

+關(guān)注

關(guān)注

16文章

1220瀏覽量

50913 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66897

原文標(biāo)題:Vivado中新建 IO Planning工程初步引腳分配

文章出處:【微信號(hào):fpga234,微信公眾號(hào):fpga234】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

在Vivado中新建IO Planning工程來(lái)初步引腳分配

在Vivado中新建IO Planning工程來(lái)初步引腳分配

評(píng)論