引 言

SoPC可編程片上系統是一種特殊的嵌入式微處理器系統。首先,它是片上系統(SoC),即由單個芯片完成整個系統的主要邏輯功能;其次,它是可編程系統,以FPGA為硬件基礎,具有靈活的設計方式,可裁減、可擴充、可升級,并具備軟硬件系統在線可編程的功能。

IP(Intellectual Property)知識產權是SoC設計中非常重要的內容。資源復用(IP Reuse)是指在集成電路設計過程中,通過繼承、共享或購買所需的部分或全部知識產權內核(IP Core)進行設計、綜合和驗證,從而加速流片設計過程的設計方法。IP技術包含兩個方面的內容:IP核的生成和IP核的重用。本設計中采用VHDL語言,構建一個功能強大的完整DDS模塊,并根據IBM CoreConnect總線連接規范,在DDS模塊外面添加OPB(On?chip Peripheral Bus)片上外設總線接口,封裝為自定義IP,添加到硬件系統中。

對于本設計來說,利用SoPC和IP的優勢是可以利用最少的元器件,創建一個易配置、易擴展、易修改并且易于繼承使用的集成系統。該系統的創建是基于Xilinx公司提供的嵌入式開發工具包EDK(Embedded Development Kit)來實現的。EDK自帶了MicroBlaze軟核和PowerPC硬核微處理器及大量免費IP,有利于構建簡易系統。針對MicroBlaze及PowerPC提供的C語言編譯器,可使系統的功能實現更加簡易。對基于MicroBlaze的系統,MicroBlaze通過OPB總線與外設IP及外部存儲器控制接口相連接,通過LMB(Local Memory Bus)總線與FPGA片上塊存儲器BRAM(Block RAM)相連接,還可以通過EMC(External Memory Control)等存儲器控制IP擴展片外RAM或ROM。

1 系統的架構

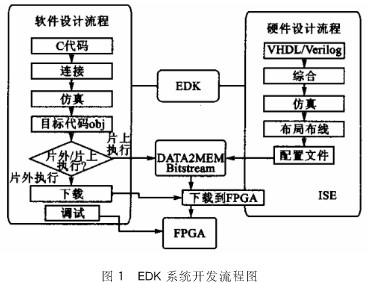

本設計采用SoPC可編程片上系統的思想,利用Xilinx的Spartan3系列XC3S400 FPGA,通過EDK開發工具包的集成開發環境XPS(Xilinx Platform Studio)完成了FPGA硬件系統設計及基于此硬件系統的軟件開發。圖1是基于EDK的系統開發設計流程圖,設計分為硬件設計和軟件設計兩部分。硬件設計符合基于HDL硬件描述語言的EDA開發流程,是根據硬件系統合理使用總線IP和外設IP,并為各個實例定義地址范圍以及輸出端口和時鐘,經過綜合及布線后形成硬件配置文件。軟件設計與傳統的嵌入式軟件開發設計類似,是在硬件設計的基礎上根據處理器所支持的指令集以及編譯環境編寫程序代碼,然后對代碼編譯燒寫及調試。

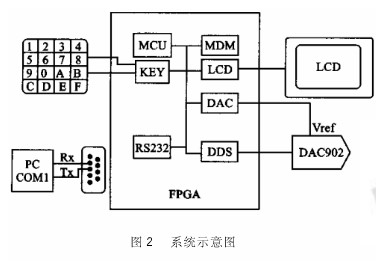

該設計通過FPGA實現所有數字部分。系統的示意圖如圖2所示。

在FPGA內部,以MicroBlaze為控制核心,以DDS IP為波形發生功能實現核心,同時加入了其他的IP核,諸如調試用的MDM(Microprocessor Debug Module),用于與PC進行通信的UART(Universal Asynchronous Receiver & Transmitter)通用異步傳輸模塊,以及LCD顯示和4×4按鍵控制模塊,實現了系統的高度集成。FPGA硬件系統為數字系統產生數字量,外圍電路加上高速數模轉換器件DAC902,把波形數據轉換為模擬波形,即實現了完整的可編程片上系統的波形發生器。

2 硬件系統的具體實現

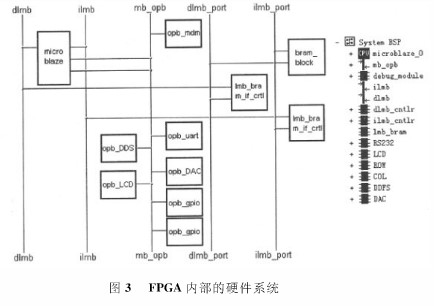

本設計以32位MicroBlaze軟核處理器為系統的核心部分,負責指令的執行。各種IP包括自主編寫的以及EDK自帶的,使用XPS下的ADD/Edit Cores工具,通過相應類型的總線連接到MicroBlaze上。其中UART、LCD、GPIO和自主編寫的DDS的IP都是通過OPB(On?chip Peripheral Bus)片上外設總線連接到處理器上的。程序存儲器RAM則是由FPGA內部的BRAM實現,并通過LMB(Local Memory Bus)本地存儲器總線與MicroBlaze相連接。自主編寫的IP與總線間的接口符合CoreConnect規范,實現了IP間的無縫結合,方便了數據的讀寫及時序控制。圖3給出了在FPGA內部由各種IP組合成的可編程硬件系統。

硬件系統所包含的器件如圖3右部分所示。Microblaze_0是該系統的CPU,其中的debug_module為調試模塊,dlmb_cntlr和 ilmb_cntlr為片上BRAM控制器。Lmb_bram為片上BRAM,它通過LMB總線與 BRAM控制器相連,接受CPU的讀寫訪問。DDFS是為實現DDS編寫的IP模塊。RS232為UART模塊,用于與其他設備的通信以及程序調試。LCD IP負責128×64點陣液晶的顯示控制。 COL和ROW是例化后的GPIO接口,用于連接4×4鍵盤。

2.1 MicroBlaze軟核處理器

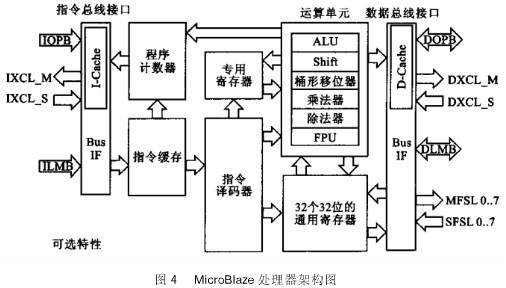

MicroBlaze是Xilinx提供的32位微處理器IP核,是哈佛結構的RISC微處理器,有較高的性能。它可以在性價比很高的SpartanIII系列FPGA上實現。EDK為其提供了MBGCC,支持C及C++語言。 MicroBlaze架構如圖4所示。

該處理器含有32個32位的通用寄存器,2個專用寄存器,獨立的32位數據和指令總線,并與IBM的OPB總線完全兼容,具有32位的指令寬度支持三個操作數和兩種尋址模式,以及可選的硬件乘除法及浮點運算單元。

2.2 DDS IP的實現

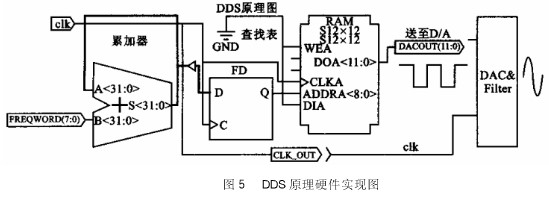

數字直接頻率合成技術(Direct Digital Frequency Synthesis,簡稱DDS或DDFS)的基本原理是利用采樣定理,通過查表法產生波

形,其基本電路原理如圖5所示。

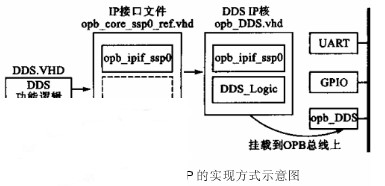

DDS的頻率及步進容易控制,且合成的頻率取決于累加器及查找表的速度,采用FPGA可以很好的發揮這項優勢,獲得精細的步進及寬頻帶。使用HDL硬件描述語言,可以很方便的描述出DDS的FPGA硬件實例。在基本的DDS模塊上,添加相應的控制寄存器,通過向不同的寄存器內寫入相應的控制字,實現頻率以及幅度的可控性。最后通過IBM CoreConnect技術,在DDS模塊外面添加總線接口,作為自定義IP,成功地將其掛載到系統總線上,便可以方便的對其進行讀寫操作,實現DDS模塊與MicroBlaze的通信。圖6是從用戶邏輯到成為符合IBM CoreConnect技術規范的DDS IP的實現過程。

DDS的VHDL代碼作為子模塊與opb_core_ssp0_ref.vhd模塊共同構成opb_DDS IP Core,其中ipif(IP InterFace )符合IBM CoreConnect規范,負責DDS邏輯與OPB總線之間的通信。在EDK中,通過Create/Import IP工具把opb_DDS添加到系統中,并為其分配地址,建立端口連接,之后就可以使用該IP了。DDS IP配合控制程序可產生各種波形,并對頻率、幅度進行精確的控制。

2.3 其余部分

系統所需要的LCD顯示、DAC控制等模塊,均通過與生成DDS IP相同的方式,編寫為符合IBM CoreConnect總線規范的IP,以供使用。

在硬件系統構建完畢之后,使用Platgen工具生成網表文件和Bitgen工具生成相應的硬件配置文件。若將工程導入到ISE軟件中,可以進行優化設置,還可以將工程導入到其他的綜合工具如Synplify Pro進行實現。IP核的編寫是在ISE中完成的。無論對于整個系統還是一個單獨的IP,都可以利用Modelsim工具進行行為及時序仿真。最后,為此系統描寫XBD(Xilinx Board Description)板級描述文件,通過此文件,EDK可以通過BSB(Base System Builder)模式自動生成基本的硬件系統,并對所添加的端口進行約束,這樣可以實現資源的繼承性使用。

3 軟件系統的實現

EDK提供了免費的GNU C Compiler,可以支持標準C。同時,EDK為多種IP以API的形式提供了驅動函數,有利于程序的開發。XPS所集成的軟件工程管理工具允許在一個硬件平臺上同時開發多個軟件工程。完成軟件代碼的編寫后,使用EDK集成的XMD和GDB調試器對代碼進行仿真和調試,也可以配合ChipScope(片內邏輯分析儀)進行硬件及軟件的協同調試。XMD通過MDM模塊和JTAG口連接目標板上的CPU,GDB可以對程序進行單步調試或斷點設置。針對本設計及應用,編寫了系統控制及液晶顯示程序。程序編譯后生成為elf文件,通過Update bitstream工具把程序同硬件配置文件合成為Download.bit文件,把此文件下載到目標板后,FPGA首先根據硬件配置信息建立硬件系統,并把程序代碼映射到片內BRAM中,最后啟動MicroBlaze,運行程序。

4 總結

本系統基于FPGA,以MicroBlaze為核心,加入具有良好特性的DDS IP,并輔以必要的外圍電路,構成了高度集成化的系統。另外,SoPC系統的柔性配置,使得可以基于此系統擴展片外存儲器,并可以實現RTOS操作系統的移植,以實現更豐富的功能和完成更復雜的任務。

-

集成電路

+關注

關注

5392文章

11622瀏覽量

363174 -

操作系統

+關注

關注

37文章

6892瀏覽量

123742 -

波形發生器

+關注

關注

3文章

293瀏覽量

31431

發布評論請先 登錄

相關推薦

手機應用中的可編程片上系統器件

MicroBlaze處理器的PetaLinux操作系統怎么移植?

可編程SoC(SoPC),什么是可編程SoC(SoPC)

基于片上可編程系統解決方案實現視頻編解碼IP核的設計

在SoPC可編程片上系統上實現RTOS操作系統的移植

在SoPC可編程片上系統上實現RTOS操作系統的移植

評論