多采樣率技術已廣泛應用于很多領域。在一個信號處理系統中,在不同的地方使用不同的采樣率有利于信號的存儲、傳輸和處理。例如在數字通信中,網絡的不同部分可能需要不同的編碼格式,在這些編碼格式的轉化過程中,往往涉及到基本的采樣率變換。

FPGA是實現數字信號處理的一種高效手段。在實現高帶寬信號處理領域,FPGA技術可以通過一個芯片上的多級運算單元來獲得比通用DSP芯片更高的運算速度[2]。由于采樣率變換能用一種并行的方法實現,使用FPGA來實現就可以利用其硬件本身的并行性得到較高的效率。

1 有理數采樣率變換器的原理

從概念上講,采樣率變換器可以通過數/模轉換,再對模擬信號進行給定頻率的模/數轉換得到。在實際的系統中,通過在數字域利用抽取和內插運算實現是一種更為合理和有效的手段。

抽取是降低采樣率的方法。在時域上,D倍(D為抽取因子)抽取就是從原始序列中每隔D-1個樣點取出一個構成新的數字序列。在頻域上,這一運算可以看成是頻譜的壓縮, 即原來以Ω sat1為周期的頻譜變為以Ω sat2為周期的頻譜。為避免可能引起的混迭失真,抽取前應使原信號通過一個低通濾波器。其抽取的示意圖及實現框圖如圖1所示。

內插是提高采樣率的方法。實際的內插系統由兩部分構成:(1)零值插值器。設插值因子為I, I倍零值內插就是在原始序列任意兩個樣本間加入I-1個零值樣本。在頻域上,頻譜進行了擴張,即原來以Ω sat1為周期的頻譜變為以Ω sat2為周期的頻譜。從Ω c到Ω sat2-Ω c的頻帶被稱為鏡像頻譜。(2)低通濾波器。信號經過此濾波器后,鏡像頻譜被濾去,從而得到采樣率提高的信號序列。內插圖示及實現框圖如圖2所示。

利用抽取系統和內插系統的級連,就可以得到有理數采樣率轉換器的基本方案。一般地,對于 I/D 倍數的有理數采樣變換,通過先內插后抽取的方法,可以得到如圖3所示的實現框圖。圖3(a)中的第二部分和第三部分是兩個低通濾波器的級連,因而總的濾波效果等效為通帶邊緣較低的低通濾波器,合并后得到框圖3(b)。

然而,對于上述三個系統,利用原始框圖直接實現并不是一個很好的方案。如從圖3可以看出,該系統最主要的運算量在濾波器的實現部分,圖3(b)中濾波器的采樣率為 F3=I,F1=DF2, 濾波運算是在最高采樣率的部分實現的,這是不經濟的。換一種說法,比如對后兩級的系統,經濾波后的序列每D個樣本中僅有一個是實際需要的,而D-1樣本的運算被丟棄了。

2 FIR濾波器的多相分解與多采樣率系統網絡變換

利用FIR濾波器的多相分解[1~2]及多采樣率系統網絡結構的變換[1],可以得到降低了運算代價的采樣率變換器的多相結構。

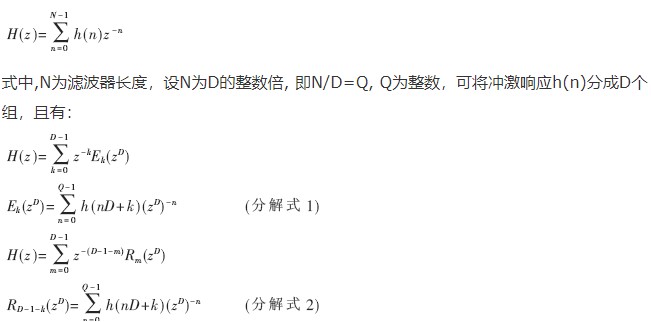

FIR濾波器的多相分解是指將數字濾波器H(z)可分解為若干個不同的組。設H(z)的轉移函數為:

對于多采樣率網絡,存在下面幾個等效變換:

T1: 抽取與乘常數可以換位。

T2: 零值插值和乘常數可以換位。

T3:兩個信號先分別抽取然后相加,以及先相加然后抽取等效。

T4:抽樣率相同的兩個信號先分別零值內插(內插因子相等)然后相加,以及先相加然后零值內插等效。

T5:如果I和D 互質,則抽取與內插可以交換。

此外,Nobel關系式[3]給出了抽取/內插與濾波器級連時如圖4所示的等效變換。

Nobel 關系式的意義在于:在抽取與濾波級連時,首先進行抽取運算,可以把濾波器的長度降低一個D因子; 內插與濾波級連時,首先進行濾波運算,可以使濾波器的的長度降低一個I因子。

3 采樣率變換器的多相表示結構

通過對圖1中的整數倍速抽取器系統進行多相分解(分解式1),然后依次進行T3及Nobel變換(抽取),可以得到抽取系統的多相結構。此結構中濾波器將在F2=F1/D的采樣率下進行,也就是說,對于給定的芯片和濾波器結構,濾波器能達到最高時鐘頻率相同時,該結構能處理的帶寬是圖1的D倍,或者說對相同采樣率的數據,該結構對濾波器最高時鐘頻率的要求降低為原來的1/D,因而是一種高效的實現方式。

類似地,對圖2中的整數內插系統進行多相分解(分解式2),并依次進行T4及Nobel變換(零內插),以得到整數內插的多相結構,通過變換,將以F1=F2/I的采樣率進行濾波運算。

分數倍采樣率轉換器的多相結構有多種實現方案。

(1)如果I與D不互質,可以利用已經得到的多相結構,然后與抽取或內插級連實現。如圖3(b)中可以把前兩部分用圖5的多相結構實現或把后兩部分用圖6的多相結構實現,具體選擇時可參考D與I的數值。

(2)如果I與D互質,則可以轉化為更為高效的多相結構[1,4]。圖7即是I、D互質時的一種高效結構。這一結構的推導利用了多相分解的分解式1和分解式2、T1~T5以及兩數互質時的歐幾里德公式(若I、D互質,則存在整數p、q,使得pI+qD=1)。這樣的結構不是唯一的,通過多采樣率系統的網絡變換,還可以得到其他的結構。在此結構中,濾波器運算是在F4的采樣率中進行的,且有F4=F1/D=F2/I,與最初的形式相比,濾波器的最高時鐘頻率相同時,處理帶寬增大為原來的I×D倍。

該多相結構中的Rm,n(z4)可以由原始濾波器經過兩次多相分解而求得。特殊地,如果有濾波器的級數N=DI,則 Rm,n(z4)=h[(n+1)I-(m+1)T3],為原始濾波器某一項的系數。

4 FPGA設計與驗證

由于整數倍抽取和內插的實現過程可以包含在分數采樣率變換器的實現過程中,因此下面只討論I、D互質的有理數采樣率變換器的實現。

根據圖7的多相結構,對于I、D互質的分數抽樣率轉化系統,可以分解為四個模塊:

(1)輸入與延時鏈模塊。這部分的時鐘周期應該為T1。

(2)R0~RI-1的延時與抽取模塊。注意:抽取器只是在第0,D,……,N×D個時鐘周期讓信號通過,其他時鐘周期阻隔信號。若已知延時與抽取鏈的功能,則可用一個如圖8(a)所示的多相選擇開關來實現,而圖8(b)給出了該電路的一種實現方案,其中TClk_T4 =DTclk_T1,T4為模塊3的時鐘周期。

(3)本系統最為關鍵的部分是第三部分。該部分是運算的主體部分,對整個系統的資源利用率和時鐘性能有很大的影響。該模塊需要實現的是I×D個FIR濾波器。對于給定的設計,這些濾波器的系數是常數,可由如下方法得到:

①根據低通濾波器的要求,用Matlab的FDAtool計算出濾波器的系數,并使其階數N=M×I×D,M為正整數,可根據濾波器的需要選取。

②利用多相分解公式計算每個濾波器的系數。

③把所得到的數字進行定點化處理(比如系數同乘以2 048,取整,待計算出結果后右移11位)。

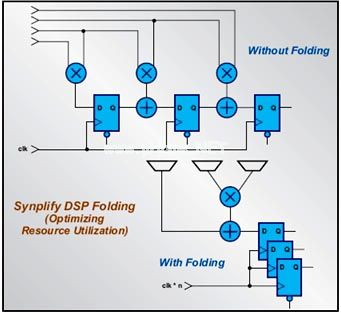

對于常系數的FIR濾波器,在FPGA實現時,有多種可以選擇的方式以降低復雜性。在本設計中,采用簡化的加法器圖[3]來實現,避免了使用資源代價較大的通用乘法器,同時提高了系統的整體性能。例如,在測試系統的設計中,需要計算132×x(n)、28×x(n-1)、126×x(n-2)、13×x(n-3),用圖9方案來實現時,將比用四個通用乘法器節省更多的LE資源,并且使最高的時鐘頻率得到了提高。表1給出了一個測試系統的資源與性能對比(使用了Altera公司的EP1C3T144C6芯片及Quartus II 5.1版本進行綜合)。

(4)第四部分是與第二部分類似的模塊。零內插器的特點是某個時鐘周期有用信號通過,其余時鐘周期通過零值,因而內插與延時相加模塊也可用一個多相選擇開關來實現。內插與延時相加模塊實現電路圖如圖10所示。

圖11給出了一個D=3、I=4、N為12時的分數采樣率變換的部分仿真結果(Modelsim 6.1)。其中,濾波器系數定點化為12位補碼,輸入、輸出數據為12位補碼整數, 測試輸入序列為20kHz的正弦波波形序列,采樣率為600kHz,輸出為800kHz采樣的正弦波序列。通過把輸入輸出序列保存并做FFT變換,可以得到兩者的實際頻率相同的結論。

利用FIR濾波器的多相分解及多采樣率網絡變換技術,本文介紹了一種有理數采樣率變換器的高效多相結構,并結合FPGA芯片的結構進行了實現與優化。文中的一些方法也適用于其他多采速率系統的設計。

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606065 -

濾波器

+關注

關注

161文章

7862瀏覽量

178948 -

變換器

+關注

關注

17文章

2109瀏覽量

109557

發布評論請先 登錄

相關推薦

矩陣變換器空間矢量調制策略的FPGA實現

在FPGA中轉換音頻采樣率

用FPGA實現音頻采樣率的轉換

多相結構采樣率變換器的FPGA實現

什么叫采樣率 數字信號處理時鐘與采樣率的關系

通過FPGA芯片實現對高效多相結構的采樣率變換器進行優化

通過FPGA芯片實現對高效多相結構的采樣率變換器進行優化

評論