慢門限恒虛警處理是一種對接收機內部噪聲電平進行恒虛警處理的電路,內部噪聲隨著溫度、電源等因素的改變而改變,這種變化是緩慢的,所以針對內部噪聲的處理稱為慢門限恒虛警處理。通過對雷達信號的慢門限處理降低了虛警概率,為后處理提供了必要條件。

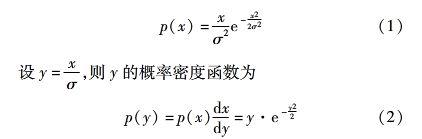

利用大規(guī)模可編程電路來實現(xiàn)慢門限恒虛警處理,具有方便、可靠的特點,可以方便地修改和仿真。雷達工作期,接收機輸出除噪聲外還有信號和地物雜波等,所以對噪聲的采樣應在休止期進行。接收機檢測器后噪聲電壓的概率密度函數(shù)服從瑞利分布

由式(2)可得出,P(y)與σ無關,如果能將變量x歸一化為變量y,則噪聲強度σ變化時將保持輸出恒虛警;恒虛警處理裝置就是設法檢測出噪聲x的均方差σ值,再算出值;這個過程稱為歸一化,歸一化的結果就達到了恒虛警的目的。

用數(shù)字電路實現(xiàn)除法運算比較復雜,故采用取對數(shù)的方法,將除法運算轉化為減法運算,簡化了電路實現(xiàn)

1 工作原理

在休止期對噪聲值lgx采樣,得到lgσ。取雷達工作期的lgx減去lgσ,算出lgy式(3),完成了歸一化處理。設計中慢門限恒虛警處理電路是采用開環(huán)式噪聲電平恒定電路,省略了反對數(shù)電路,增加了部分檢測電路,原理如圖1所示。

2 FPGA設計

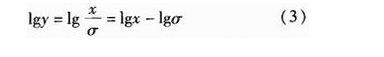

在休止期選8位I/Q信號幅度值進行累加,并對累加值進行鎖存,當累加128個單元后,取出平均值并鎖存作為第一門限值。在工作期選取8位I/Q信號幅度值一方面與噪聲平均值比較,另一方面減去噪聲平均值再與人工門限比較,如果兩次比較都為大于,則輸出1 bit過門限信號。人工門限值的選定要根據(jù)虛警率確定,如果虛警點多則調高門限值,反之降低門限,保持一定的虛警點數(shù)。

電路總框圖如圖2所示,包括3個子模塊分別為時序產生模塊、求噪聲平均值模塊、減法運算及比較模塊,虛框表示FPGA芯片外圍電路。

設計遵從了流水線和模塊化設計原則,把總模塊劃分為幾個功能獨立又相互聯(lián)系的子模塊;上一個模塊的輸出即為下一個模塊的輸入,由最后一個模塊完成最終結果的輸出。

各子模塊電路設計完成后,建立相應電路符號,在原理圖輸入方式下,將各單元電路符號按原理框圖邏輯關系連接,通過保存、編譯,再進行項目處理包括器件選擇、引腳定義,確認正確無誤后便完成了FPCA內部電路的設計,將設計項目下載至芯片,嵌入板級電路與其它器件配合使用,完成電路功能。

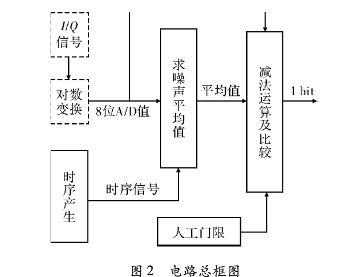

2.1 時序產生模塊

利用10 MHz時鐘產生τ脈沖RM;在休止期128 τ處產生平均值打入脈沖RM128和清除脈沖RST128。原理圖如圖3所示。

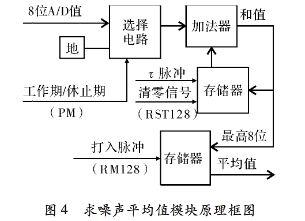

2.2 求噪聲平均值模塊

當休止期時,選8位I/Q信號幅度值進行累加,并對累加值進行鎖存,當累加128個單元后取出平均值用RM128打入存儲器鎖存輸出作為第一門限值,然后清除脈沖RST128清除累加值。取平均值方法:128個單元8位I/Q信號幅度值累加最大能達到15位數(shù),平均值即為高8位值,所以取累加值的高8位作為平均值即可,原理如圖4所示。

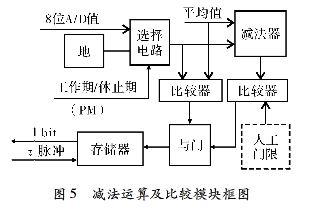

2.3 減法運算及比較模塊

在工作期選取8位I/Q信號幅度值一方面與噪聲平均值比較,另一方面減去噪聲平均值再與人工門限比較,如果兩次比較都為大于,則輸出 1 bit過門限信號。原理圖如圖5所示。

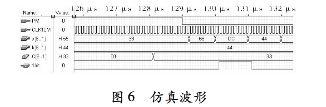

3 仿真

慢門限恒虛警處理電路仿真波形如圖6所示。PM=‘1’時為休止期,PM=‘0’時為工作期;為使仿真波形更直觀、易理解,休止期恒取8位I/Q信號幅度值X[8..1]=“33”,128單元后送出平均值C[8..1]=“33”;人工門限為恒定門限,此處設為K[8..1]=“44”;在工作期,當X[8..1]=“66”和“44”時,66-33<44、44-33<44故1 bit=‘0’,當X[8..1]=“DC”時,DC>33,DC-33>44連續(xù)通過兩道門限故1 bit=‘1’。

4 結束語

以上是在MaxplusⅡ環(huán)境中設計、編譯、仿真。一般為減少積累單元數(shù)和存儲計數(shù)設備,采用降低第一門限以達到高虛警率,而后面采用較高的人工門限以保證工作時的低虛警概率。該慢門限恒虛警處理電路的設計成功,為設計此類型電路提供了借鑒。采用8位二進制值累加128次,取高8位作為平均值的方法,使得電路易于實現(xiàn),該方法簡單、可靠。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

606007 -

芯片

+關注

關注

456文章

51170瀏覽量

427255 -

仿真

+關注

關注

50文章

4124瀏覽量

133993

發(fā)布評論請先 登錄

相關推薦

雷達信號檢測程序,包括MTI,多普勒濾波器組,恒虛警處...

基于自動刪除算法的廣義變化性指標恒虛警檢測器

噪聲恒虛警處理電路的計算機仿真

新的基于單元逼近的恒虛警率檢測器

一種基于FPGA的慢門限恒虛警處理電路設計

saber仿真軟件波形如何處理分析、saber仿真軟件如何畫電路圖

基于數(shù)字技術實現(xiàn)閉環(huán)式噪聲電平恒定電路的設計

基于ADSP-TS201處理器實現(xiàn)雷達恒虛警的軟硬件設計和系統(tǒng)仿真分析

紅外預警衛(wèi)星系統(tǒng)虛警抑制技術綜述

基于ADSP-TS201的著陸雷達恒虛警電路實現(xiàn)

采用FPGA芯片的慢門限恒虛警處理電路設計及波形仿真分析

采用FPGA芯片的慢門限恒虛警處理電路設計及波形仿真分析

評論