商業衛星通信系統工作在惡劣環境和極端溫度中,符合高可靠應用的所有要求。即便它們對于公司使命并不關鍵,但電信服務商和廣播公司仍依賴它們來交付創收服務。直到最近,自適應天線的運用還不算是一個成熟技術,而現在已有可能把它們用在這些通信系統中,前提是多個信道同步這一難題得到解決。

自適應天線系統使網絡運營商能增加無線網絡容量。自適應天線能有效定位和跟蹤多個信號,來動態地使干擾最小化,預期的信號接收最大化,因此有望提供更高的頻譜效率,更大的覆蓋范圍,更高的頻率復用率。但是,這些性能優勢會導致更高的復雜性,結果,自適應天線收發器被常規體系結構更復雜。需要為每個天線陣列元件準備單獨的收發器信道,并且信道之間需要準確的實時同步。

天線類型

可按物理結構、輻射模式或工作頻率來對天線分類,但它們的設計目的均為輻射和接收電磁波。天線的目的是盡可能把電磁能轉換為電流,反之亦然。在這方面,天線是收發系統的自由空間和傳輸線之間的過渡結構。

自從機電技術在19世紀末期開始得到利用以來,這兩大設計領域已經實現了許多改進,科學家和工程師們努力提高效率、動態范圍和容量。能量分配到周圍空間以及從周圍空間收集能量的效率,對頻譜的運用、新網絡建設成本以及這些網絡提供的服務質量有深刻影響。

通過利用多根一起工作的天線來提高特定網絡的覆蓋范圍和容量,許多種技術得到部署應用。分集方法(Diversity)利用隨時間變化(例如衰減)的信號在各個位置不相同這一事實,來改善無線電波的接收。換言之,即便對于兩個相隔僅一個波長的位置,信號的衰減也很可能不相同。為利用這一事實,使用兩根相隔一定距離的天線來接收相同信號。在任何特定時間,在兩個信號當中,信號電平最高的那個被自動發送到接收器。分集常用于信號接收。

天線還經常被排列成多元陣列。陣列是幾個互連的元件被排列成勻稱的結構,來形成單個天線。陣列的用途是產生某些輻射模式,它們具有單個元件無法實現的某些合乎需要的特征。當幾個天線元件被組合在陣列中(稱作陣列因子)時,總體輻射模式會改變。

還可連貫地組合多個孔徑的輸出,來產生將在接收子系統中被解調的信號。更先進的天線技術已經開發成功,使一根天線能迅速改變其輻射模式,來響應接收信號到達方向的變化。這些天線以及配套技術被稱作自適應天線或智能天線。

智能天線體系結構

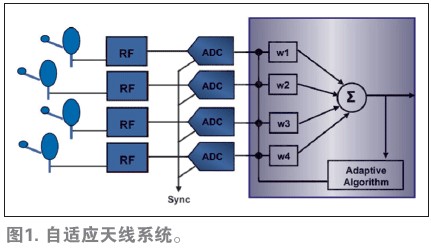

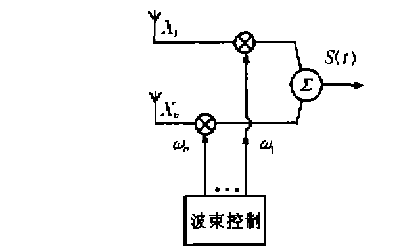

自適應或智能天線進一步拓展了分集概念。典型的自適應天線系統如圖1所示。此類系統把天線陣列與數字信號處理能力結合起來,以便用一種自適應的空間敏感方式來完成收發。自適應天線能實時修改其輻射模式,來確保主瓣指向最大信號電平的方向。該方法還可被用于指向某個不需要的干擾信號方向中的無信號狀態。

本質上,可在相同方向采用幾個元件來放大較弱的預期信號,并消除不需要的干擾。同樣,系統可以把信號組合起來,并把它們朝相同方向發射。這類方法還被稱作波束成形。結果就是各個元件的動態范圍可被集中起來,并能區分預期信號和非預期信號。此類好處使得自適應天線系統與常規系統相比很有吸引力。事實上,自適應天線方法的采用有望對頻譜的高效使用、新無線網絡建設成本的最小化、服務質量的優化產生重要影響。

但是,實現更高性能的代價是使收發器更加復雜,這是因為自適應系統需要為每個陣列元件準備單獨的收發鏈。各個收發鏈必須精確同步,以便保持發射信號和接收信號之間的相位關系。本節僅重點介紹接收子系統。現代接收系統采用很快的ADC,采樣率至少為1Gsps。人們需要高采樣頻率,這是因為奈奎斯特帶寬(Nyquist bandwidth)與ADC采樣頻率有很簡單的直接關系,NyquistBW=FS/2,其中FS即為ADC采樣速率。

增加信息量

有效增加奈奎斯特帶寬,就能增加收發器中的每條ADC信道的信息載波,由此提高系統吞吐率。與多信道接收器中的同步有關的一個挑戰是,采樣率很高的ADC會產生很高的數據速率。正常情況下,ADC有一個輸出時鐘來把輸出數據鎖到FPGA或ASIC中。但是,多信道收發器中的ADC輸出時鐘之間的相位關系是未知的。

系統設計者面臨的挑戰是要使來自多個運行于每秒數百兆或數千兆的ADC的數據同步。在系統級,一般不會試圖使ADC自身同步,而是實施額外數字電路來使ADC之后的FPGA或ASIC里的數字數據重新同步。這條額外的復雜數字電路處理ADC的高速數據輸出,此外還需要額外的電路開銷(overhead circuitry)來確定ADC之間的實際相位關系。因此,系統級同步的缺點是需要額外高速數字電路來處理ADC輸出,并且多個轉換器之間實際相位關系的確定所需的開銷電路很復雜。

ADC10D1000等等配備創新技術的新型轉換器能克服這個技術難題——在自適應天線系統中使多條信道同步。該器件是National Semiconductor公司的超高速空間適用ADC家族的新成員。它采用0.18μm純CMOS工藝制造,滿足100krad總輻射劑量(TID),并且對于超過120MeV/mg/cm2的密度具備單事件閉鎖抗擾度。該設計產生的有效位數(ENOB)高達9.0,具有248MHz輸入信號和1GHz 采樣率,同時提供10-18誤碼率。該產品采用376引腳密封CCGA封裝。

同步多個接收器信道

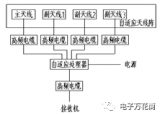

該型號有兩個特性來同步系統中的多個ADC:AutoSync和DCLK Reset(圖2)。DCLK Reset特性工作方式與AutoSync特性不同,但本質上執行的是相同功能。但是,當人們試圖同步三個或更多ADC時,板級實施會更具挑戰性。

AutoSync 是一種擁有專利的技術,不斷地使系統中的多個此類轉換器同步。它的工作方式無需特殊的同步脈沖,并且同步期間可能引起的任何擾動都會在一個DCLK時鐘周期內得到恢復。主/從ADC可被排列成一棵二元樹結構(binary tree),這樣任何擾動將很快從系統去除掉。

該技術指定一個ADC為主ADC,系統中其它的為從ADC。一個帶有一個主ADC和兩個從ADC的系統實例如圖3所示。主ADC提供兩個基準時鐘——RCLK1、 RCLK2,它們被一號和二號從ADC使用。為簡單起見,只顯示一個DCLK。但在現實中,有DCLKI和DCLKQ時鐘,但根據內部芯片設計,它們生來就同相。對于數據轉換器數量更多的更先進系統,鏈中的每個ADC被輪流用于產生兩個基準時鐘,這樣基準時鐘就以二元樹形式傳播(圖3)。

復雜的同步

對于系統中有多個主ADC和從ADC的應用,AutoSync可被用于使各個從器件與各自的主器件同步,而DCLK Reset可被用于使主ADC彼此同步。為使多個ADC的DCLK以及數據輸出同步,各個DCLK必須同時過渡,并且彼此同相。每個ADC的DCLK是在一段等待時間后從CLK生成的,加tOD(輸出數據延時)減tAD(孔徑延時)。因此,要想使DCLK同時過渡,CLK信號必須同時到達每個ADC。

為了消除通往每個ADC的CLK路徑中的任何差異,可使用tAD調節特性。但是,使用該特性,還會影響DCLK在輸出端產生的時間。如果器件處于解復用器方式,那么就有四個可能的相位,每個DCLK可能會在其中某個相位上被生成,這是因為對于本案例,典型的CLK是1GHz,而DCLK是250MHz。 RCLK信號控制著DCLK的相位,使得每個從DCLK與主DCLK同相。

有四個步驟來實現這個目標。首先,通過SPI把一號 ADC配置成主器件,并把其它所有ADC配置成從器件。然后,對于其基準時鐘給其它ADC饋電的那些ADC,給它們的基準時鐘通電。它們的默認方式是斷電,以便省電。在下一步,對于每個從ADC,調整RCLK_IN時序來實現清潔記錄。

最后,對于每個從ADC,選擇四個DCLK相位中的某個,使得DCLK相位與主器件的相位匹配。用戶可以選擇那個通過SPI來對齊兩個DCLK的相位。

責任編輯:gt

-

接收器

+關注

關注

14文章

2479瀏覽量

72214 -

天線

+關注

關注

68文章

3212瀏覽量

141146 -

衛星通信

+關注

關注

12文章

727瀏覽量

38823

發布評論請先 登錄

相關推薦

基于AccelDSP的自適應濾波器設計

在WCDMA中LMS自適應天線陣的硬件實現

基于WCDMA技術規范的LMS自適應天線陣的硬件實現

CDMA系統中的幾種智能天線自適應算法

PSAM自適應調制OFDM系統模型

基于LS-LMS的智能天線自適應干擾抑制方法

WCDMA中LMS自適應天線陣的硬件實現

如何才可以不使用自適應算法實現智能天線系統

自適應天線系統的原理及應用優勢分析

自適應天線系統的原理及應用優勢分析

評論