在多媒體應(yīng)用中,多媒體信息絕大部分是視頻數(shù)據(jù)和音頻數(shù)據(jù),而數(shù)字化的視頻數(shù)據(jù)和音頻數(shù)據(jù)的數(shù)據(jù)量是非常龐大的。為了能夠及時(shí)完整地處理前端采集的數(shù)據(jù),一般系統(tǒng)都采用高速DSP和大容量緩沖存儲器,且緩沖存儲器一般選用同步動(dòng)態(tài)隨機(jī)存儲器(SDRAM)。由于DSP不能直接與SDRAM接口,而且SDRAM控制時(shí)序比較復(fù)雜,因此本文介紹如何利用電可擦除可編程邏輯器件實(shí)現(xiàn)TMS320C5402與SDRAM的接口。

1 、SDRAM結(jié)構(gòu)和命令

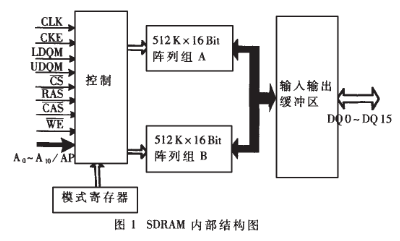

SDRAM是一種具有同步接口的高速動(dòng)態(tài)隨機(jī)存儲器,本文選用的是Samsung公司512K×16Bit×2組的KM416S1120D。SDRAM的同步接口和內(nèi)部流水線結(jié)構(gòu)允許存儲外部高速數(shù)據(jù),其內(nèi)部結(jié)構(gòu)框圖如圖1所示。

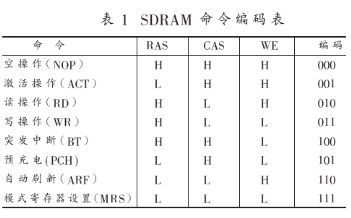

在具體操作SDRAM時(shí),首先必須通過MRS命令設(shè)置模式寄存器,以便確定SDRAM的列地址延遲、突發(fā)類型、突發(fā)長度等工作模式;再通過ACT命令激活對應(yīng)地址的組,同時(shí)輸入行地址;然后通過RD或WR命令輸入列地址,將相應(yīng)數(shù)據(jù)讀出或?qū)懭雽?yīng)的地址;操作完成后用PCH命令或BT命令中止讀或?qū)懖僮鳌T跊]有操作的時(shí)候,每32ms必須用ARF命令刷新數(shù)據(jù)(2048行),防止數(shù)據(jù)丟失。

2、 FLEX10K系列EPLD特點(diǎn)

FLEX10K系列EPLD是工業(yè)界第一個(gè)嵌入式的可編程邏輯器件,主要由嵌入式陣列塊(EAB)、邏輯陣列塊(LAB)、快速布線通道(FastTrack)和I/O單元組成,具有如下特點(diǎn):

(1)片上集成了實(shí)現(xiàn)宏函數(shù)的嵌入式陣列和實(shí)現(xiàn)普通函數(shù)的邏輯陣列;

(2)具有10000~250000個(gè)可用門;

(3)支持多電壓I/O接口,遵守PCI總線規(guī)定,內(nèi)帶JTAG邊界掃描測試電路;

(4)可快速預(yù)測連線延時(shí)的快速通道連續(xù)式布線結(jié)構(gòu);

(5)多達(dá)6個(gè)全局時(shí)鐘信號和4個(gè)全局清除信號;

(6)增強(qiáng)功能的I/O引腳,每個(gè)引腳都有一個(gè)獨(dú)立的三態(tài)輸出使能控制,都有漏極開路選擇。

3、 TMS320C5402和SDRAM接口設(shè)計(jì)

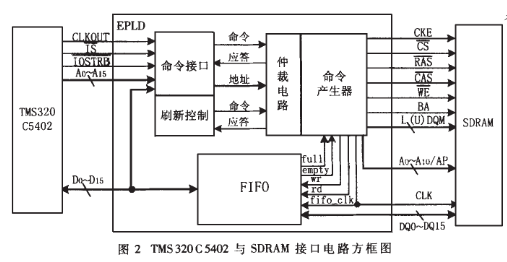

TMS320C5402和SDRAM接口電路方框圖如圖2所示。

命令接口主要對DSP送來的SDRAM的地址和操作命令進(jìn)行解碼(命令編碼見表1);刷新控制主要對SDRAM數(shù)據(jù)刷新進(jìn)行計(jì)時(shí),確保32ms刷新2048行數(shù)據(jù);仲裁電路主要對讀寫命令和刷新命令進(jìn)行仲裁,杜絕同時(shí)操作,防止數(shù)據(jù)丟失;命令產(chǎn)生器主要用來產(chǎn)生控制SDRAM的各種時(shí)序,完成SDRAM的讀、寫和刷新,同時(shí)控制FIFO的讀、寫操作;FIFO是DSP與SDRAM之間的數(shù)據(jù)通道,深度為256,其作用是充分利用SDRAM的突發(fā)讀寫功能,提高系統(tǒng)速度,同時(shí)簡化DSP軟件設(shè)計(jì)。

3.1 命令接口和刷新控制電路設(shè)計(jì)

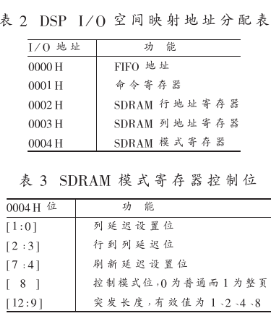

命令接口電路主要由命令寄存器、命令譯碼器、SDRAM行列地址鎖存器、模式寄存器組成。其中命令寄存器映射為DSP的I/O空間0001H,SDRAM行和列地址鎖存器分別映射為DSP的I/O空間0002H和0003H,模式寄存器映射為DSP的I/O空間0004H,具體控制命令和I/O地址分配如表2、表3所示。

DSP每次進(jìn)行讀、寫操作時(shí),首先向其I/O空間0002H和0003H寫入SDRAM行和列地址,然后向I/O空間0001H寫入控制命令,命令譯碼器根據(jù)命令寄存器中命令,譯碼后向仲裁電路發(fā)出讀寫請求。

刷新控制電路主要由1562計(jì)數(shù)器構(gòu)成。由于TMS320C5402時(shí)鐘頻率為100MHz,SDRAM要求在32ms之內(nèi)刷新2048行數(shù)據(jù),因此該計(jì)數(shù)器計(jì)數(shù)值應(yīng)小于:

32ms/2048/0.01μs=1562.5。當(dāng)計(jì)數(shù)器計(jì)滿1562次時(shí),刷新控制電路向仲裁電路發(fā)出刷新要求。

3.2 仲裁電路和命令產(chǎn)生器設(shè)計(jì)

仲裁電路接收命令接口模塊解碼的命令和刷新控制模塊的刷新請求,產(chǎn)生適當(dāng)?shù)目刂泼睿渲兴⑿抡埱蟮膬?yōu)先級較高。當(dāng)來自DSP的命令和來自刷新控制模塊的刷新請求同時(shí)到達(dá)時(shí),則首先執(zhí)行刷新操作,然后執(zhí)行來自DSP的命令。這樣可以防止SDRAM的數(shù)據(jù)丟失。由此可知,仲裁電路實(shí)質(zhì)上是一個(gè)優(yōu)先級選擇器。

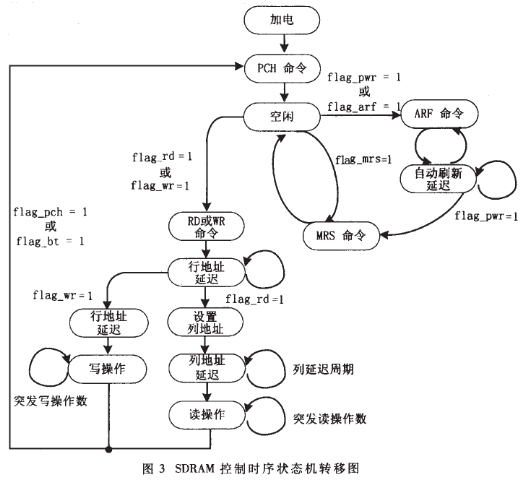

命令產(chǎn)生器主要產(chǎn)生SDRAM讀、寫和刷新的控制時(shí)序(具體時(shí)序可見參考文獻(xiàn)1)以及FIFO的讀寫控制信號,用以對SDRAM進(jìn)行各種操作,其實(shí)質(zhì)上是一個(gè)Mealy型狀態(tài)機(jī),利用VHDL語言可以很方便地實(shí)現(xiàn),其狀態(tài)轉(zhuǎn)移圖如圖3所示。

3.3 FIFO設(shè)計(jì)

FIFO電路是DSP與SDRAM進(jìn)行數(shù)據(jù)交換的通道,通過FIFO電路可以很好地實(shí)現(xiàn)DSP對SDRAM的讀寫。FIFO電路被映射為DSP的I/O空間0000H(見表2),DSP對SDRAM的每次讀或?qū)懀紝SP的I/O空間0000H操作,簡化了DSP軟件設(shè)計(jì)。利用FLEX10K系列EPLD內(nèi)部嵌入式陣列塊(EAB)和參數(shù)化模塊庫(LPM),可以很快地構(gòu)造出256×16的FIFO電路,F(xiàn)IFO的設(shè)計(jì)比較簡單。VHDL描述具體如下(注意在程序開始處添加LPM庫):

FIFO256 CSFIFO

GENERIC MAP LPM_WIDTH <= 16;LPM_NUM-

WORDS <= 256;

PORT MAP data <= LPM_WIDTH-1 DOWNTO 0;

wreq <= wr;rreq <= rd;

clock <= clk50;clockx2 <= clk100;

clr <= clr;sclr <= sclr;

empty <= empty;full <= full;

q<=qLPM_WIDTH-1 DOWNTO 0;

由于EPLD通用、高速及價(jià)廉的特點(diǎn),因此具有很好的實(shí)際應(yīng)用前景,尤其適用于需要大容量高速緩沖存儲器的多媒體應(yīng)用。

責(zé)任編輯:gt

-

SDRAM

+關(guān)注

關(guān)注

7文章

430瀏覽量

55371 -

存儲器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164350 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

517瀏覽量

44184

發(fā)布評論請先 登錄

相關(guān)推薦

可編程邏輯器件

求一種可利用復(fù)雜可編程邏輯器件設(shè)計(jì)技術(shù)實(shí)現(xiàn)的專用鍵盤接口芯片方案

如何利用EPLD實(shí)現(xiàn)TMS320C5402與SDRAM接口?

PLD可編程邏輯器件

可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗(yàn)指導(dǎo)書

什么是PLD(可編程邏輯器件)

基于可編程邏輯器件的數(shù)字電路設(shè)計(jì)

EDA技術(shù)與應(yīng)用(可編程邏輯器件)

電可編程邏輯器件EPLD是如何設(shè)計(jì)的

可編程邏輯器件測試

利用電可擦除可編程邏輯器件實(shí)現(xiàn)DSP與SDRAM接口設(shè)計(jì)

利用電可擦除可編程邏輯器件實(shí)現(xiàn)DSP與SDRAM接口設(shè)計(jì)

評論