DDS 技術是近幾年來迅速發展的頻率合成技術, 它采用全數字化的技術, 具有集成度高、體積小、相對帶寬寬、頻率分辨率高、跳頻時間短、相位連續性好、可以寬帶正交輸出、可以外加調制的優點, 并方便與控制器接口構成智能化的頻率源。由于基準時鐘的頻率一般固定, 因此相位累加器的位數決定了頻率分辨率, 位數越多, 分辨率越高。基于DDS 諸多優點, 本系統采用DDS技術來實現數字調制功能, 充分發揮DDS 的優勢, 使系統結構簡單、功能強大。

1 硬件實現及工作原理

本系統為一套無線數據傳輸系統, 硬件電路分為發射機電路和接收機電路兩部分。

1.1 發射機電路

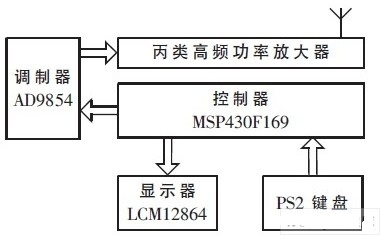

如圖1 所示,發射機硬件電路主要由控制器、調制電路、高頻功率放大器、天線、顯示電路與電源部分組成。

圖1 發射機組成圖

控制器以TI 公司高性能混合信號處理器MSP430F169為核心, 完成對DDS 、鍵盤、LCD 顯示器的控制和信息處理的功能。MSP430F169 為16 bit 具有精簡指令集的超低功耗混合信號處理器(Mixed Signal Processor) , 采用1.8 V~3.6 V 電源電壓, 在1 MHz 的時鐘條件下運行時,芯片的電流在200 μA~400 μA, 時鐘關斷模式的最低功耗只有0.2 μA,在8 MHz 晶體驅動下指令周期為125 ns。

且MSP430F169 具有豐富的片上外圍模塊, 如看門狗、模擬比較器、定時器、串口、硬件乘法器等。在本系統中,MSP430F169 工作在3.3 V 電壓、8 MHz 主頻下。

調制電路以ADI 公司單片DDS 芯片AD9854 為核心。該芯片最高系統時鐘為300 MHz , 理論輸出信號頻率范圍為直流到150 MHz,最高并行編程速率為100 MHz,采用3.3 V 單電源供電, 與上述控制器芯片匹配, 無需加電平轉換電路,從而實現控制器與調制器的無縫接口。

AD9854 支持10 MHz 串行通信方式和100 MHz 并行通信方式, 本系統采用串行數據輸入方式。AD9854 內置4~20 倍頻的PLL, 外部較低頻率的參考時鐘可通過倍頻后得到300 MHz 的系統時鐘, 這樣就避免了設計高頻參考時鐘的難度, 降低了高頻時鐘干擾。AD9854 參考時鐘的輸入有單端輸入和差分輸入兩種方式, 為了使電路簡單, 本設計選用單端輸入方式。外部20 MHz 有源晶振輸出經PLL 電路15 倍頻到300 MHz 后作為系統時鐘。

濾波器采用由3 個電感和7 個電容構成的七階橢圓濾波器, 因為AD9854 的最高工作頻率為300 MHz , 而DDS輸出最高頻率為系統工作頻率的40%左右, 所以本方案中濾波器的截止頻率設計為120 MHz, 有效濾除了高頻干擾,使輸出信號較為平滑。

高頻功率放大器工作在丙類方式, 能夠實現較高的效率。顯示器采用LCM128 128×64 點字符點陣液晶顯示器, 用來完成人機交互界面和信息的顯示功能。電源部分采用LM2576-3.3 三端穩壓片, 能夠提供最高3 A 的電流輸出, 完全滿足本系統的要求。同時為了防止AD9854工作時對電源造成干擾, 電路設計采用了大量的濾波電容, 且對數字電源和模擬電源作了很好的隔離, 以防止數字電源對模擬電源的串擾。

1.2 接收機電路

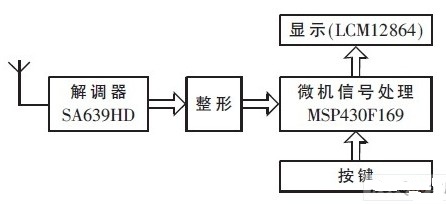

接收機硬件電路由解調電路、數據處理器、顯示電路及電源部分組成, 接收機框圖如圖2 所示。

圖2 接收機組成圖

解調器以飛利浦專用FSK 解調芯SA639DH 為核心部件。它具有靈敏度高、動態范圍大、傳輸速率快、穩定性好等特點。天線接收到的信號經輸入回路取出的2FSK信號與本振信號同時送入乘法器進行混頻, 再經一級帶通濾波器濾除高頻分量取其下變頻到中頻, 然后進行中頻放大后經二級帶通濾波送入限幅放大器進行限幅放大。限幅放大后的信號被分成兩路, 一路直接送入乘法器, 另一路經移相網絡移相90° 產生調相調頻波再送乘法器, 兩路信號進行相位比較, 乘法器輸出的信號經低通濾波器取出原調制信號, 然后再把該信號送入比較器進行整形后送信號處理器進行處理。

接收機數據處理器同樣采用MSP430F169 , 顯示器采用與發射機相同的LCM12864 。由于接收機部分與發射機相比功耗低, 故接收機電源部分采用兩節5 號干電池串聯供電。

2 系統軟件的實現

2.1 發射機的軟件設計

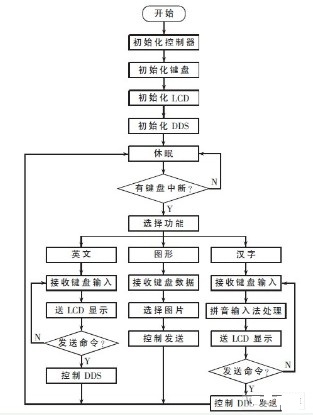

發射機上電后, 首先對系統進行初始化, 包括對控制器本身的端口配置、片內外設的配置, 以及外部的AD9854[ 6]、PS2 鍵盤和顯示器等部件的初始化。初始化結束后系統進入休眠模式, 直到被外部鍵盤產生的中斷喚醒。然后根據得到的按鍵鍵碼進行相應處理。為了讓AD9854 產生2FSK 信號, 需進行如下的初始化過程:S/PSELECT 置1 或置0 以決定輸入數據是并行還是串行。1為并行,0 為串行; 本系統采用串行接口, 在SCLK 信號控制下從并行輸入口D0~D1 寫入48 bit 并行寄存器, 或在SCLK 控制下從串行輸入口SDATA 寫入48 bit 串行寄存器。發射機的軟件流程圖如圖3 所示( 注: 在發射機內部存儲有3 幅圖片) 。

圖3 發射機流程圖

2.2 接收機的軟件設計

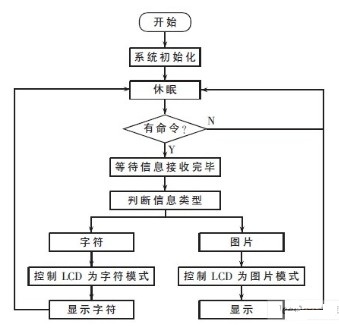

接收機不需要區分接收到的是英文字符還是漢字,故軟件設計相對發射機來說較容易。同樣, 開始對信號處理器以及外設進行初始化, 使其工作在等待信息接收狀態, 此時, 只有接收機射頻部分電路工作, 其他部件處于休眠模式。當接收機檢查到有信息到來時, 通過中斷喚醒控制器, 控制器再喚醒其他外設進行數據接收和處理。接收到的信息經信號處理器判斷, 如果為字符( 包括英文字符和漢字) , 則控制LCD 進入字符模式, 進行字符的顯示; 如果為圖片, 則控制LCD 進入圖片模式, 進行圖片顯示。接收機的軟件流程如圖4 所示。

圖4 接收機流程圖

3 系統測試結果

(1) 載波中心頻率:發射機在2FSK 模式時,1 和0 所對應的兩個頻率分別為fH=30.003 000 MHz 和fL=29.997 000 MHz,系統在空閑時發射頻率為30.000 000 MHz , 故選取頻率為30.000 000 MHz 為中心頻率。

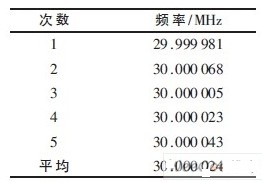

(2) 頻率穩定度: 在單片機復位的前提下, 用頻率計每隔2 min 測一次AD9854 的輸出頻率,共測5 次,如表1所示。根據測試結果計算:

表1 AD9854 輸出頻率測量值

頻率穩定度=最大頻率偏差/中心頻率=(30.000 068-29.999 981)÷30.000 024=0.000 087÷30.000 024=2.9×10-6(3) 發射功率: 在發射功率級末端接50 Ω 假負載,用100 MHz 數字示波器測得發射信號的輸出電壓峰峰值VP-P, 據公式P=V2P-P/8RL, 得到發射功率值, 實驗測得VP-P=2.98 V,P=V2P-P/8RL=22.2 mW。

(4) 傳輸速率: 發射機、接收機在通信距離為10 m 的情況下, 分別以1.2 kb/s 、9.6 kb/s 、57.6 kb/s 、115.2 kb/s的波特率傳送5 次20 個漢字, 漢字錯誤率均為零。

(5) 圖形傳送功能: 發射機、接收機。發射機調用機內自帶的三幅圖形( 分別為公雞、小兔及西工大校徽) 以點陣的形式傳送, 接收機能夠不失真接收, 說明本系統具有圖形的點陣傳送功能。

本系統可以簡單高效地進行無線數據傳輸, 是實現無線通信的一種簡單可行的設計方案。經過系統測試,系統技術指標令人滿意, 工作可靠。另外, 由于本系統采用DDS 來實現信號調制, 故可以比較容易地改變調制信號頻率, 為實現跳頻通信提供了方便。

-

控制器

+關注

關注

112文章

16448瀏覽量

179483 -

功率放大器

+關注

關注

102文章

3626瀏覽量

132299 -

天線

+關注

關注

68文章

3213瀏覽量

141152

發布評論請先 登錄

相關推薦

采用DDS技術實現無線數據傳輸系統的數字調制功能設計

采用DDS技術實現無線數據傳輸系統的數字調制功能設計

評論