1 引言

當前,越來越多的設計應用領域要求具有高精度的A/D轉換和實時處理功能。在實時數(shù)據(jù)采集處理系統(tǒng)設計中,一般需要考慮數(shù)據(jù)采集以及對采集數(shù)據(jù)的處理。而對于大數(shù)據(jù)量的實時數(shù)據(jù)采集處理系統(tǒng)來說,保持數(shù)據(jù)高速傳輸也是該系統(tǒng)性能的關鍵因素。

采用TMS320VC5402和轉換器ADuC841構成雙CPU處理器平臺,充分利用TMS320VC5402的對大容量數(shù)據(jù)和復雜算法的處理能力,ADuC841接口的控制能力以及各自擁有的DMA控制器構建實時數(shù)據(jù)采集處理系統(tǒng)。雙CPU通過DMA方式實現(xiàn)數(shù)據(jù)交換,將數(shù)據(jù)傳輸和系統(tǒng)控制分開,提高了數(shù)據(jù)傳輸速度,降低了處理器負擔,提高系統(tǒng)運行效率。采用此解決方案。大大提高了系統(tǒng)的信號采集和處理能力。

2系統(tǒng)硬件設計

2.1 ADuC841簡介

ADuC841是ADI公司ADuC84X系列中性能最完善的一款微轉換器,它具有單周期指令,20 MI/s的8052內(nèi)核;內(nèi)置一個8通道、高速420 Ks/s、高精度自校正、12位逐次逼近的ADC,具有DMA控制:2通道12位DAC;2通道PWM方式∑-△型DAC;片上15 ppm/℃高穩(wěn)定電壓基準;片上溫度傳感器;62 KB片內(nèi)Flash/EE程序存儲器;4 KB的片內(nèi)Flash/EE數(shù)據(jù)存儲器。還包括看門狗定時器和電源.、ADC與數(shù)據(jù)存儲器之間的DMA方式、存儲保護功能、通用異步串行收發(fā)器(UART)、SPI和I2C總線接口等功能模塊。

ADuC841片內(nèi)的ADC的轉換速率為2.38μs/次(420 kHz的采樣率)。當A/D轉換時,ADuC841必須在2μs內(nèi)讀取A/D轉換結果并將其傳輸且存儲到外部存儲器中以便后續(xù)處理,否則將導致下一個轉換結果出現(xiàn)后丟失前一個轉換結果。由于中斷服務子程序中存儲轉換結果和微轉換器跳轉到ADC的中斷服務子程序都需要時間,因此很多應用無法響應高的中斷速率。采用ADC的DMA方式傳輸數(shù)據(jù)能夠解決上述問題,通過設置特殊功能寄存器ADCCON2中的中斷響應位即可使能ADC的DMA方式。這種方式下,無需CPU的軟件中斷響應干預,可通過硬件直接檢測相應控制位就能將ADC的轉換結果直接輸出并存儲到片外的靜態(tài)RAM中,并提供了一個高速數(shù)據(jù)傳輸通道,從而保證了ADC能以最高速率(420 kHz)完成數(shù)據(jù)采樣和轉換,并進行高速信號傳輸。

2.2數(shù)字信號處理器TMS320VC5402簡介

TMS320VC5402 是 TI 公 司 的TMS320C5000系列之一,它采用改進的哈佛結構,具有分離的程序總線和數(shù)據(jù)總線,采用4級流水線作業(yè),其運行速度可達100 MI/S,具有高速運行的特點。同時提供豐富的指令集,增強的模塊化結構設計,具有通用性,拓展了應用領域。TMS320VC5402可尋址3個獨立的存儲空間,包括1 MB×16的程序空間,64 KB×16的數(shù)據(jù)空間以及64 KB×16位的I/O端口空間。片內(nèi)提供16 KB×16的雙存取RAM和4 KB×16的ROM,并具有直接存儲器訪問(DMA)功能,通過HOLD允許對外部程序、數(shù)據(jù)以及I/O空間進行直接存儲器訪問。TMS320VC5402存儲器直接存儲控制DMA可在不占用CPU資源的情況下,實現(xiàn)DSP存儲器間數(shù)據(jù)的自由傳輸。TMS320VC5402有6個可獨立編程的DMA通道,每個DMA通道由各自的寄存器控制。

2.3系統(tǒng)的硬件結構

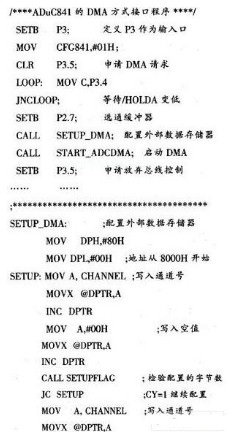

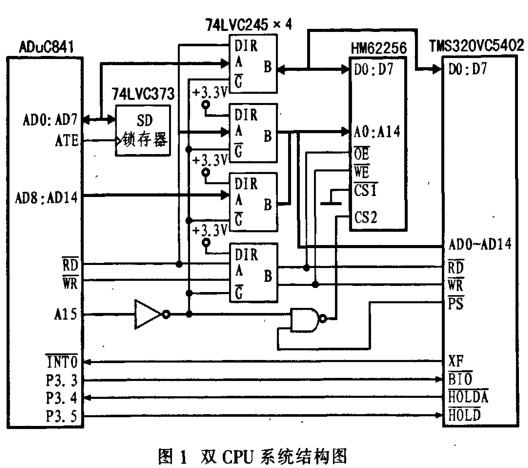

設計DMA共享存儲器實現(xiàn)雙機通訊需要考慮以下幾點:(1)設計ADuC841和TMS320VC5402之間數(shù)據(jù)總線和地址總線的隔離電路。隔離電路在雙CPU不通信時隔離地址總線和數(shù)據(jù)總線,而在DMA通信時則選通。(2)設計ADuC841和TMS320VC5402都能對存儲器讀寫的選通信號和讀寫信號。(3)設計控制TMS320VC5402信號及其響應信號。

考慮上述問題,采用ADuC841與TMS320VC5402的雙CPU系統(tǒng)結構如圖1所示。存儲器HM62256既是TMS320VC5402的全局數(shù)據(jù)存儲器,又是ADuC841的外部存儲器。A15為片選信號,地址范圍為8000H~FFFFH。兩個CPU分別通過總線和數(shù)據(jù)存儲器HM62256相連,實現(xiàn)存儲器共享。

隔離電路采用4片74LVC245雙向緩沖器實現(xiàn),由于ADuC841的P0口是分時復用的地址/數(shù)據(jù)總線,所以需采用一片74LVC373地址鎖存器將P0端口的地址信號從地址/數(shù)據(jù)總線中分離出來。而ADuC841的16位數(shù)據(jù)總線需要雙向緩沖,由于ADuC841要對HM62256進行讀寫操作,所以緩沖器的方向由ADuC841的讀信號RD控制,當ADuC841讀數(shù)據(jù)時,RD為低電平,使數(shù)據(jù)緩沖方向為HM62256至ADuC841;寫數(shù)據(jù)時,RD為高電平,數(shù)據(jù)緩沖方向為ADuC841至HM62256。緩沖器的使能線由A15反向信號控制,當A15為高電平時,選通緩沖器,否則緩沖器為高阻態(tài)。A15還是HM62256的片選信號,若要ADuC841和TMS320VC5402都能選通HM62256,需將A15和PS的與非信號作為HM62256的片選信號。ADuC841選通時,PS為高電平,ADuC841的A15有效。TMS320VC5402選通時,當A15為低電平時,PS有效。

ADuC841通過P3.5、P3.2(INT0)分別與TMS320VC5402的HOLD、XF引腳相連,P3.5向TMS320VC5402申請總線控制,TMS320 VC5402響應ADuC841的請求后,HOLDA信號變低,TMS320VC5402的CPU掛起,并出讓外部總線。ADuC841通過A15打開總線驅動器,并經(jīng)與非門后選中HM62256,獲得HM62256的控制權,實現(xiàn)對HM62256的讀寫操作。而TMS320VC5402可通過XF向ADuC841請求中斷,ADuC841在響應中斷INT0后,通過P3.5將HOLD信號轉換為高電平,此時總線控制權重新交給TMS320VC5402。

3系統(tǒng)軟件設計

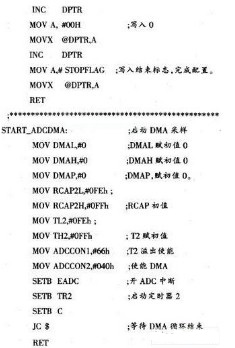

系統(tǒng)上電時,ADuC841由P3.5向DSP申請總線控制HM62256,設置DMA方式,通過配置3個特殊功能寄存器ADCCON1~ADCCON3,ADuC841的ADC工作在不同模式下。其中在DMA模式下,ADC可連續(xù)轉換,并將采樣值直接輸出并存儲到片外的HM62256中而無需來自CPU的任何軟件干預,從而保證ADC能以最高速度(420 kHz)完成采樣和轉換并進行高速信號傳輸。A/D轉換后,ADuC841通過ADC中斷,P3.5發(fā)送高電平至TMS320VC5402的HOLD引腳,向TMS320VC5402申請放棄總線控制,HM62256的總線控制權重新交換給TMS320VC5402,由TMS320VC5402進行數(shù)據(jù)處理。當TMS320VC5402處理完數(shù)據(jù)后,首先將運算結果放回HM62256,然后通過XF信號線通知ADuC841,ADuC841響應后,向DSP申請總線控制接管HM62256,讀出運算結果,然后進行下一步處理。以下是ADuC841的部分DMA接口程序代碼:

4 結束語

對于實時數(shù)據(jù)采集處理系統(tǒng),選取合理有效的核心算法是至關重要的,然而,選擇數(shù)據(jù)傳輸方法也是相當重要,在一些實際情況下,數(shù)據(jù)傳輸時間可能超過數(shù)據(jù)處理的時間。通過合理使用DMA高速數(shù)據(jù)傳輸是提高數(shù)據(jù)傳輸效率的一種途徑,有助于產(chǎn)品的開發(fā)。

-

存儲器

+關注

關注

38文章

7528瀏覽量

164342 -

緩沖器

+關注

關注

6文章

1930瀏覽量

45644 -

數(shù)據(jù)采集

+關注

關注

39文章

6251瀏覽量

114039

發(fā)布評論請先 登錄

相關推薦

基于CYUSB3014的高速實時數(shù)據(jù)采集系統(tǒng)

提高MES系統(tǒng)數(shù)據(jù)采集傳輸實時性的辦法及措施

采用LabVIEW實現(xiàn)USB實時數(shù)據(jù)采集處理系統(tǒng)設計

采用LabVIEW實現(xiàn)USB實時數(shù)據(jù)采集處理系統(tǒng)

實時數(shù)據(jù)處理系統(tǒng)有什么特點?

基于MAX3420的實時數(shù)據(jù)采集系統(tǒng)設計

基于DSP和光纜通信的遠程高速數(shù)據(jù)采集及處理系統(tǒng)的設計與應用

Windows CENET在高速實時數(shù)據(jù)采集系統(tǒng)中可移植性的研究

嵌入式高速實時數(shù)據(jù)采集系統(tǒng)設備驅動程序的研究

遠程高速數(shù)據(jù)采集及處理系統(tǒng)的設計

DSP和USB的高速數(shù)據(jù)采集與處理系統(tǒng)設計方案

基于TMS320VC5402芯片和ADuC841轉換器實現(xiàn)數(shù)據(jù)采集處理系統(tǒng)的設計

如何使實時數(shù)據(jù)采集處理系統(tǒng)保持數(shù)據(jù)的高速傳輸

如何使實時數(shù)據(jù)采集處理系統(tǒng)保持數(shù)據(jù)的高速傳輸

評論