濾波器是一種用來(lái)消除干擾雜訊的器件,可用于對(duì)特定頻率的頻點(diǎn)或該頻點(diǎn)以外的頻率進(jìn)行有效濾除。它在電子領(lǐng)域中占有很重要的地位,在信號(hào)處理、抗干擾處理、電力系統(tǒng)、抗混疊處理中都得到了廣泛的應(yīng)用。而對(duì)于程控濾波器,該系統(tǒng)的最大特點(diǎn)在于其濾波模式可以程控選擇,且-3 dB截止頻率程控可調(diào),相當(dāng)于一個(gè)集多功能于一體的濾波器,將有更好的應(yīng)用前景。此外,系統(tǒng)具有幅頻特性測(cè)試的功能,并通過(guò)示波器顯示頻譜特性,可直觀地反應(yīng)濾波效果。

1 方案論證與選擇

1.1 可變?cè)鲆娣糯竽K的設(shè)計(jì)與論證

方案1:數(shù)字電位器控制兩級(jí)INA129級(jí)聯(lián)。用FPGA控制數(shù)字電位器DS1267使其輸出不同的阻值,作為高精度儀表放大器INA129的反饋電阻。通過(guò)控制數(shù)字電位器來(lái)改變INA129的放大倍數(shù),從而實(shí)現(xiàn)放大器的增益可調(diào)。

方案2:采用可變?cè)鲆娣糯笃?/u>AD603實(shí)現(xiàn)。可變?cè)鲆娣糯笃鲀?nèi)部由R-2R梯形電阻網(wǎng)絡(luò)和固定增益放大器構(gòu)成,加在其梯型網(wǎng)絡(luò)輸入端的信號(hào)經(jīng)衰減后,由固定增益放大器輸出,衰減量是由加在增益控制接口的參考電壓決定;可通過(guò)單片機(jī)控制,由DAC產(chǎn)生精確的參考電壓控制增益,從而實(shí)現(xiàn)較精確的數(shù)控。

由于輸入的正弦小信號(hào)振幅10 mV,電壓增益60 dB,10 dB步進(jìn)程控可調(diào),且電壓增益誤差不能大于5%.對(duì)精度而言兩個(gè)方案都可實(shí)現(xiàn),在AD603后再加一級(jí)放大也可實(shí)現(xiàn)60 dB的放大倍數(shù)。但數(shù)字電位器內(nèi)部結(jié)構(gòu)復(fù)雜,有電容影響,后級(jí)接運(yùn)放后會(huì)帶來(lái)意想不到的后果,因此采用方案2。

1.2 濾波器模塊的設(shè)計(jì)與論證

方案1:采用數(shù)字濾波器。利用MATLAB的數(shù)字濾波器設(shè)計(jì)FIR或者IIR濾波器。數(shù)字濾波器具有精度高,截止特性好等優(yōu)點(diǎn)。但是FIR濾波器會(huì)占用太多FPGA資源,IIR濾波器設(shè)計(jì)時(shí)工作量大且穩(wěn)定性不高,且要使截止頻率可調(diào),必須使用不同的參數(shù),設(shè)計(jì)起來(lái)軟件量比較大。

方案2;采用無(wú)源LC濾波器。利用電感和電容可以搭建各種類型的濾波器。參照濾波器設(shè)計(jì)手冊(cè)上的相關(guān)參數(shù),可以比較容易地設(shè)計(jì)出理想的濾波器。但是如果要截止頻率可調(diào),只有改變電感電容參數(shù),硬件會(huì)非常復(fù)雜。

方案3:采用集成的開(kāi)關(guān)電容濾波器芯片。開(kāi)關(guān)電容濾波器是由MOS開(kāi)關(guān)、MOS電容和MOS運(yùn)算放大器構(gòu)成的一種大規(guī)模集成電路濾波器。其開(kāi)關(guān)電容組在時(shí)鐘頻率的驅(qū)動(dòng)下,可以等效成一個(gè)和時(shí)鐘頻率有關(guān)的等效電阻。當(dāng)用外部時(shí)鐘改變時(shí),等效電阻改變,從而改變了濾波器的時(shí)間常敦,也就改變了濾波特性。開(kāi)關(guān)電容濾波器可以直接處理模擬信號(hào),而不必像數(shù)字濾波器那樣需要A/D、D/A變換,簡(jiǎn)化了電路設(shè)計(jì),提高了系統(tǒng)的可靠性。

綜上所述,本系統(tǒng)采用方案3,利用集成芯片MAX297實(shí)現(xiàn)低通濾波器,利用LTC1068實(shí)現(xiàn)高通濾波器;采用方案2,利用無(wú)源LC濾波器技術(shù)來(lái)實(shí)現(xiàn)四階橢圓低通濾波器。

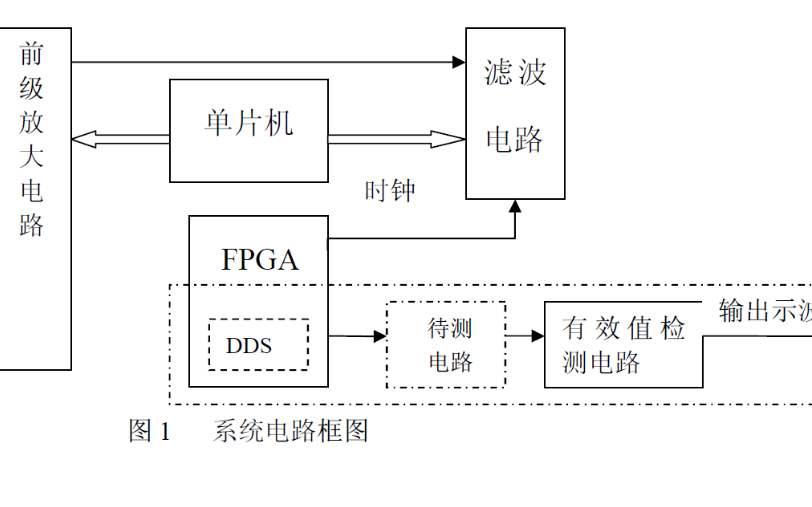

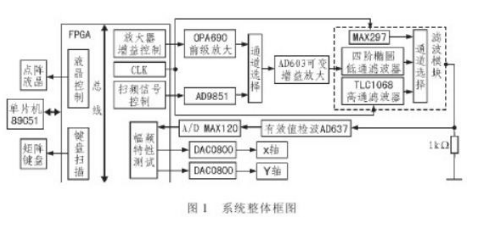

2 系統(tǒng)總體設(shè)計(jì)方案及實(shí)現(xiàn)方框圖

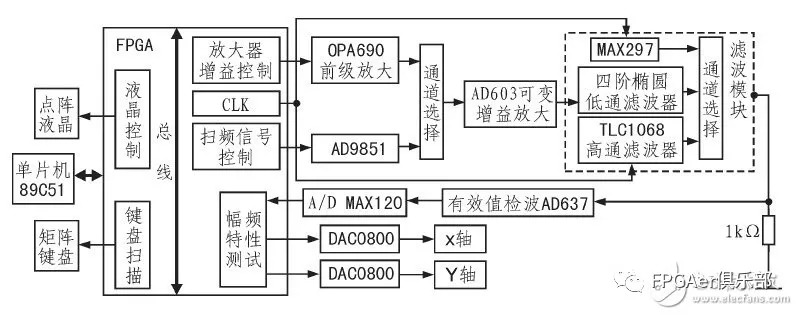

本系統(tǒng)以單片機(jī)及FPGA為控制核心,由可控增益放大模塊、程控濾波模塊和幅頻特性測(cè)試模塊構(gòu)成。系統(tǒng)框圖如圖1所示。輸入振幅為1 V的信號(hào)經(jīng)分壓網(wǎng)絡(luò)衰減后變成振幅10 mV的小信號(hào),經(jīng)OPA690前級(jí)放大2倍,同時(shí)起到阻抗變換和隔離的作用。與此同時(shí)由AD9851產(chǎn)生一設(shè)定頻率的正弦信號(hào),通過(guò)模擬開(kāi)關(guān)選擇一道送到后級(jí)。信號(hào)由程序控制AD603進(jìn)行0~60dB的可調(diào)增益放大后,送入濾波模塊。濾波模塊包括低通、高通、橢圓濾波器,其中低通、高通由程序控制-3 dB截止頻率在1~30 kHz范圍內(nèi)可調(diào),步進(jìn)1kHz.橢圓濾波器截止頻率50 kHz.再通過(guò)模擬開(kāi)關(guān)選擇某一特定濾波信號(hào)輸出,經(jīng)有效值檢波和A/D轉(zhuǎn)換后送入FPGA進(jìn)行幅頻特性的測(cè)試,再用兩塊DAC0800實(shí)現(xiàn)幅頻特性曲線的顯示。

圖1 系統(tǒng)整體框圖

3 主要功能電路設(shè)計(jì)

3.1 放大模塊

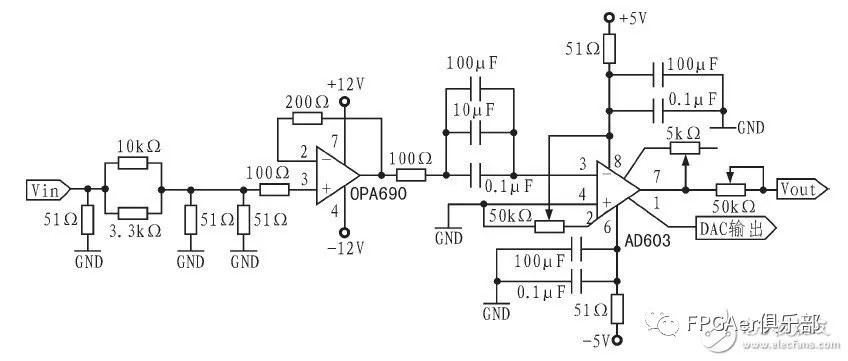

放大模塊的具體電路如圖2所示。第一部分是一個(gè)分壓網(wǎng)絡(luò),其中前4個(gè)電阻將輸入信號(hào)衰減100倍,并與信號(hào)源內(nèi)阻共同構(gòu)成51Ω阻抗,后面的51Ω為匹配電阻。第二部分采用OPA690將小信號(hào)放大2倍,同時(shí)起到阻抗變換和隔離的作用。由于AD603輸入阻抗為100Ω,所以在后面串接一個(gè)100 Ω的電阻進(jìn)行匹配。第三部分即為AD603可變?cè)鲆娣糯螅脑鲆骐S著控制電壓的增大以dB為單位線性增長(zhǎng)。1腳的參考電壓通過(guò)單片機(jī)進(jìn)行運(yùn)算并控制DAC芯片輸出電壓來(lái)得到,從而實(shí)現(xiàn)精確的數(shù)控。增益G(dB)=40VG+G0,其中VG為差分輸入電壓,范圍-500~500mV;G0是增益起點(diǎn),接不同反饋網(wǎng)絡(luò)時(shí)也不同。在5、7腳間接一個(gè)5kΩ的電位器,從而改變。

圖2 放大模塊

3.2 高通濾波模塊

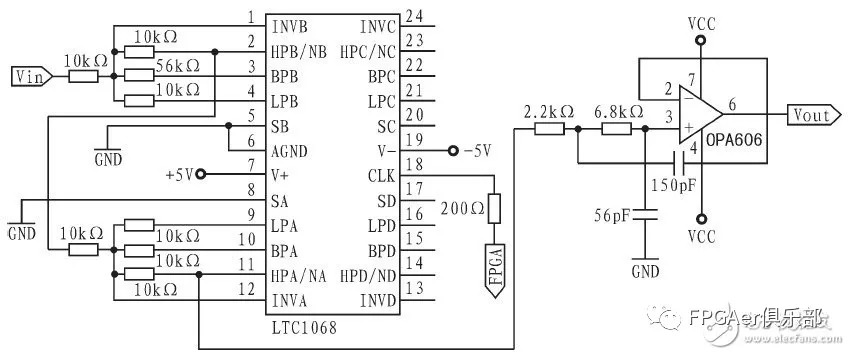

LTC1068是低噪聲高精度通用濾波器,當(dāng)其用于高通濾波時(shí),截止頻率范圍1 Hz~50 kHz,并且直至截止頻率的200倍都無(wú)混疊現(xiàn)象。由于LTC1068的4個(gè)通道都是低噪聲、高精度、高性能的2階濾波器,因此每個(gè)通道只要外接若干電阻就可以實(shí)現(xiàn)低通、高通、帶通和帶阻濾波器的功能。具體電路如圖3所示。其中B端口Q值0.57,A端口Q值約為1.在電路的調(diào)試中發(fā)現(xiàn),A口的Q值需比B口Q值大,否則信號(hào)在截止頻率處幅值會(huì)有上翹。

圖3 LTC1068高通濾波

LTC1068的時(shí)鐘頻率與通帶之比為200:1,由于LTC1068內(nèi)部對(duì)時(shí)鐘信號(hào)CLK二倍頻,所以當(dāng)截止頻率最小為1 kHz時(shí),內(nèi)部時(shí)鐘頻率其實(shí)為400kHz,故在LTC1068后面再加一個(gè)截止頻率為450kHz的低通濾波器以濾除分頻帶來(lái)的噪聲及高次諧波。

3.3 低通濾波模塊

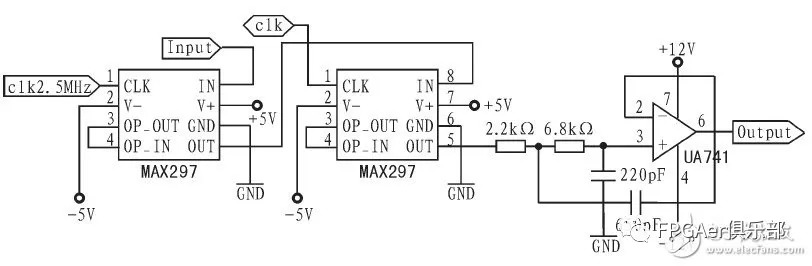

用MAX297實(shí)現(xiàn)低通濾波器。開(kāi)關(guān)電容濾波器MAX297可以設(shè)置為8階低通橢圓濾波器,阻帶衰減為-80dB,時(shí)鐘頻率與通帶頻率之比為50:1.通過(guò)改變CLK的頻率,即可滿足濾波器-3 dB截止頻率在1~20kHz范圍內(nèi)可調(diào),步進(jìn)1 kHz的要求。

在使用MAX297時(shí)要注意的是,當(dāng)信號(hào)頻率和采樣辨率同頻,開(kāi)關(guān)電容組在電容上各次采到相同的幅度為信號(hào)幅值的信號(hào),相當(dāng)于輸入信號(hào)為直流的情況,使濾波器輸出一個(gè)直流電平。同理,當(dāng)信號(hào)頻率為采樣頻率的整數(shù)倍時(shí),也會(huì)出現(xiàn)相同的現(xiàn)象。為此,在其前面,要增加模擬低通濾波器,把采樣頻率及其以上的高頻信號(hào)有效地排除。故又用一級(jí)MAX297,截止頻率設(shè)置為50kHz.其中時(shí)鐘頻率設(shè)置為2.5 MHz.在其后面,也要增加低通濾波器,其截止頻率為150 kHz,以濾去信號(hào)的高頻分量,使波形更加平滑。具體電路如圖4所示。

圖4 MAX297低通濾波

3.4 四階橢圓低通模塊

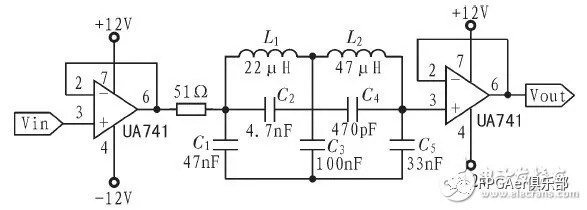

系統(tǒng)要求制作一個(gè)四階橢圓型低通濾波器,帶內(nèi)起伏≤1 dB,-3 dB通帶為50 kHz,采用無(wú)源LC橢圓低通濾波器來(lái)實(shí)現(xiàn)。用Filter Sol ution模擬仿真濾波器,隨后在MulTIsim中再模擬仿真并調(diào)整電容、電感的參數(shù)使其為標(biāo)稱值。此外,在橢圓濾波器前后接射級(jí)跟隨器避免前后級(jí)影岣。具體電路如圖5所示。

圖5 橢圓低通模塊

4 系統(tǒng)軟件設(shè)計(jì)

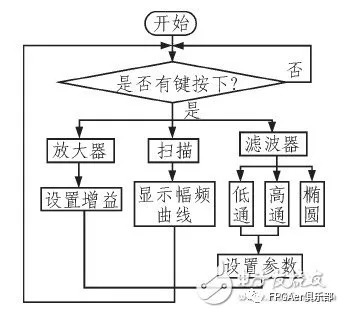

系統(tǒng)軟件設(shè)計(jì)由單片機(jī)和FPGA組成,用戶可以通過(guò)界面的顯示選擇高通、低通和橢圓濾波器,可以設(shè)置截止頻率,同時(shí)可以顯示幅頻曲線。其中單片機(jī)主要完成用戶的輸入輸出處理和系統(tǒng)控制,F(xiàn)PGA主要完成的功能有:控制AD9851產(chǎn)生掃頻信號(hào)、控制濾波器截止頻率的時(shí)鐘信號(hào)的產(chǎn)生以及控制兩塊D/A以顯示幅頻特性曲線。程序流程圖如圖6所示。

圖6 程序流程圖

5 測(cè)試方案與測(cè)試結(jié)果

5.1 放大器測(cè)試

放大器輸入端的正弦信號(hào)頻率為10 kHz,振幅為10 mV,設(shè)定增益大小分別為10、20、30、40、50、60dB,用示波器測(cè)量實(shí)際輸出幅值,計(jì)算出實(shí)際增益,其誤差小于1%.此外,測(cè)得放大器通頻帶為1~200kHz。

5.2 低通、高通濾波器測(cè)試

將放大器增益設(shè)置為40dB,濾波器設(shè)置為低通濾波器,預(yù)置濾波器截止頻率在1~30 kHz范圍,步進(jìn)為1kHz.用示波器測(cè)量實(shí)際截止頻率,計(jì)算相對(duì)誤差小于1.5%,且2fc處的電壓總增益小于20dB.高通濾波器測(cè)試方法同理。

5.3 橢圓濾波器測(cè)試

放大器增益設(shè)置為40 dB,用示波器測(cè)量實(shí)際-3 dB截止頻率和200 kHz處的總電壓增益。測(cè)得fc=50.0kHz,在150 kHz處幅度就已幾乎衰減到0.

5.4 幅頻特性與相頻特性測(cè)試

測(cè)量低通、高通濾波器的頻率特性,在示波器上顯示其幅頻特性曲線,與所設(shè)置的濾波模式及截止頻率相符。

6 結(jié)束語(yǔ)

本系統(tǒng)放大器增益范圍10~60 dB,通頻帶1~200 kHz,增益誤差小于1%.濾波器截止頻率范圍1~30kHz,誤差小于1.5%.橢圓濾波器截止頻率誤差為0,在150 kHz處幅度幾乎衰減到0.誤差主要于時(shí)鐘頻率,當(dāng)截止頻率為20 kHz的時(shí)候,所需最高的時(shí)鐘頻率為2MHz,不能保證很好的時(shí)鐘沿,而且時(shí)鐘頻率也不可能精確地控制,以及放大器的非線性誤差。此外,利用DAC0800和有效值檢波電路實(shí)現(xiàn)了幅頻特性測(cè)試儀,系統(tǒng)整體性能良好。整個(gè)系統(tǒng)在單片機(jī)和FPGA的有機(jī)結(jié)合、協(xié)同控制下,工作穩(wěn)定,測(cè)量精度高,人機(jī)交互靈活。

-

單片機(jī)

+關(guān)注

關(guān)注

6043文章

44621瀏覽量

638570 -

濾波器

+關(guān)注

關(guān)注

161文章

7860瀏覽量

178934

原文標(biāo)題:FPGA學(xué)習(xí)系列28,以FPGA為控制核心的程控濾波器設(shè)計(jì)

文章出處:【微信號(hào):FPGAer_Club,微信公眾號(hào):FPGAer俱樂(lè)部】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

解讀FPGA設(shè)計(jì)程控濾波器系統(tǒng)電路

基于AT89S52單片機(jī)的程控濾波器設(shè)計(jì)

基于51單片機(jī)和FPGA的程控濾波器的實(shí)現(xiàn)方案

一文帶你深度了解濾波器

基于FPGA的程控濾波器設(shè)計(jì)與實(shí)現(xiàn)

一種程控濾波器的設(shè)計(jì)

基于單片機(jī)和FPGA的程控濾波器的設(shè)計(jì)

程控濾波器的實(shí)現(xiàn)和濾波方案設(shè)計(jì)

基于LPC2138的二階程控濾波器設(shè)計(jì)

基于C8051F020的程控濾波器的實(shí)現(xiàn)

以FPGA為控制核心的程控濾波器設(shè)計(jì)

使用51單片機(jī)和FPGA為核心設(shè)計(jì)一個(gè)程控濾波器的設(shè)計(jì)報(bào)告免費(fèi)下載

一文帶你了解以FPGA為控制核心的程控濾波器設(shè)計(jì)

一文帶你了解以FPGA為控制核心的程控濾波器設(shè)計(jì)

評(píng)論