1 引言

在 IC 工藝中,金屬連線間的寄生電容除了取決于金屬間距、金屬厚度和連線寬度之外,還受金屬連線間的介質的介電常數的影響。在金屬刻蝕之后填充的介質材料(inter-metal dielectric)通常為二氧化硅,其介電常數介于 3.2~4.0 之間。隨著工藝節點的進步,金屬連線的線寬和間距越來越小,連線之間的寄生電容也越來越大,對電路性能的影響也隨之增大。而金屬線的厚度和連線之間的距離受工藝節點所限,一般不能夠任意變動。所以要實現更小的寄生電容,需要改變填充介質材料,以便得到較低的介電常數。在已知的物質中,干燥空氣的介電常數最低,可以借助在金屬連線間形成空氣隙的方式來降低金屬間介質的整體介電系數[1]。由于金屬連線間的寄生電容主要來自于在金屬之間正對著的區域,邊緣電容只占少比例。只需要在工藝制造過程中將空氣隙形成于金屬平板中間部分,其高度超過金屬連線高度即可。

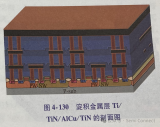

在已經量產的 0. 2μm RF-SOI 工藝中形成空氣隙的方法是進行金屬連線刻蝕,使金屬之間形成相互間隔的溝槽。為了在金屬連線之間形成盡可能大的空氣隙,通常利用填充性能較差的 PEFSG 作為填充材料。為了阻擋 PEFSG 中 F 的穿透作用,還需要先填充一層富硅氧化層(SRO)作為阻擋層。SRO的填充性能和 PEFSG 基本相同。在 0.20 μm 的工藝中,可以滿足要求。而在 0.13μm 工藝節點,當金屬連線間距小于 0.18 μm以后,側壁處的 SRO 阻擋層和 PEFSG 的厚度較薄,尤其在 Ti/TiN 臺階處對 Al的覆蓋不夠,并且還存在裂隙,會導致 PEFSG 中的 F 和金屬 Al 接觸反應,導致 Al 和 F 的生成物流動到空氣隙中,引發金屬連線短路(見圖 1)。所以如何改善金屬聯線側壁二氧化硅填充形貌是一個亟待解決的問題。

2 實驗方案

在射頻開管器件中,導通電阻和關斷電容是衡量射頻開管器件優良與否的關鍵參數。而后段金屬連線之間的電容對整體的關斷電容有直接影響[2,3]。

本文基于華虹宏力的 0.13μm RF-SOI 工藝平臺,對射頻開關器件中金屬連線間的空氣隙形成工藝進行了優化。射頻開關器件為叉指結構設計,源區和漏區分別通過金屬連線引出(見圖 2)。開關器件源漏之間的總電容由兩部分組成:分別是前段工藝中開關器件源漏電極與柵電極、源漏電極與襯底間的本征寄生電容,以及后段工藝中源漏金屬連線之間的寄生電容。在前段工藝保持不變的情況下,改變后段金屬連線間介質材料的填充工藝,測量得到的電容差異即為金屬連線間寄生電容的差異。在下一小節中我們將具體研究不同的填充工藝與材料對空氣隙的形成、以及最終對射頻開關器件關斷電容的影響。

3 實驗結果與討論

首先用 IC 工藝中常用的幾種二氧化硅填充材料進行了實驗,考量在不同金屬連線間距處的填充性能(分別為 0.18μm和 0.46μm)。其中 0.18μm 的對應于0.13μm 工藝的最小設計規則,即最小金屬連線間距,0.46μm 則對應于射頻開關源漏端叉指結構的金屬連線間距。具體試驗分批方案參見表 1。

我們需要找到不同金屬連線間距處填充一致性好的填充材料。也就是既要滿足 0.46μm 金屬間距處形成空氣隙降低寄生電容,又不能使最小金屬連線間距處臺階覆蓋能力不足而導致側壁保護不夠,同時需要小心調整填充材料和厚度達到兩者的平衡。對于更大的金屬連線間距甚至無窮遠的間距,由于空氣隙沒有實際作用,所以我們不予考慮。從圖 3 可以看出,對溝槽的填充能力從強到弱為:HDP > PETEOS > PEFSG = PEUSG。PETEOS 填充能力明顯強于 PEFSG和 PEUSG,并可以形成比較小的空氣隙。而 HDP 由于是邊填充邊在溝槽兩側上方減薄的方式,導致填充能力過強,完全沒有空氣隙。所以我們考慮先一層較薄的 PETEOS,利用其較強的填充能力作為金屬線側壁保護層,然后填充 PEUSG,利用其較弱的填充能力形成空氣隙。同時由于 USG 材料中不含 F 元素,還可以省略 SRO 阻擋層。

依據以上的實驗結果,我們確定了用 PETEOS+ PEUSG 作為填充材料。由于 4 000 ? 的 PETEOS 在 0.18μm 和 0.46μm 的金屬連線間距處已經將空氣隙封口,后續再填充 PEUSG 已經無效。所以我們選擇500 ?,1 000 ?,1 500 ? 和 2 000 ? PETEOS 作為實驗對照。具體試驗分批情況參見表 2。

從以上電子顯微鏡掃描照片可以看出增加 PETEOS厚度對金屬連線側壁覆蓋能力改善明顯。但是當PETEOS 厚度增加到 150 nm 甚至 200 nm 后,0.46 μm 金屬連線間距的空氣隙變小,并且抬高至金屬連線上方,這樣反而會使寄生電容增加。因此PETEOS 厚度介于 50 nm 和 100 nm 之間是比較理想的。我們最終選擇了厚度為 70μm 的 PETEOS 用來改善金屬連線側壁覆蓋形貌,厚度為 1 000 μm 的 PEUSG 用于形成空氣隙。多片晶圓多點電學測試結果表明,并沒有觀察到滿足最小設計規則的(0.18 μm )金屬連線間出現短路現象。

最后我們將新的填充工藝應用在射頻開關器件上,并測試了在關斷狀態下的 S12 參數,分批條件見表 3,測試結果見圖 5。其中條件 1 為原來的填充工藝。由于 PEFSG 和 PEUSG 本身的介電常數有差別,也加入了 PEFSG 實驗條件作為比對。從條件 2 和條件 3 的結果來看,使用 PEFSG和 PEUSG 填充對帶有空氣隙的金屬互聯電容基本沒有區別。我們同時也可以看出條件 3 中 70 nm 的 PETEOS與 650 nm PEUSG 的組合對整體電容的影響小于 3%,對射頻開關性能影響非常小。

4 結語

本文以射頻開關器件的應用為背景,提出了在 IC工藝節點變小之后,在不影響性能的基礎上改善金屬連線側壁填充的二氧化硅形貌的方法。通過分析和實驗,改善了最小金屬互聯間距處由于二氧化硅覆蓋不夠導致的短路問題。同時射頻器件源漏區域的大間距金屬連線處空氣隙仍然能高于金屬高度。并且實測了新的填充工藝的金屬互聯電容與原有的工藝之間的電容值差異,得到了比較理想的結果。

參考文獻

[1] B.Shieh,K.C.Saraswat,J.P.McVittie, S.List,S.Nag,M.Islamraja,R.H. Havemann.Air-gap formation during IMD deposition to lowerinterconnect capacitance[J].IEEE Electron Device letter,1998,19(01):16-18.

[2] R.Wolf,D.Wang,A.Joseph,A.Botula, P.Rabbeni,D.Harame,J.Dunn.Highly Resistive Substrate CMOS on SOI for Wireless Front-End Switch Application[C].CS MANTECH Conference, 2011,Palm Springs,California,USA.

[3] M.Jaffe,M.A.Khalil,A.Botula,J.E. Monaghan,J.Gambino,J.Gross,Z.X.He, A.Joseph,R.Phelps,S.Shank,J. Slinkman,R.Wolf.Improvements in SOI technology for RF switches[C].2015 IEEE 15th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, 2015:30-32.

-

集成電路

+關注

關注

5392文章

11624瀏覽量

363192 -

射頻開關

+關注

關注

7文章

81瀏覽量

20657

原文標題:金屬連線間形成空氣隙的改進工藝研究

文章出處:【微信號:appic-cn,微信公眾號:集成電路應用雜志】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種電磁型射頻微機電系統開關的軟磁懸臂梁制備工藝研究

MEMS開關缺陷的改進概述

射頻開關在高低溫電測試實驗的改進

開關電源pcb線間距規則

空氣的開關原理 空氣開關的安裝方式

半大馬士革工藝:利用空氣隙減少寄生電容

基于射頻開關器件的金屬連線間形成空氣隙的改進工藝研究

基于射頻開關器件的金屬連線間形成空氣隙的改進工藝研究

評論