一個8比特從設(shè)備

前文曾經(jīng)指出,Wishbone總線規(guī)范是"輕量級(Lightweight)"規(guī)范,它實現(xiàn)起來非常簡單緊湊,接口需要的互聯(lián)邏輯非常少。這里給出一個Wishbone從設(shè)備的一個例子,如圖21所示。該從設(shè)備由一個與門和8個D觸發(fā)器構(gòu)成。在寫周期,當(dāng)STB_I和WE_I同時有效,數(shù)據(jù)DAT_I[7:0]在時鐘CLK_I的上升沿被寫到觸發(fā)器中。

圖21 一個簡單的Wishbone從設(shè)備

該從設(shè)備的RTL代碼如下:

moduleslave8bit( inputCLK_I,//這里使用了Verilog2001語法 inputRST_I, input[7:0]DAT_I, inputSTB_I,inputWE_I, outputreg[7:0]DAT_O,outputACK_O); always@(posedgeCLK_IorposedgeRST_I) begin if(RST_I) begin DAT_O<=8'h00; ???????????????????????????end ???????????????????else?if(STB_I&WE_I) ???????????????????????????begin ??????????????????????????????????DAT_O<=DAT_I; ???????????????????????????end ???????????end ?????????? ????assign?ACK_O=STB_I; endmodule

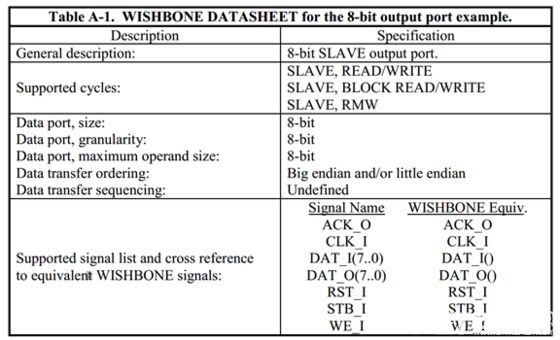

該從設(shè)備的Wishbone文檔如表5。

表5從設(shè)備的Wishbone文檔

一個32比特RTL級隨機(jī)數(shù)生成器從設(shè)備

下面我們舉一個實用一點的例子,一個隨機(jī)數(shù)生成器。隨機(jī)數(shù)生成理論和隨機(jī)數(shù)生成器隨機(jī)數(shù)生成理論和隨機(jī)數(shù)生成器模塊的RTL代碼見附錄2。該模塊端口定義如下:

module rng(clk,reset,loadseed_i,seed_i,number_o);

number_o為隨機(jī)數(shù)輸出,當(dāng)loadseed_I有效時,種子seed_I被送入number_o成為隨機(jī)數(shù)的第一個值。

我們的目的是將其包裝成WISHBONE兼容的從模塊,其Verilog RTL代碼如下:

moduleRng_wbc( inputCLK_I, inputRST_I, input[31:0]DAT_I, inputSTB_I,inputWE_I, input[3:0]SEL_I, output[31:0]DAT_O,outputACK_O); assignACK_O=STB_I; wireloadseed=WE_I&STB_I&(|SEL_I); wire[31:0]seed; assignseed[7:0]=SEL_I[0]?DAT_I[7:0]:8'h00; assignseed[15:8]=SEL_I[1]?DAT_I[15:8]:8'h00; assignseed[23:16]=SEL_I[2]?DAT_I[23:16]:8'h00; assignseed[31:24]=SEL_I[3]?DAT_I[31:24]:8'h00; wire[31:0]rand_number; assignDAT_O[7:0]=SEL_I[0]?rand_number[7:0]:8'h00; assignDAT_O[15:8]=SEL_I[1]?rand_number[15:8]:8'h00; assignDAT_O[23:16]=SEL_I[2]?rand_number[23:16]:8'h00; assignDAT_O[31:24]=SEL_I[3]?rand_number[31:24]:8'h00; //隨機(jī)數(shù)生成器的莉化 rngunit_rng(.clk(CLK_I),.reset(RST_I), .loadseed_i(loadseed),.seed_i(seed), .number_o(rand_number)); endmodule

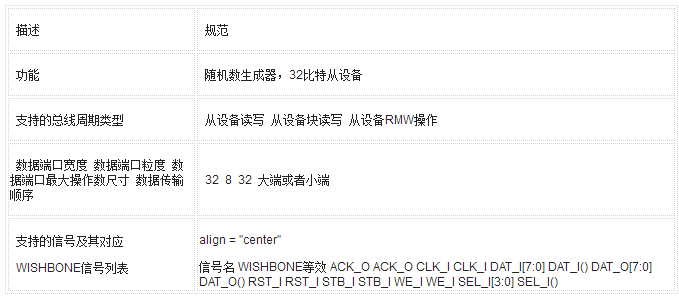

該從設(shè)備的Wishbone文檔如表6。

表6從設(shè)備的Wishbone文檔

-

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2003瀏覽量

61349 -

Wishbone

+關(guān)注

關(guān)注

0文章

16瀏覽量

10444

原文標(biāo)題:【博文連載】Wishbone總線從設(shè)備接口示例

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何在不改變RTL代碼的情況下,優(yōu)化FPGA HLS設(shè)計

wishbone總線

基于WISHBONE總線的FLASH閃存接口設(shè)計

AXI互連RTL將1個從設(shè)備連接到2個主設(shè)備怎么實現(xiàn)?

基于Wishbone總線的UART IP核設(shè)計

基于WISHBONE總線的FLASH閃存接口設(shè)計

設(shè)計復(fù)用的RTL指導(dǎo)原則

HLS系列 – High Level Synthesis(HLS) 從一個最簡單的fir濾波器開始2

用Elaborated Design優(yōu)化RTL的代碼

python設(shè)計一個簡單推薦系統(tǒng)的資料和完整代碼

從RTL追蹤到Scala

一個簡單的RTL同步FIFO設(shè)計

一個簡單的設(shè)備激活器電路

一個簡單的Wishbone從設(shè)備的RTL代碼

一個簡單的Wishbone從設(shè)備的RTL代碼

評論