聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1630文章

21797瀏覽量

606012 -

Altera

+關(guān)注

關(guān)注

37文章

787瀏覽量

154172 -

系統(tǒng)性能

+關(guān)注

關(guān)注

0文章

8瀏覽量

6474

發(fā)布評論請先 登錄

相關(guān)推薦

SoC FPGA有哪些作用?

Altera公司意欲通過更先進(jìn)的制程工藝和更緊密的產(chǎn)業(yè)合作,正逐步強(qiáng)化FPGA協(xié)同處理器,大幅提升SoC FPGA的整體性能,為搶攻嵌入式系統(tǒng)

發(fā)表于 08-26 07:15

鏡像對系統(tǒng)性能的影響有哪些?

鏡像抑制基礎(chǔ)知識可減少AD9361和AD9371中正交不平衡的技術(shù)鏡像的來源、含義及對系統(tǒng)性能的影響

發(fā)表于 03-29 07:59

如何提高FPGA的系統(tǒng)性能

本文基于Viitex-5 LX110驗證平臺的設(shè)計,探索了高性能FPGA硬件系統(tǒng)設(shè)計的一般性方法及流程,以提高FPGA的系統(tǒng)性能。

發(fā)表于 04-26 06:43

基于SoC的數(shù)字?jǐn)z像系統(tǒng)

重點介紹基于SoC的數(shù)字?jǐn)z像系統(tǒng)的工作原理和內(nèi)部電路。 最后對其芯片和系統(tǒng)性能進(jìn)行簡要說明。

發(fā)表于 04-08 09:47

?12次下載

優(yōu)化BIOS設(shè)置提高系統(tǒng)性能

BIOS設(shè)置對系統(tǒng)性能的影響非常大,優(yōu)化的BIOS設(shè)置,可大大提高PC整體性能,不恰當(dāng)?shù)脑O(shè)置會導(dǎo)致系統(tǒng)性能下降,運行不穩(wěn)定,甚至出現(xiàn)死機(jī)等現(xiàn)象。下面就BIOS中影響系統(tǒng)性能選

發(fā)表于 10-10 14:27

?43次下載

基于FPGA的SOC系統(tǒng)中的串口設(shè)計

基于FPGA 的SOC 系統(tǒng)中的串口設(shè)計

作者:葛銳 歐鋼摘要:本文在XILINX FPGA 中采用嵌入式處理器Picoblaze 進(jìn)行SOC

發(fā)表于 02-08 09:48

?21次下載

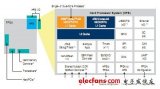

Altera公司SoC FPGA 簡介

本文是關(guān)于Altera公司SoC FPGA 的用戶手冊(英文版) 。文中主要介紹了什么是SoC FPGA、

發(fā)表于 09-05 14:03

?153次下載

based SmartFusion2 SoC FPGA設(shè)計的System Builder設(shè)計工具

時間 美高森美公司(Microsemi) 宣布SmartFusion 2 SoC FPGA用戶現(xiàn)在可以獲益于其新近發(fā)布的系統(tǒng)創(chuàng)建器(System Builder)設(shè)計工具。System

發(fā)表于 09-25 09:07

?686次閱讀

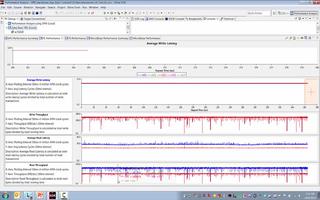

Xilinx SDK的系統(tǒng)性能分析工具技介紹

了解SDK中的系統(tǒng)性能分析工具,以對系統(tǒng)進(jìn)行建模,測量,分析和優(yōu)化。

SDK中的工具允許您對系統(tǒng)中的數(shù)據(jù)進(jìn)行檢測和可視化,以實現(xiàn)最佳性能。

如何提高GSPS和寬帶RF的系統(tǒng)性能

您是一個尋求在無需交錯或移除令人頭痛的信號偽像的前提下,提升系統(tǒng)性能的FPGA或雷達(dá)、無線基礎(chǔ)設(shè)施和儀器儀表設(shè)計師嗎? 在高速轉(zhuǎn)換中,分辨率或采樣速率很重要,但它們并非設(shè)計師在設(shè)計中需要考慮的唯一

發(fā)表于 09-24 10:45

?0次下載

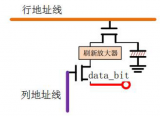

新手必看!FPGA的系統(tǒng)性學(xué)習(xí)

本系列將帶來FPGA的系統(tǒng)性學(xué)習(xí),從最基本的數(shù)字電路基礎(chǔ)開始,最詳細(xì)操作步驟,最直白的言語描述,手把手的傻瓜式講解,讓電子、信息、通信類專業(yè)學(xué)生、初入職場小白及打算進(jìn)階提升的職業(yè)開發(fā)者都可以有系統(tǒng)性

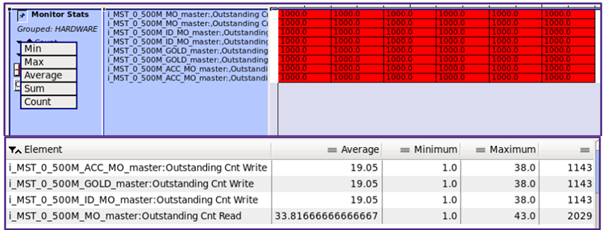

使用Synopsys智能監(jiān)視器提高Arm SoC的系統(tǒng)性能

在使用 AXI 總線移動大量數(shù)據(jù)的 SoC 中,AXI 總線的性能可能會成為整體系統(tǒng)性能的瓶頸。SoC 中日益增加的復(fù)雜性和軟件內(nèi)容,因此需要使用實際數(shù)據(jù)有效載荷在硅前進(jìn)行左移

介紹SoC FPGA系統(tǒng)性能(2)

介紹SoC FPGA系統(tǒng)性能(2)

評論