FD-SOI

若要說2018以及未來五年最受矚目的半導體工藝技術,除了即將量產的7納米FinFET尖端工藝,以及預計將全面導入極紫外光(EUV)微影技術的5納米工藝節點,各家晶圓代工業者著眼于應用廣泛、無所不包的物聯網(IoT)市場對低功耗、低成本組件需求而推出的各種中低階工藝技術選項,也是產業界的關注焦點。

例如晶圓代工龍頭臺積電(TSMC)的16與12納米FFC (FinFET Compact Technology)、22納米超低功耗(ULP)、28納米HPC/HPC+,以及40納米ULP、55納米ULP與低功耗(LP)等邏輯工藝,還有英特爾(Intel)的22納米低功耗FinFET (22FFL)工藝、GlobalFoundries的28納米HPP (High Performance Plus)/SLP (Super Low Power)、22FDX工藝,以及三星電子(Samsung)的28納米FDSOI、LPP、LPH…等等,都是適合廣泛物聯網應用市場需求特性的解決方案。

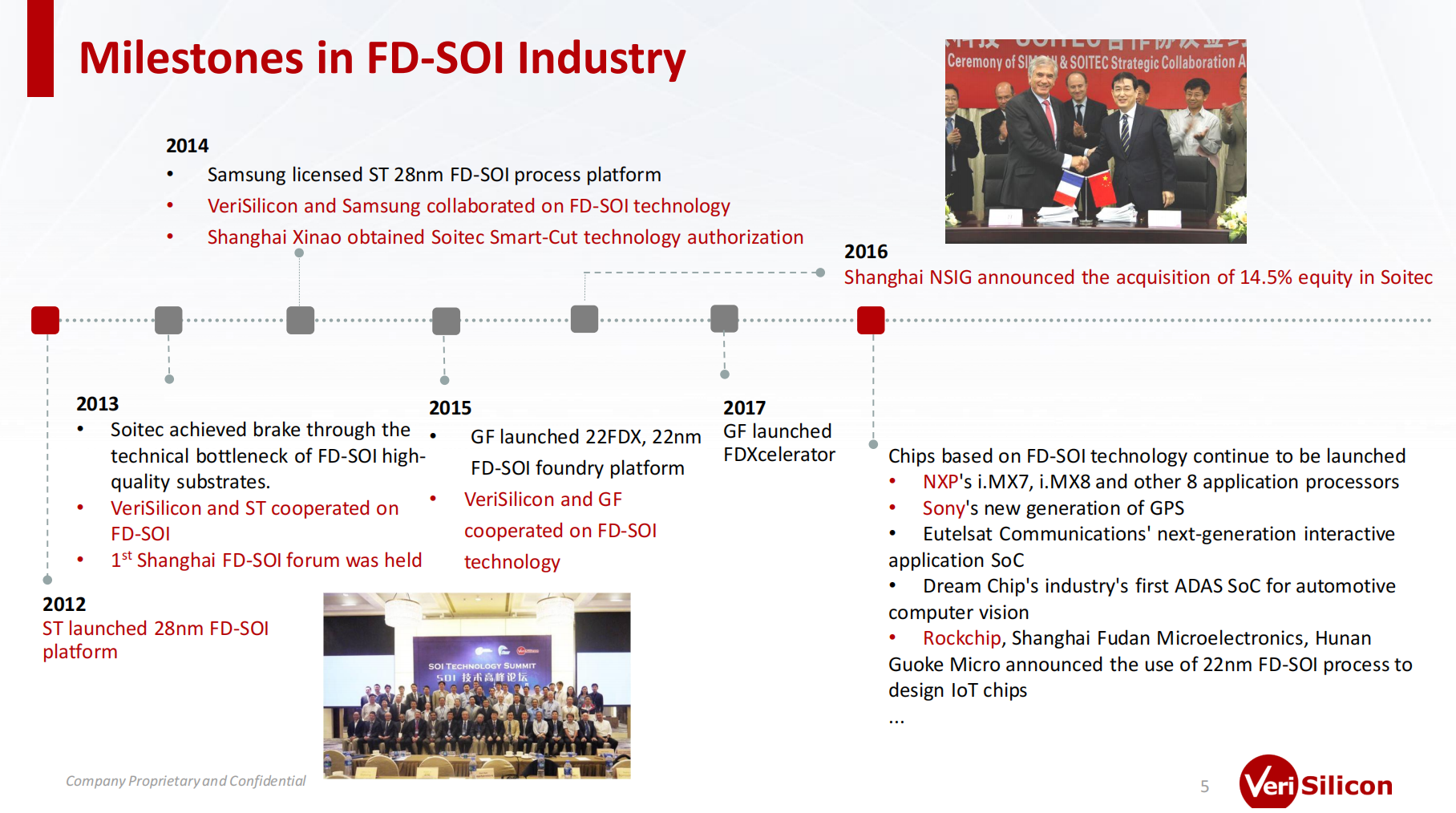

其中GlobalFoundries的FDX系列工藝與Samsung的FD-SOI工藝,與其他競爭方案之間的最大差異,就在于采用了無論是英文或中文讀來都十分拗口的“全空乏絕緣上覆硅”(Fully Depleted Silicon On Insulator,FD-SOI)技術;該技術早在2011年就由SOI產業聯盟(SOI Industry Consortium)、意法半導體(ST)以及其研發伙伴IBM、GlobalFoundries、三星等率先在業界推廣,號稱在28納米與20 (22)納米節點能達到由英特爾、臺積電等支持的新一代FinFET工藝相當的性能,但成本與風險更低。

FD-SOI技術優勢何在?

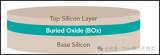

不同于FinFET工藝采用的3D晶體管結構,FD-SOI為平面工藝;根據ST官網上的技術資料,FD-SOI有兩大主要創新:首先是采用了埋入氧化物(buried oxide,BOX)超薄絕緣層,放置于硅基板之上;接著將超薄的硅薄膜布署于晶體管通道,因為其超薄厚度,通道不需要摻雜(dope),使晶體管能達到完全空乏。以上兩種創新技術的結合全名為“超薄基體埋入氧化層全空乏絕緣上覆硅”(ultra-thin body and buried oxide FD-SOI,UTBB-FD-SOI)。

ST表示,與傳統的塊狀硅技術相較,FD-SOI能提供更好的晶體管靜電特性,而埋入氧化層能降低源極(source)與汲極(drain)之間的寄生電容;此外該技術能有效限制源極與汲極之間的電子流動,大幅降低影響組件性能的泄漏電流(圖1)。除了透過閘極,FD-SOI也能藉由極化(polarizing)組件底層基板來控制晶體管行為,類似于塊狀硅技術亦可實現的基體偏壓(body bias)。

圖1:塊狀硅工藝與FD-SOI工藝晶體管結構比較(來源:STMicroelectronics)

不過塊狀硅技術的基體偏壓非常有限,因為寄生漏電流以及晶體管幾何尺寸縮減之后晶體管效率降低;而FD-SOI因為晶體管結構以及超薄絕緣層,偏壓效率會更好。此外,埋入氧化層也能實現更高的基體偏壓,達到對晶體管突破性的動態控制──當基板的極化為正向,也就是順向基體偏壓(FBB),晶體管切換速度能加快,并因此能優化組件性能與功耗。

根據ST的說法,FD-SOI能輕易實現FBB并在晶體管運作期間進行動態調節,為設計工程師提供高度彈性,特別是對省電性能與速度有高度要求、性能并非關鍵的組件,因此是物聯網或便攜式/可穿戴消費性電子設備應用的理想解決方案。

市場研究機構International Business Strategies (IBS)首席執行官Handel Jones在2014年發表的一份報告中寫道:“同樣是100mm見方大小的芯片,采用28納米FD-SOI工藝的成本比塊狀CMOS工藝低3%,在20納米節點則可以進一步低30%;這是因為帶來更高參數良率的同時,晶圓成本也更低;”此外FD-SOI工藝裸晶的復雜度與塊狀CMOS工藝比較,低了10%~12%。

Jones進一步表示:“更小的裸晶面積與更高的參數良率之結合,FD-SOI工藝在20納米節點的產品成本優勢會比塊狀CMOS工藝多20%;在28納米節點,FD-SOI的性能則比20納米塊狀CMOS高出15%。”他并指出:“FD-SOI工藝在高/低Vdd方面能提供比塊狀CMOS工藝更高的能源效率等級(energy efficiency levels);FD-SOI在位單元(bit cells)上的電源效率也高出塊狀CMOS,這是因為較低的泄漏電流以及對α粒子更好的免疫力。”

FD-SOI工藝:西方冷、東方熱

不過盡管FD-SOI號稱有上述諸多優勢,對于該工藝的生產良率、專用晶圓片價格與供應來源穩定性,還有大量生產確切時程、整體技術支持生態系統完整性,產業界仍有諸多疑慮;因此雖然FD-SOI在歐洲有ST、恩智浦(NXP)等支持者,三星、GlobalFoundries等也分別積極推廣自家FD-SOI代工業務,該技術在市場的討論熱度與能見度一直偏低,特別是在西方。

時間來到2017年2月,GlobalFoundries宣布投資100億美元在中國成都高新西區建立12吋晶圓廠(圖2),2018年開始營運的第一期生產線會是轉移自該公司新加坡廠之為較成熟的180/130納米工藝,第二期為轉移自其德國德累斯頓 (Dresden)廠的22FDX FD-SOI工藝生產線,預計2019年開始營運;此訊息在半導體產業界引起廣大回響,除了再次昭示了中國發展本土半導體產業鏈的企圖心,也代表FD-SOI工藝的“主戰線”將在中國點燃。

圖2:Globalfoundries在中國成都興建12吋廠Fab 11,預計2019年量產的第二階段生產線為22FDX FD-SOI工藝(來源:Globalfoundries)

中國早在2015年就對FD-SOI技術表達了高度興趣;當時IC設計服務業者芯原(VeriSilicon)首席執行官戴偉民(Wayne Dai)在接受EE Times記者訪問時即表示,與其不斷地在FinFET工藝方面追趕臺積電或英特爾的腳步,他認為中國應該投資FD-SOI,并以該技術做為低功耗工藝的替代方案。此外上海新傲科技(Simgui)于2015年秋天開始量產首批8吋SOI晶圓片,采用與該公司策略伙伴、法國業者Soitec的Smart Cut工藝技術。

還有一個由中國“大基金”成立的投資平臺,上海硅產業投資有限公司(National Silicon Industry Group,NSIG)在2016年宣布收購14.5%的Soitec股權;晶圓代工業者上海華力微電子(Shanghai Huali Microelectronics Corp.)在GlobalFoundries宣布成都廠投資計劃前,也透露了投資FD-SOI生產線的計劃,但并沒有具體時間表。這些跡象在顯示FD-SOI將會是中國半導體產業發展藍圖的一部分,并可能讓這個迄今在西方世界市場稍嫌受到冷遇的技術,在東方市場發光發熱。

根據Globalfoundries產品管理資深副總裁Alain Mutricy在2017年5月接受EE Times采訪時的說法,該公司在成都投資設廠只是第一步,接下來還將在當地建立FD-SOI生態系統,幫助中國無晶圓廠IC設計業者以及設計服務業者更容易取得所需的IP與工具。

物聯網工藝戰火即將引爆

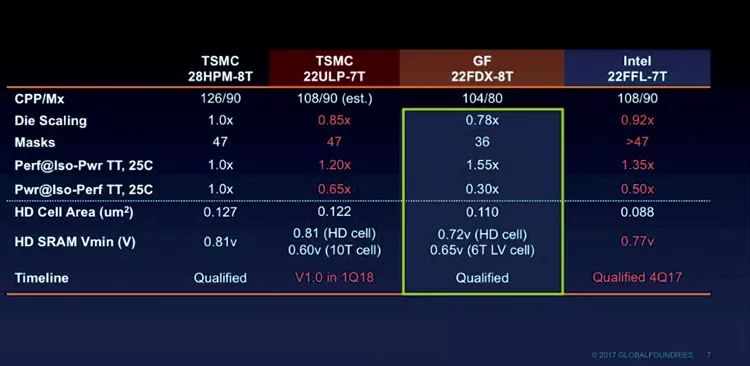

2017年9月底,在SOI產業聯盟主辦的第五屆上海FD-SOI論壇上,發表專題演說的GlobalFoundries首席執行官Sanjay Jha再次大力宣傳FD-SOI工藝,并以22納米──采用單次光罩最小節點,也是適合物聯網、便攜設備等對成本/功耗敏感應用,預期將會是市場上的“長壽”節點──為基準,將該公司的22FDX工藝以及英特爾22FFL工藝、臺積電22ULP工藝的性能比較(圖3)。

圖3:GlobalFoundries、臺積電與英特爾的22納米工藝性能比較(來源:GlobalFoundries)

Jha在接受訪問時表示:“從成本上面來說,22納米FinFET如果采用平面技術,工藝步驟會多一些,工藝控制的復雜度很高。對于FDX,底層的基板成本可能會高一點。確實很難模擬各自成本的結構,但是考慮到我們在中國晶圓廠的建設投資以及規模產生的成本效應,從生產的成本來說,相較于英特爾的技術,可能略有優勢。”

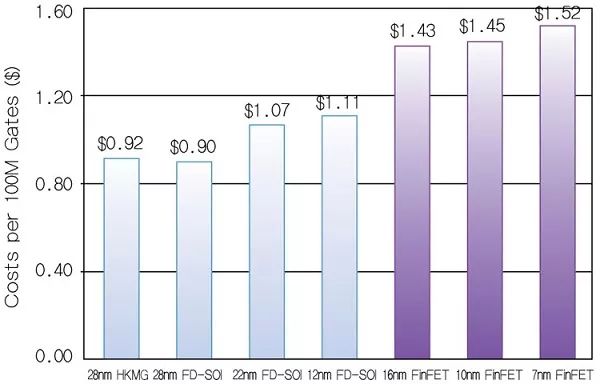

IBS首席執行官Jones也進一步提出了FD-SOI工藝的閘極成本(cost per gate)分析(圖4),他指出,28納米FD-SOI工藝與28納米高介電金屬閘極(HKMG)塊狀CMOS的閘極成本相當,22納米FD-SOI的閘極成本也仍具競爭力;而到了下一代的12納米FD-SOI,因為所需光罩層數較少,閘極成本會比16納米FinFET工藝低22.4%,比10納米FinFET低23.4%,比7納米FinFET低27%,而FD-SOI的低耗電表現當然也優于FinFET。

圖4:FD-SOI與FinFET工藝閘極成本比較(來源:IBS)

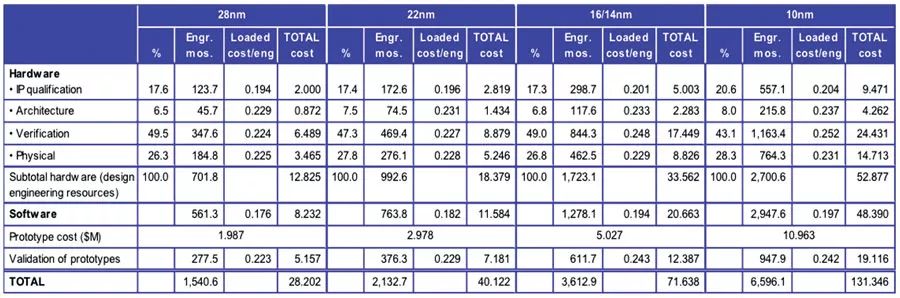

此外Jones也提出了各工藝節點的軟硬件設計成本比較(圖5),估計12納米FD-SOI的設計成本在5,000至5,500萬美元之間,而16納米FinFET設計成本在7,200萬美元左右,10納米FinFET設計成本在1.31億美元左右;因為設計成果的營收需要是成本的10倍,所以12納米FD-SOI的潛在市場規模(TAM)會比16納米與10納米FinFET更大。

圖5:各工藝節點設計成本比較(來源:IBS)

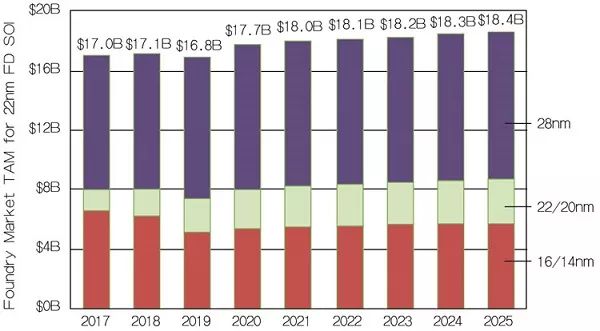

綜合FD-SOI低功耗、易于整合RF等特性與成本上的優勢,GlobalFoundries將移動設備、物聯網、無線通信(5G/LTE/Wi-Fi),以及汽車(ADAS/車用通信)視為該工藝的熱門應用;Jones則認為,現有28納米工藝組件中,有九成都適合轉向FD-SOI工藝,其TAM規模在2018年估計達到171億美元(圖6),到2025年甚至可達184億美元,眾家FD-SOI技術供應商能實際取得多少營收得各憑本事,而鎖定物聯網市場商機的工藝大戰已經煙硝四起。

圖6:22納米FD-SOI工藝潛在市場規模預測(來源:IBS)

大陸IC廠商躍躍欲試,***廠商呢?

根據GlobalFoundries在第五屆上海FD-SOI論壇提供的統計數字,該公司的22FDX工藝已經獲得了總計135家客戶的青睞,其中有20家客戶會在2017年底之前進入多項目晶圓(MPW)試產、這之中又有15家會在2018年底正式投片,而進入測試設計/投片階段的這些客戶中,包括10家來自中國的廠商。

GlobalFoundries于2017年2月宣布于成都興建投資額達百億美元的12吋新廠之后,又于同年5月與成都市政府共同宣布,雙方將合作以6年時間建立一個累計投資規模超過1億美元的“世界級的FD-SOI生態系統”,涵蓋多個位于成都的研發中心以及與大學院校合作的研究項目,目的是能吸引更多頂尖半導體業者落戶成都,并使成都“成為下一代芯片設計的卓越中心”。

將加入成都FD-SOI生態系統的公司包括EDA供應商Cadence、Synopsys,設計服務業者芯原、Invecas,還有芯片設計業者聯發科(MediaTek)、瑞芯微(RockChip)、上海復旦微電子(Shanghai Fudan Microelectronics Group Company)等等;芯原的戴偉民在接受EE Times訪問時表示,要從成都FD-SOI生態系統投資中獲得研發經費,“每一家公司都必須在成都部署研發團隊。”

戴偉民指出,FD-SOI的支持者已經在中國打好基礎,藉由像是上海FD-SOI論壇這樣的活動,持續向中國本地的芯片業者與IC設計工程師、政府官員、私人投資基金等大力宣傳;而他認為,要壯大中國的FD-SOI生態系統有幾個要點,包括:使用FD-SOI實現混合信號和RF設計的可行性、設計服務業者(如芯原)的支持、實現基體偏壓設計流程和工具,還有設計教學、研討會、大學課程、實驗室和教科書,以及政府的支持。

中國IC業者對FD-SOI技術躍躍欲試,當地的產業生態系統逐漸成形;以全球來看,GlobalFoundries則表示其FD-SOI工藝生態系統FDXcelerator的合作伙伴截至2017年9月已經達到33家(圖7),涵蓋半導體產業鏈上下游業者。盡管占據十分少數,***業者也在其中,包括封測大廠日月光(ASE)、嵌入式內存IP供應商力旺電子(eMemory),以及處理器IP供應商晶心科技(Andes)。

圖7:GlobalFoundries積極為FD-SOI工藝建立產業生態系統(來源:GlobalFoundries)

晶心科技總經理林志明接受采訪時表示,該公司是在2015年與GlobalFoundries的長期伙伴、美國IC設計服務業者Invecas合作,將其32位N7處理器核心導入采用FD-SOI工藝的參考設計,后來也獲得了GlobalFoundries的22FDX工藝驗證。

他指出,晶心的處理器核心開發原本就是以低功耗、高效率為要求,其N7、N8與N9等系列都已經在物聯網與便攜式消費性電子市場獲得采用,進駐包括智能手表、智能語音助理、游戲機以及隨身卡拉OK麥克風等等裝置,目標市場與FD-SOI技術的方向一致,以此工藝選項搭配晶心的IP,可望為客戶的設計帶來更佳的省電效能。

圖8:晶心科技總經理林志明:FD-SOI工藝的終端目標市場正好與我們的產品線非常一致

***地區的半導體IP供應商并未在FD-SOI生態系統中缺席,但***IC設計業者何時會跟進?除了已經準備加入成都FD-SOI生態系統的聯發科技,***本地業者對此技術的態度與西方市場一樣偏冷;如半導體測試實驗室宜特科技(iST)表示,據了解正在嘗試FD-SOI設計的***地區IC業者仍在少數,預期對該工藝的接受速度會比中國大陸業者緩慢得多。

結語

市場研究機構集邦科技(TrendForce)旗下拓墣產業研究所半導體研究中心分析師黃志宇表示,目前全球FD-SOI產能的統計數字不易取得,僅能大略估計該工藝占據2017年全球晶圓代工銷售的比例為0.2%左右;他并指出,中國大陸積極建立FD-SOI產業鏈,引進晶圓片制造商Soitec、晶圓代工業者GlobalFoundries,對***地區晶圓代工業者的28納米工藝競爭力可能會帶來沖擊。

不過黃志宇也指出,觀察中國FD-SOI產能開出的時間點亦相當重要,必須同時考慮市場上既有晶圓代工業者的28納米工藝的折舊情形以及FD-SOI的實際產能規模:“當FD-SOI工藝產能規模小、成本就相對變高,而若晶圓代工業者折舊情形良好、將可提供更優惠的28納米工藝價格,如此在以成本導向的終端產品競爭上,FD-SOI就未必有利。”

28納米工藝可說是***晶圓代工雙雄聯電(UMC)、臺積電的“搖錢樹”,其中臺積電在2017年的28納米晶圓片出貨量創下了18萬片的新高紀錄,該節點營收在臺積電2017年第三季仍然是占據當季整體營收最高比例、達到27%,高于先進的16/20納米節點;聯電則在第三季看到28納米HKMG的市場需求趨緩。

來勢洶洶的FD-SOI工藝將會對現有28納米晶圓代工市場帶來什么樣的影響?中國半導體產業是否將因為FD-SOI技術的發展而改寫歷史?臺積電即將開出的22納米新工藝又是否能取得市場動力?為物聯網市場商機,聯電在28納米工藝之后又將祭出甚么新“武器”?2018年半導體市場的發展局勢值得陸續觀察!

-

物聯網

+關注

關注

2913文章

44928瀏覽量

377053 -

FD-SOI

+關注

關注

2文章

46瀏覽量

21787

原文標題:FD-SOI技術優勢何在?戰火即將引爆

文章出處:【微信號:RF_Semiconductor,微信公眾號:射頻半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Quobly宣布容錯量子計算技術重大突破

FD-SOI成≥12nm和≤28nm區間更好的選擇,三星、格羅方德等公司如何布局?

解讀芯原股份基于FD-SOI的RF IP技術平臺:讓SoC實現更好的通信

三星電子:18FDS將成為物聯網和MCU領域的重要工藝

設計中標收入已逾20億美元,格羅方德FDX下一步如何走?

IBS首席執行官再談FD-SOI對AI的重要性,在≥12nm和≤28nm區間FD-SOI是更好的選擇

芯原戴偉民博士回顧FD-SOI發展歷程并分享市場前沿技術

HPLC智能電表有什么技術優勢嗎?

FD-SOI技術優勢何在?物聯網工藝戰火即將引爆

FD-SOI技術優勢何在?物聯網工藝戰火即將引爆

評論