大家好,又到了每日學(xué)習(xí)的時(shí)候了。今天我們來(lái)聊一聊異步電路中的時(shí)鐘同步處理方法。

既然說(shuō)到了時(shí)鐘的同步處理,那么什么是時(shí)鐘的同步處理?那首先我們就來(lái)了解一下。

時(shí)鐘是數(shù)字電路中所有信號(hào)的參考,沒(méi)有時(shí)鐘或者時(shí)鐘信號(hào)處理不得當(dāng),都會(huì)影響系統(tǒng)的性能甚至功能,所以在一般情況下,我們?cè)谕粋€(gè)設(shè)計(jì)中使用同一個(gè)時(shí)鐘源,當(dāng)系統(tǒng)中有多個(gè)時(shí)鐘時(shí),需要根據(jù)不同情況選擇不同的處理方法,將所有的時(shí)鐘進(jìn)行同步處理,下面分幾種情況介紹時(shí)鐘的同步處理方法。

******************************************************************************************************************************************************

一、當(dāng)有多個(gè)時(shí)鐘在同一個(gè)數(shù)字電路中,且有一個(gè)時(shí)鐘(假設(shè)為SysClk)的速率大于其它時(shí)鐘兩倍以上

這種情況最為簡(jiǎn)單,我們?cè)?a target="_blank">接口部分就必須要對(duì)其他時(shí)鐘進(jìn)行同步化處理,將其處理為與SysClk同步的時(shí)鐘信號(hào)。這樣處理的好處是:

1. 便于處理電路內(nèi)部時(shí)序;

2. 時(shí)鐘間邊界條件只在接口部分電路進(jìn)行處理。

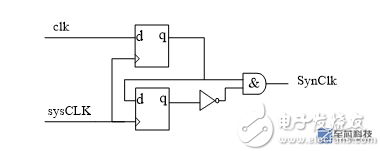

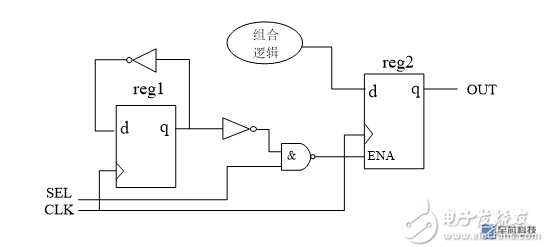

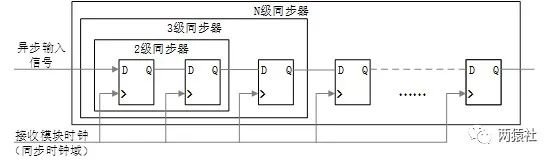

一般的時(shí)鐘同步化方法如下圖所示。

實(shí)質(zhì)上,時(shí)鐘采樣的同步處理方法就是上升沿提取電路,經(jīng)過(guò)上升沿提取輸出信息中,帶有了系統(tǒng)時(shí)鐘的信息,所以有利于保障電路的可靠性和可移植性。

******************************************************************************************************************************************************

二、當(dāng)系統(tǒng)中所有時(shí)鐘沒(méi)有一個(gè)時(shí)鐘速率達(dá)到其他時(shí)鐘頻率的兩倍的情況,也就是系統(tǒng)中多個(gè)時(shí)鐘速率差不多的情況

這個(gè)時(shí)候無(wú)法滿足采樣定理,所以在接口部分就必須對(duì)其他時(shí)鐘和數(shù)據(jù)通過(guò)FIFO進(jìn)行隔離,并將其他時(shí)鐘信息轉(zhuǎn)換為和系統(tǒng)時(shí)鐘同步的允許信號(hào)。比如在高速的數(shù)據(jù)采集系統(tǒng)當(dāng)中,AD的采集時(shí)鐘往往比較高,大于系統(tǒng)時(shí)鐘的一半以上,這時(shí)候采用同步化處理無(wú)法滿足時(shí)序設(shè)計(jì)。

******************************************************************************************************************************************************

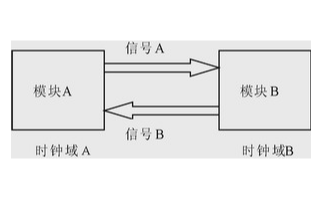

三、系統(tǒng)中多個(gè)時(shí)鐘之間存在數(shù)據(jù)互相采樣

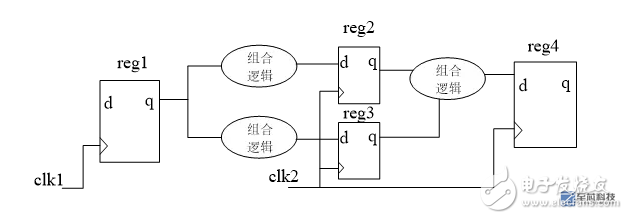

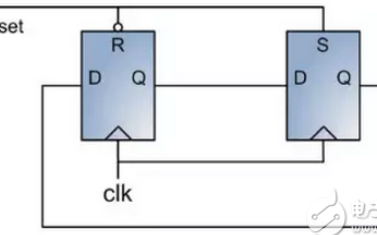

如下圖所示的情況。clk1和clk2來(lái)自不同的時(shí)鐘源,該電路即可能出現(xiàn)在同一芯片里,也可能出現(xiàn)在不同的芯片里,但是都存在同樣的危險(xiǎn)性。由于時(shí)鐘源不同,對(duì)于寄存器reg2和reg3來(lái)說(shuō),在同一時(shí)刻,極有可能一個(gè)認(rèn)為reg1輸出為“1”,另一個(gè)認(rèn)為是“0”,必然導(dǎo)致電路結(jié)果的錯(cuò)誤。

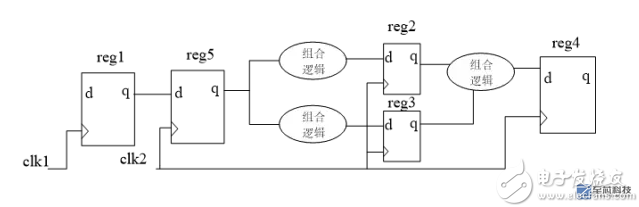

對(duì)于這種電路,我們必須在reg1之后再添加一個(gè)觸發(fā)器,用clk2的時(shí)鐘沿進(jìn)行采樣,然后用該觸發(fā)器的輸出經(jīng)過(guò)組合邏輯輸出到reg2和reg3當(dāng)中,如下圖所示。

*************************************************************************************************************************

四、多級(jí)時(shí)鐘或多級(jí)時(shí)鐘網(wǎng)絡(luò)處理

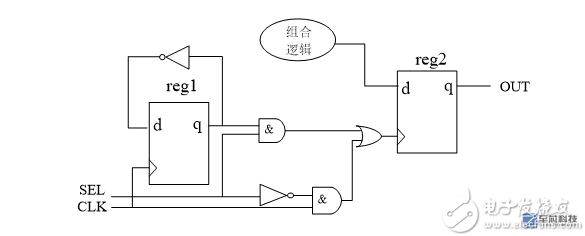

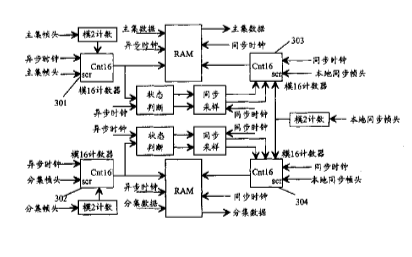

由于時(shí)鐘建立-保持時(shí)間的限制,FPGA設(shè)計(jì)中應(yīng)盡量避免采用多時(shí)鐘網(wǎng)絡(luò),或者盡量減少時(shí)鐘的個(gè)數(shù),所以在FPGA對(duì)ASIC芯片進(jìn)行驗(yàn)證的時(shí)候,我們必須要將時(shí)鐘網(wǎng)絡(luò)進(jìn)行簡(jiǎn)化,因?yàn)镕PGA內(nèi)部時(shí)鐘資源不像ASIC一樣具有很強(qiáng)的穿透性和靈活性。下圖為一個(gè)含有危險(xiǎn)的多級(jí)時(shí)鐘的例子,多路選擇器的輸入是clk和clk的2分頻,時(shí)鐘由SEL引腳控制的多路選擇器輸出,在這兩個(gè)時(shí)鐘均為邏輯“1”時(shí),當(dāng)SEL的狀態(tài)改變時(shí),存在靜態(tài)冒險(xiǎn)競(jìng)爭(zhēng)現(xiàn)象。

所以為了確保電路的正常工作,需要進(jìn)行修改,修改之后的電路如下圖所示。

今天就聊到這里,各位,繼續(xù)加油!

-

異步電路

+關(guān)注

關(guān)注

2文章

48瀏覽量

11149

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

簡(jiǎn)談同步復(fù)位和異步復(fù)位

簡(jiǎn)談異步電路中的時(shí)鐘同步處理方法

簡(jiǎn)談異步電路中的時(shí)鐘同步處理方法

FPGA設(shè)計(jì)中的異步復(fù)位同步釋放問(wèn)題

簡(jiǎn)談同步復(fù)位和異步復(fù)位

多時(shí)鐘域的同步時(shí)序設(shè)計(jì)和幾種處理異步時(shí)鐘域接口的方法

IC設(shè)計(jì)中同步復(fù)位與異步復(fù)位的區(qū)別

如何將一種異步時(shí)鐘域轉(zhuǎn)換成同步時(shí)鐘域

異步時(shí)鐘的同步處理

簡(jiǎn)談異步電路中的時(shí)鐘同步處理方法

簡(jiǎn)談異步電路中的時(shí)鐘同步處理方法

評(píng)論