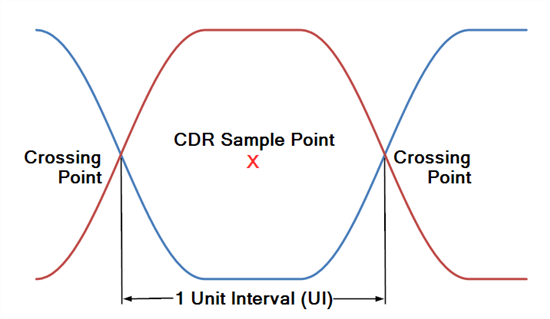

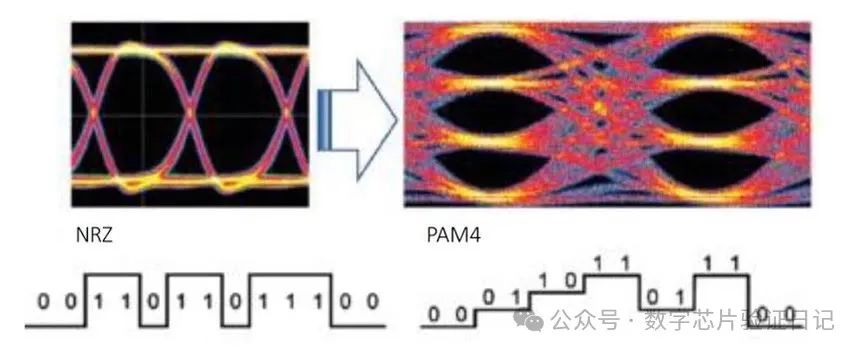

要理解抖動,我們首先要了解眼狀圖。眼狀圖是數字信號在時域中的表現形式,其中電壓振幅按時間變化繪制。一長串數據可分割成多個片段,稱之為單位間隔 (UI),這些 UI 在示波器上一個個疊加,有助于示波器一次顯示極大數量的數據。單位間隔定義為 UI = 1/比特速率。如圖 1 中眼狀圖所示。一個眼狀圖由 1 個 UI 組成(工程師有時會繪制兩個并排眼狀圖),它是數字信號質量的視覺體現。

圖 1

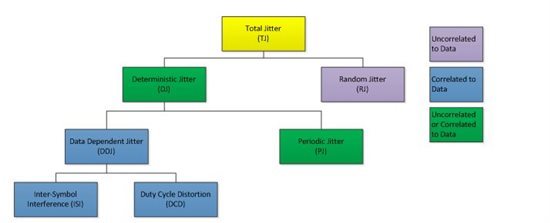

既然我們了解了眼狀圖,就可提出這樣一個問題“什么是抖動?”抖動可定義為不希望看到的、信號理想轉換位置的高頻率偏移。抖動可分為總體抖動 (TJ)、隨機抖動 (RJ) 和確定性抖動 (DJ)。顧名思義,總體抖動 (TJ) 包含所有抖動組成部分的影響。下圖 2 中的流程圖是 TJ 及其所有組件的分解圖:

圖 2

如欲了解有關 TJ 的更多詳情,敬請查看應用手冊《如何測量總體抖動》。

RJ 是不可預測的,而且通過隨機過程不斷積累,其中包括但不僅限于熱噪聲、散粒噪聲與電源噪聲。RJ 不受限制,因此其測量值會隨時間推移持續增大。

DJ 是可預測的抖動,因為它與所傳輸的數據類型以及傳輸媒介有關。DJ 具有非高斯概率密度分布函數,而且是有界限的,因此其測量值會隨時間推移增加到某一點,但不會無限增大。DJ 包含幾個組成部分,其中包括數據相關抖動 (DDJ)、占空比失真 (DCD)、碼間串擾 (ISI) 與周期性抖動 (PJ)。

碼間串擾 (ISI) 是所選傳輸媒介內帶寬不足的產物。PCB 跡線或線纜可作為低通濾波器 (LPF) 衰減數據信號中的高頻率內容。這會引起電壓失調和不均衡數據模式,如果處理不當最終會導致位錯誤。占空比失真 (DCD) 是升降時間不等的結果,其可導致具有不同持續時間的 1 和 0,引起閥值交點偏移。數據相關抖動 (DDJ) 是與數據模式有關的抖動,由帶寬限制 (ISI) 和閥值交點偏移 (DCD) 的總和效應引起。對于 DDJ 而言,之前傳輸的數據位會給當前數據位狀態產生負面影響。周期性抖動 (PJ) 是按周期形式重復的抖動,不包含數據相關性抖動組成部分。PJ 可以是任何具有周期性特性的邊緣偏移。有一種 PJ 叫做正弦曲線抖動 (SJ),因為它可分解成諧波相關正弦曲線的傅里葉級數。PJ 一般由外部確定性噪聲源引起,該噪聲源通過開關電源、串擾或不穩定時鐘恢復 PLL 耦合在我們的系統中。當然,可通過每個抖動成分了解更多信息,我建議大家對其進行深入挖掘,真正理解抖動及其組分。

ISI 抖動是傳輸媒介帶寬的函數,因此可通過設計進行補償。如果背板或線纜傳輸路徑出現大量 ISI 抖動,可使用 SN65LVCP1414 線性均衡器和 SN65LVCP114 線性四通道多路復用器均衡器等器件來對通道的 LPF 效應進行逆向處理。這些器件可為您的系統補償高達 17dB 的損耗,從而可通過減少整體抖動來擴展通道范圍。

-

眼圖測量

+關注

關注

0文章

4瀏覽量

8848 -

信號抖動

+關注

關注

1文章

4瀏覽量

9177

發布評論請先 登錄

相關推薦

示波器眼圖的關鍵參數

TTL電平與高電平信號的轉換

txs0102使用中遇到的高電平是什么引起的?怎么解決?

高電平輸入和低電平輸入是什么意思

rca輸出是低電平還是高電平

雙色led燈的引腳為高電平還是低電平

如何解決交流接觸器出現異常抖動問題

芯片引腳懸空是高電平還是低電平

高電平和低電平輸入有什么區別

高速信號傳輸中的抖動和眼圖挑戰

從眼狀圖入手,了解高電平抖動問題

從眼狀圖入手,了解高電平抖動問題

評論