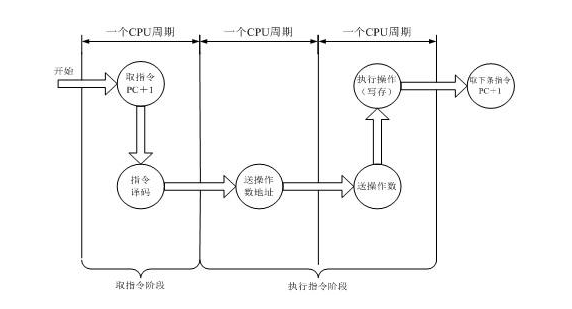

指令周期是取出一條指令并執(zhí)行這條指令的時間。一般由若干個機器周期組成,是從取指令、分析指令到執(zhí)行完所需的全部時間。

指令周期類型有非訪內(nèi)指令的指令周期、取數(shù)指令的指令周期、存數(shù)指令的指令周期、空操作指令和轉(zhuǎn)移指令的指令周期。

指令不同,所需的機器周期數(shù)也不同。對于一些簡單的的單字節(jié)指令,在取指令周期中,指令取出到指令寄存器后,立即譯碼執(zhí)行,不再需要其它的機器周期。對于一些比較復(fù)雜的指令,例如轉(zhuǎn)移指令、乘法指令,則需要兩個或者兩個以上的機器周期。

從指令的執(zhí)行速度看,單字節(jié)和雙字節(jié)指令一般為單機器周期和雙機器周期,三字節(jié)指令都是雙機器周期,只有乘、除指令占用4個機器周期。

因此在進行編程時,在完成相同工作的情況下,選用占用機器周期少的命令會提高程序的執(zhí)行速率,尤其是在編寫大型程序程序的時候,其效果更加明顯。

指令周期的四個階段

非訪內(nèi)指令的指令周期

CLA是一條非訪內(nèi)指令,它需要兩個CPU 周期,其中取指令階段需要一個CPU周期,執(zhí)行指令階段需要一個CPU周期。

1、取指令階段

(1)程序計數(shù)器PC的內(nèi)容20(八進制)被裝入地址寄存器AR;

(2)程序計數(shù)器內(nèi)容加1,變成21,為取下一條指令做好準備;

(3)地址寄存器的內(nèi)容被放到地址總線上;

(4)所選存儲器單元20的內(nèi)容經(jīng)過數(shù)據(jù)總線,傳送到數(shù)據(jù)緩沖寄存器DR;

(5)緩沖寄存器的內(nèi)容傳送到指令寄存器IR;

(6)指令寄存器中的操作碼被譯碼或測試;

(7)CPU識別出是指令CLA,至此,取指令階段即告結(jié)束。

2、執(zhí)行指令階段

(1)操作控制器送一控制信號給算術(shù)邏輯運算單元ALU;

(2)ALU響應(yīng)該控制信號,將累加寄存器AC的內(nèi)容全部清零,從而執(zhí)行了CLA指令。

取數(shù)指令的指令周期

1.送操作數(shù)地址

第二個CPU周期主要完成送操作數(shù)地址。在此階段,CPU的動作只有一個,那就是把指令寄存器中的地址碼部分(30)裝入地址寄存器,其中30為內(nèi)存中存放操作數(shù)的地址。

2.兩操作數(shù)相加

第三個CPU周期主要完成取操作數(shù)并執(zhí)行加法操作中。在此階段,CPU完成如下動作:

(1)把地址寄存器中的操作數(shù)的地址發(fā)送到地址總線上。

(2)由存儲器單元30中讀出操作數(shù),并經(jīng)過數(shù)據(jù)總線傳送到緩沖寄存器。

(3)執(zhí)行加操作:由數(shù)據(jù)緩沖寄存器來的操作數(shù)可送往ALU 的一個輸入端,已等候在累加器內(nèi)的另一個操作數(shù)(因為CLA指令執(zhí)行結(jié)束后累加器內(nèi)容為零)送往ALU的另一輸入端,于是ALU將兩數(shù)相加,產(chǎn)生運算結(jié)果為0+6=6。這個結(jié)果放回累加器,替換了累加器中原先的數(shù)0 。

存數(shù)指令的指令周期

STA指令的指令周期由三個CPU周期組成。

1.送操作數(shù)地址

在執(zhí)行階段的第一個CPU周期中,CPU完成的動作是把指令寄存器中地址碼部分的形式地址40裝到地址寄存器。其中數(shù)字40是操作數(shù)地址。

2.存儲和數(shù)

執(zhí)行階段的第二個CPU周期中,累加寄存器的內(nèi)容傳送到緩沖寄存器,然后再存入到所選定的存儲單元(40)中。CPU完成如下動作:

(1)累加器的內(nèi)容被傳送到數(shù)據(jù)緩沖寄存器DR;

(2)把地址寄存器的內(nèi)容發(fā)送到地址總線上,即為將要存入的數(shù)據(jù)6的內(nèi)存單元號;

(3)把緩沖寄存器的內(nèi)容發(fā)送到數(shù)據(jù)總線上;

(4)數(shù)據(jù)總線上的數(shù)寫入到所選中的存儲器單元中,即將數(shù)6寫入到存儲器40號單元中。注意 在這個操作之后,累加器中仍然保留和數(shù)6,而存儲器40號單元中原先的內(nèi)容被沖掉 。

空操作指令和轉(zhuǎn)移指令的指令周期

第四條指令即“NOP”指令,這是一條空操作指令。其中第一個CPU周期中取指令,CPU把23號單元的“NOP”指令取出放到指令寄存器,第二個CPU周期中執(zhí)行該指令。因譯碼器譯出是“NOP”指令,第二個CPU周期中操作控制器不發(fā)出任何控制信號。NOP指令可用來調(diào)機之用。

1.第一個CPU周期(取指令階段)

CPU把24號單元的“JMP 21”指令取出放至指令寄存器,同時程序計數(shù)器內(nèi)容加1,變?yōu)?5,從而取下一條指令做好準備。

2.第二個CPU周期(執(zhí)行階段)

CPU把指令寄存器中地址碼部分21送到程序計數(shù)器,從而用新內(nèi)容21代替PC原先的內(nèi)容25。這樣,下一條指令將不從25單元讀出,而是從內(nèi)存21單元開始讀出并執(zhí)行,從而改變了程序原先的執(zhí)行順序。

注意 執(zhí)行“JMP 21”指令時,我們此處所給的四條指令組成的程序進入了死循環(huán),除非人為停機,否則這個程序?qū)o休止地運行下去,因而內(nèi)存單元40中的和數(shù)將一直不斷地發(fā)生變化。當(dāng)然,我們此處所舉的轉(zhuǎn)移地址21是隨意的,僅僅用來說明轉(zhuǎn)移指令能夠改變程序的執(zhí)行順序而已

-

cpu

+關(guān)注

關(guān)注

68文章

10905瀏覽量

213030

發(fā)布評論請先 登錄

相關(guān)推薦

指令周期的四個階段詳解

指令周期的四個階段詳解

評論