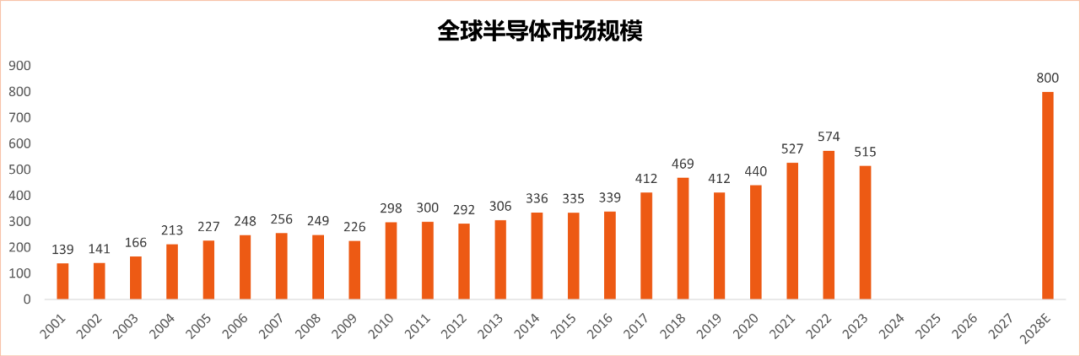

從2001年到現(xiàn)在,全球半導體市場規(guī)模的增長先后主要依靠PC、Smart Phone和HPC三大驅(qū)動力。在HPC的驅(qū)動下,全球半導體市場規(guī)模將從2023年的5150億美元增長到2028年的8000億美元,CAGR高達9.2%。基于SerDes的Chip-to-Chip技術(shù)能夠?qū)崿F(xiàn)HPC集群的萬卡、十萬卡等超大規(guī)模組網(wǎng),提升整體數(shù)據(jù)中心的算力協(xié)同效率。

數(shù)據(jù)來源:World Semiconductor Trade Statistics

UCIe+SerDes對大算力芯片的價值

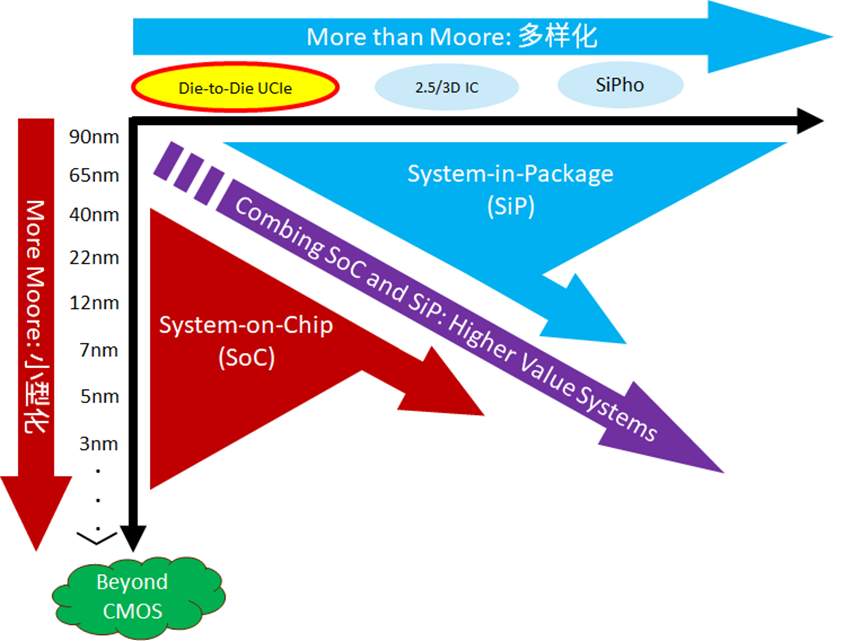

目前,基于UCIe的Multi-Die Chiplet是實現(xiàn)More than Moore的重要手段,結(jié)合先進的2.5D和3D封裝技術(shù)已經(jīng)實現(xiàn)產(chǎn)業(yè)化的高效量產(chǎn)與推廣,成為國內(nèi)外HPC芯片的主流設(shè)計選擇。

圖源:晟聯(lián)科

UCIe作為統(tǒng)一的接口標準,可以讓不同F(xiàn)oundry,不同工藝之間的Chiplet互聯(lián),讓Chiplet的封裝成本和效率得到進一步優(yōu)化,最終將Chiplet推向Market Place的終極形態(tài)。

晟聯(lián)科16G/32G UCIe IP解決方案作為一種低延時、低功耗和高性能的Chiplet芯片互聯(lián)方案,正在為Chiplet的廣泛應用場景賦能。目前在高性能計算(HPC)、數(shù)據(jù)中心、CPU、加速器等應用場景助力Chiplet實現(xiàn)低功耗和低延遲。

晟聯(lián)科UCIe+SerDes高速IP對大算力芯片的價值

1、High Bandwidth 高帶寬

當前大部分國內(nèi)HPC芯片Die-to-Die Bandwidth在幾百GB/s~1TB/s之間,國際巨頭HPC芯片Die-to-Die Bandwidth在10TB/s級別。UCIe+SerDes技術(shù),提升了數(shù)據(jù)傳輸效率,使得海量數(shù)據(jù)能夠在芯片內(nèi)部及芯片間快速流通,滿足人工智能、高性能計算等領(lǐng)域?qū)Ω咚贁?shù)據(jù)傳輸能力的迫切需求。

2、Low Latency 低延時

UCIe SPEC要求在2D和2.5D封裝下實現(xiàn)≤ 2ns的Latency,高速SerDes的RX+TX Latency通常為10ns上下,UCIe+SerDes技術(shù),將會有效優(yōu)化信號傳輸路徑、減少信號失真及采用高效的時鐘同步機制,為實時數(shù)據(jù)處理、大參數(shù)模型訓練等場景提供了堅實的技術(shù)支撐。

3、Improve Time-to-Market 加快市場速度

HPC芯片作為大算力芯片,Die面積越做越大,采用Multi-Die有利于提升良率,不同Die也可以靈活配置成不同的產(chǎn)品系列,從而進一步降低成本,滿足未來多元化、復雜化的計算需求,加快Time-to-Market的節(jié)奏。

UCIe+SerDes,實現(xiàn)Interface IP高速互連

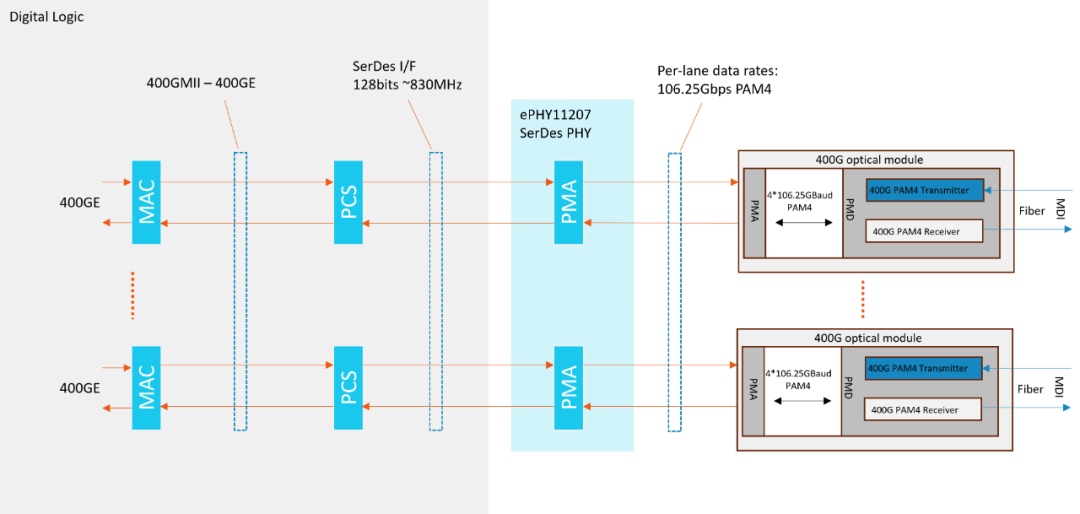

為了應對HPC等大算力應用帶來的挑戰(zhàn),晟聯(lián)科112G SerDes跟光模塊配合實現(xiàn)Chip-to-Chip高速互連,讓分布式運行的多Die集成為一顆高性能運行的芯片,做到低延時,高速度。同時支持同構(gòu)和異構(gòu)集成HPC芯片架構(gòu),并提供優(yōu)秀的產(chǎn)品性能表現(xiàn)。

▲ 晟聯(lián)科112G SerDes IP跟光模塊配合實現(xiàn)Chip-to-Chip高速互連

UCIe SPEC要求在2D和2.5D封裝下Latency≤2ns,在3D封裝下≤125ps。Speed要求要求32GT/s。

晟聯(lián)科UCIe+SerDes高速IP互連解決方案能經(jīng)過多年的研發(fā)和積累,是國內(nèi)少數(shù)在先進工藝,同時支持32G UCIe和112G SerDes的高速接口IP解決方案的公司,能夠?qū)崿F(xiàn)High Speed + Low Latency + Long Reach,晟聯(lián)科支持HPC高性能計算客戶取得更大的創(chuàng)新:

? UCIe速率達到32GT/s,達到業(yè)界領(lǐng)先水平

? 低延時,快至接近2ns

? 提供高效穩(wěn)定的數(shù)據(jù)傳輸需求

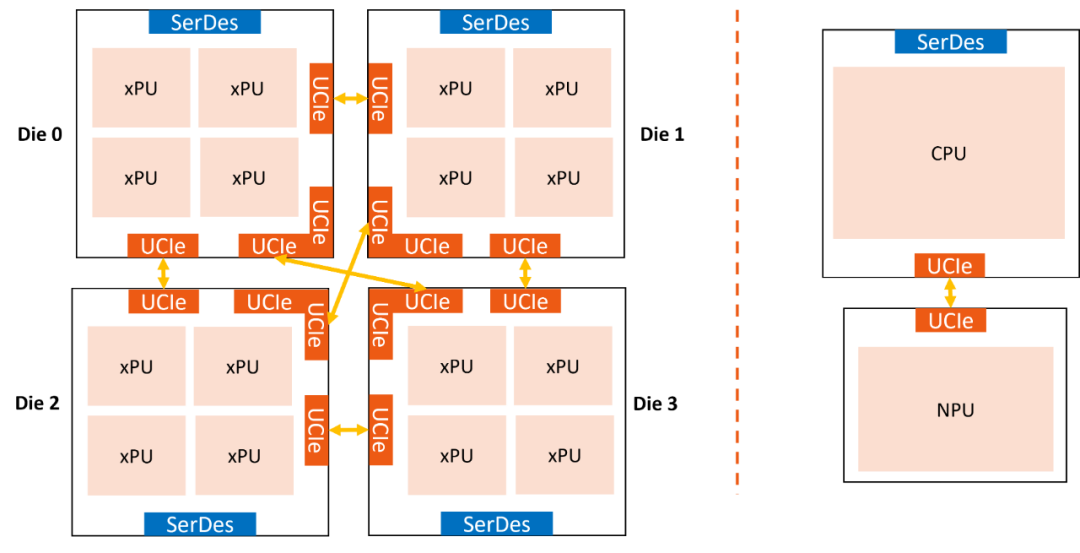

UCIe+SerDes IP的使用方式主要有2種,一種是UCIe+SerDes IP跟xPU集成在同一個Die里,Die和Die之間采用同構(gòu)或者異構(gòu)的集成方式。

▲ SerDes和UCIe在同構(gòu)/異構(gòu)集成系統(tǒng)中的應用方式

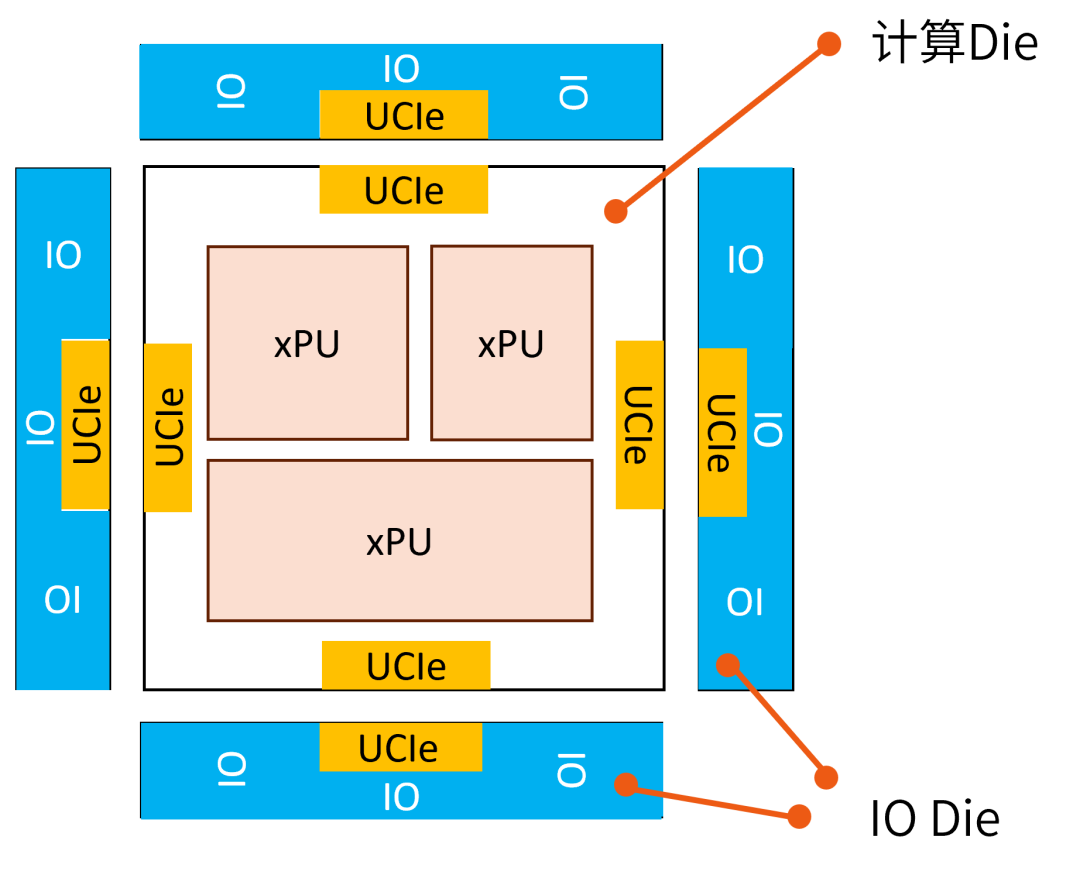

另外一種是UCIe+SerDes+PCIe等IP組成一個獨立的IOD,并跟計算Die做互連,從而形成IOD和計算Die在功能上的分離。根據(jù)客戶需求不同芯片可以采用不同的使用方式。

▲ IOD的應用方式

晟聯(lián)科,科技智連,異構(gòu)集成

晟聯(lián)科作為國內(nèi)領(lǐng)先的高速接口IP供應商,致力于為加速算力提供高速接口解決方案。擁有涵蓋遠距離、低功耗、低延時的高速SerDes及UCIe IP、PCIe6.0高速接口IP解決方案,滿足高性能計算。2014年起,公司自主研發(fā)并掌握DSP-based高速SerDes核心技術(shù),PAM4 SerDes已經(jīng)量產(chǎn)出貨,并在2021年全球率先商用Die-to-Die技術(shù)!目前,公司的高速SerDes IP已有超過2億條通道在世界500強客戶芯片和設(shè)備中出貨。

晟聯(lián)科全球總部和研發(fā)中心位于上海,在深圳、武漢等地擁有辦事處,為全國各地客戶提供專業(yè)、周到、及時的售前、售中與售后的本地化技術(shù)支持服務。在專利方面,晟聯(lián)科擁有20多項發(fā)明專利,為客戶技術(shù)和應用場景賦能。

審核編輯 黃宇

-

HPC

+關(guān)注

關(guān)注

0文章

324瀏覽量

23853 -

SerDes

+關(guān)注

關(guān)注

6文章

201瀏覽量

35042 -

UCIe

+關(guān)注

關(guān)注

0文章

48瀏覽量

1651

發(fā)布評論請先 登錄

相關(guān)推薦

康佳特發(fā)布高性能COM-HPC模塊

CES 2025上黑芝麻智能與大陸集團簽署合作備忘錄,共同發(fā)力高性能計算單元 (HPC)

聯(lián)電獲得高通高性能計算先進封裝大單

云端HPC市場崛起:阿里云以CIPU架構(gòu)引領(lǐng)高性能計算新時代

維諦技術(shù)(Vertiv):未來HPC,你想象不到的酷炫變革!

云計算hpc的主要功能是什么

HPC云計算前景

云計算hpc是什么意思

帶你了解什么是高性能計算(HPC)

晟聯(lián)科UCIe+SerDes方案塑造高性能計算(HPC)新未來

晟聯(lián)科UCIe+SerDes方案塑造高性能計算(HPC)新未來

評論