從賦能聊天機器人快速生成回答的生成式人工智能工具,到支持金融預測和天氣建模的高性能計算(HPC)應用,我們對處理能力的需求顯然達到了新的高度。面對這些計算密集型工作負載,單片SoC已不再能夠滿足當今的處理需求。為此,我們不斷創新工程技術,Multi-Die系統也應運而生。這種在單一封裝中實現異構集成的技術突破,不僅帶來了更優越的系統功耗和性能,還提高了產品良率,加速了更多系統功能的整合。

Multi-Die系統承擔著如此重要的角色,那開發者又該如何確保它們在整個生命周期內穩健可靠呢?

芯片測試對于任何芯片設計而言都至關重要。Multi-Die系統更是如此,需要對裸片到系統級執行全面測試,其中包括將各組件連接在一起的所有互連技術,例如通用芯粒互連技術(UCIe)。在這篇文章中,我們將深入探討Multi-Die系統的獨特問題,以及如何通過測試和芯片生命周期管理來確保這些復雜的設計能夠按預期可靠地工作。開發者如需獲得更多見解,還可以觀看我們的網絡研討會系列:“成功實現Multi-Die系統所需具備的條件”(共六個部分)。該系列網絡研討會介紹了Multi-Die系統的趨勢和挑戰、早期架構設計、協同設計和系統分析、Die-to-Die連接、驗證及系統健康狀況等等。

從裸片到系統的全面芯片測試

許多因素都會影響芯片的性能,溫度、老化和退化只是其中的一部分。對于Multi-Die系統來說,老化風險甚至更高,因為一個裸片發生故障可能會導致整個系統失效,造成巨大的經濟損失。在裸片層面排除缺陷是一個很好的開始。每個生產的裸片都將經歷專門的測試流程,以確保百萬分比缺陷率(DPPM)非常低。測試自動化流程負責測試和診斷器件的數字、內存和模擬部分。這其中的挑戰在于找到所需測試向量數量和相關成本之間的平衡點,以期獲得理想結果。

檢查每個裸片很重要,在系統層面評估整個系統也很重要。Multi-Die系統可以將不同工藝節點、不同用途的裸片或芯粒組合在一起。因此,一個系統可能包含運行溫度或散熱水平不同的多個裸片。此外,裸片之間的電磁干擾以及電遷移也可能造成問題。

對于Multi-Die系統,全面而徹底的預組裝測試環節,可以篩選出已知良好裸片(KGD)。設計模塊內置的高級可測性設計(DFT)功能可以評估裸片。對各個裸片進行測試,并在必要時進行修復后,設計就進入了組裝和鍵合階段。部分或全部鍵合內存和邏輯芯片之后,就可以測試互連了。

降低芯粒互連的功耗并提升其性能

Die-to-Die接口使裸片可以并排放置,為了進一步提高密度,還可以堆疊在2.5D或3D封裝中。如果兩個裸片之間提供數據接口的功能塊(即接口),可以兼具高帶寬、低功耗和低延遲特性,系統性能就能得到提升。

Die-to-Die連接通常基于高速接口,例如UCIe,該接口有望成為Multi-Die系統的優選互連標準,也是行業唯一具有完整的Die-to-Die接口工具套件的標準。UCIe適用于2D、2.5D未來的3D封裝,支持目前每引腳8 Gbps到16 Gbps的大部分設計,非常適合從網絡連接到超大規模數據中心的高帶寬應用。對于3D設計,由于互連更短,使得硅通孔(TSV)更加脆弱,因此互連級風險更高。

Multi-Die系統開發者需要避免互連中的固定型故障、開路或短路,同時確保時序和電壓方面的行為正確。由于涉及超高速信號,信號完整性成為了指示裸片間數據共享有效性的重要參數,所以通過測量和監控來檢測信號衰減水平非常重要。UCIe要求在PHY的兩側之間提供冗余通道,從而支持通過這些額外的通道實現故障修復。基于UCIe系統中的所有裸片都必須通過UCIe通道進行訪問、測試和修復,以便能夠監控裸片中正在發生的問題。

鍵合后測試可以解決一些要求切換互連通道的互連層面問題,還可以通過算法測試來評估互連缺陷。2.5D和3D互連有不同的算法集,而且測試是基于互連的缺陷。故障模型將決定所要應用的算法測試。

貫穿系統生命周期的智能監控和分析

Multi-Die系統具有微小的微凸塊,這些微凸塊彼此非常靠近,因此無法通過物理探測進行測試。例如,對于UCIe,微凸塊的間距為25至55微米,而探測距離通常為90微米。更好的辦法是通過內置自測(BIST)進行電子探測,從而檢測那些需要采取糾正措施的軟錯誤或硬錯誤。或者也可以使用在預組裝階段集成的專用晶圓測試焊盤。

當系統處于開發階段以及在現場使用時,芯片生命周期管理(SLM)方法就很有用。這種方法通過在芯片上集成傳感器和監控器來評估各種參數,例如溫度、電壓、老化和退化程度。集成SLM IP技術與分析智能后,可以將從器件傳感器和監控器收集的大量數據轉化為可操作的系統優化洞察。

那么SLM技術如何識別熱問題呢?無論是單個裸片還是Multi-Die系統,熱管理問題都不容忽視。在設計階段,由于沒有實際工作負載,開發者很難評估這些問題。再加上2.5D或3D架構的復雜性后,更是很難得到最終設計的熱曲線。以下是SLM能發揮作用的情況。布置在裸片重點位置的片上監控器讓開發者有機會深入了解和分析裸片的熱特性,并且可以在需要調整布局以解決散熱問題時提供指示信號。同樣,深入了解熱效應還可能促使開發者做出降低系統高帶寬內存(HBM)組件數據速率的決策。或者,可能還可以通過軟件來緩解散熱問題。借助監控器提供的數據,開發者可以分析并確定更優糾正方案。

SLM技術還提供可追溯性,即無論最終產品在生命周期中何時出現問題,它都能追溯到問題的根源。例如,假設在試制過程的某個環節發現良率異常,此時準確定位問題來源至關重要。我們需要判斷問題是出在某個特定晶圓或裸片上,還是影響了某一時期內生產的所有晶圓或裸片,抑或是源于晶圓廠本身。這種追溯能力在Multi-Die系統中尤為重要,因為此類系統的封裝成本可能非常高。越快發現問題,開發者就能越快讓產品進入市場并降低成本。良好的SLM解決方案應該能夠在幾分鐘內識別根本原因,而手動方法可能需要花費幾天或幾周時間。

可追溯性還適用于以下情況:最終產品已部署到現場,但開始出現意外甚至災難性的故障,可能需要召回。這種退貨授權(RMA)情況可以利用SLM和整個測試生態體系,追溯制造過程,找出根本原因。同時,還能找出現場中可能存在相同問題的同類器件,以便在故障發生前主動召回,或者通過調整器件的電壓或頻率來延長其使用壽命。

測試的最后階段針對堆疊本身進行。“已知良好系統”是此階段的核心,因為測試團隊的目標是確定其Multi-Die系統能否穩定可靠地運行,并在需要時找到監控、分析和解決問題的方法。IEEE Std 1838-2019提供了一種模塊化測試訪問架構,可支持測試裸片以及相鄰堆疊裸片之間的互連層。

對于堆疊架構,有些測試需要在下游進行,而更智能的測試仍然留在流程的上游。例如,在裸片層面評估高溫性能是不可行的。相反,在堆疊后進行Multi-Die系統的溫度測試最有效,此時發現的故障可以根據其位置進行修復。在晶圓層面進行溫度測試也是可行的,不過這可能相當昂貴。高端系統的開發者可能會選擇執行這些測試。監控和收集這些重要數據,能夠讓設計、制造和測試團隊確定如何提高結果質量。

自動化和智能化進一步提高Multi-Die系統的質量

為了滿足我們所討論的需求并推動下一波半導體創新,新思科技推出了Multi-Die解決方案,以加速單一封裝中的異構集成。這套全面的解決方案涵蓋了系統全生命周期的各個關鍵環節,包括測試、診斷、修復、校準以及持續優化各項性能指標。針對設計、試制、生產和現場優化的可追溯性和分析能力可以提高良率、質量和可靠性,并降低成本。此外,我們的AI驅動芯片設計套件Synopsys.ai具備業界少有的半導體測試自主AI應用程序。新思科技TSO.ai優化了復雜設計中的測試程序生成過程,能以更少的測試向量實現盡可能高的缺陷覆蓋率。

為了滿足計算密集型工作負載對高帶寬和高性能的需求,Multi-Die系統正迅速成為芯片設計的主流。自動化測試流程和分析智能有助于提高上述系統的質量和可靠性水平,而這更是為生成式人工智能和高性能計算(HPC)等造福全世界的應用帶來了曙光。

-

芯片測試

+關注

關注

6文章

135瀏覽量

20199 -

人工智能

+關注

關注

1796文章

47666瀏覽量

240272 -

新思科技

+關注

關注

5文章

807瀏覽量

50424 -

HPC

+關注

關注

0文章

324瀏覽量

23853

原文標題:從GenAI到HPC,Multi-Die系統如何滿足現代計算需求?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

利用Multi-Die設計的AI數據中心芯片對40G UCIe IP的需求

國產固態繼電器如何滿足物聯網應用的需求

AmpereOne如何滿足現代數據中心需求

詳解Arm計算平臺的優勢

嵌入式系統的未來趨勢有哪些?

新思科技業績超預期,自研AI芯片需求強勁

DDR4的單、雙DIE兼容,不做仿真行不行?

新思科技PCIe 7.0驗證IP(VIP)的特性

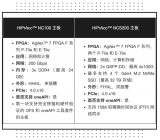

新思科技ZeBu EP和HAPS-100 A12 FPGA的關鍵用例

新思科技攜手英特爾推出可量產Multi-Die芯片設計解決方案

新思科技面向英特爾代工推出可量產的多裸晶芯片設計參考流程,加速芯片創新

新思科技針對主要代工廠提供豐富多樣的UCIe IP解決方案

新思科技推出業界首款PCIe 7.0 IP解決方案

TE推出的MULTI-BEAM Plus電源連接器具有哪些優勢?-赫聯電子

Hitek Systems開發基于PCIe的高性能加速器以滿足行業需求

新思科技Multi-Die系統如何滿足現代計算需求

新思科技Multi-Die系統如何滿足現代計算需求

評論