Hello,大家好,今天我們來分享下什么是先進(jìn)封裝中的TSV/硅通孔技術(shù)。

TSV:Through Silicon Via, 硅通孔技術(shù)。指的是在晶圓的硅部分形成一個(gè)垂直的通道,利用這個(gè)垂直的通道注入導(dǎo)電物質(zhì),將相同類別芯片或不同類別的芯片進(jìn)行互連,達(dá)到芯片級(jí)集成的先進(jìn)封裝技術(shù)。

TSV技術(shù)中的這個(gè)通道中主要是通過銅等導(dǎo)電物質(zhì)的填充完成硅通孔的垂直電氣互連,減小信號(hào)延遲,降低電容、電感,實(shí)現(xiàn)芯片的低功耗、高速通信,增加帶寬和實(shí)現(xiàn)器件集成的小型化需求。

在TSV技術(shù)之前,芯片之間的連接方式基本都是水平的,TSV的技術(shù)讓多個(gè)芯片可以進(jìn)行垂直連接,又叫堆疊。Wire bonding(引線鍵合)和Flip-Chip(倒裝焊)的Bumping(凸點(diǎn))提供了芯片對(duì)外部的電互連,通過TSV和RDL(再布線)則提供了芯片內(nèi)部的垂直和水平方向的電互連。

TSV根據(jù)應(yīng)用的構(gòu)造,大致可分為3種:

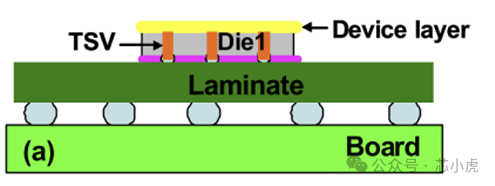

(a) 垂直的背面連接,無芯片堆疊。TSV位于有源晶粒(active die)中,用于連接至晶圓背面的焊盤(bond pad);

主要特點(diǎn):技術(shù)難度低,適合大規(guī)模投入生產(chǎn)應(yīng)用,例如應(yīng)用TSV的CMOS圖像傳感器(CIS)、SiGe功率放大器等。

應(yīng)用TSV的CMOS圖像傳感器的好處是

1)使用TSV代替引線鍵合可以減小圖像傳感器的尺寸。

2)簡化了圖像傳感器的晶圓級(jí)封裝(WLP)。WLP工藝的第一步是將玻璃晶圓附著到圖像傳感器的正面,防止光刻膠(抗蝕劑)微透鏡在組裝過程中受到損壞和污染,然而安裝好玻璃晶圓后會(huì)使從晶圓正面到焊盤的連接途徑受阻,TSV通過簡化晶圓級(jí)封裝,對(duì)此問題提供了簡易的解決方法。

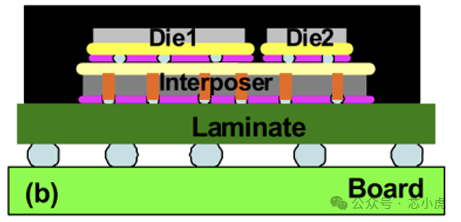

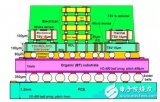

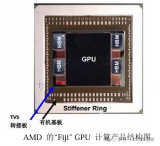

(b) 2.5D 封裝。晶粒(die)連接至硅中介層(interposer),TSV在中介層中;

主要特點(diǎn):技術(shù)難度中,與垂直的背面連接相比,2.5D 先進(jìn)封裝的硅中介層需要更小的 TSV 間距(≤50 μm),因此需要更先進(jìn)的TSV工藝。

現(xiàn)場可編程門陣列(Field Programmable Gate Array,FPGA)器件是最早使用硅中介層的產(chǎn)品之一:硅中間層可以使芯片間密切連接,整合后的結(jié)構(gòu)看起來像單個(gè)大尺寸的FPGA芯片,解決了早期直接構(gòu)建單個(gè)大尺寸FPGA芯片的技術(shù)難題。

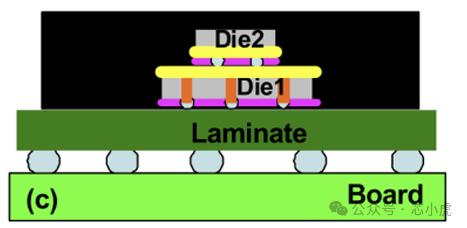

(c) 3D 封裝。TSV位于有源晶粒中,用于實(shí)現(xiàn)芯片堆疊。

主要特點(diǎn):技術(shù)難度高,存儲(chǔ)器堆疊是首批應(yīng)用3D堆疊TSV結(jié)構(gòu)的產(chǎn)品之一,和2.5D封裝中硅中階層對(duì)TSV間距的需求相似,但實(shí)際應(yīng)用中難度更高,例如對(duì)DRAM設(shè)備的寬I/O要求。使用寬 I/O的DRAM 和芯片堆疊的優(yōu)勢包括封裝高度降低40%,功耗降低50%,帶寬增加6倍。

-

TSV

+關(guān)注

關(guān)注

4文章

115瀏覽量

81565 -

硅通孔

+關(guān)注

關(guān)注

2文章

24瀏覽量

11871 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

427瀏覽量

286

原文標(biāo)題:先進(jìn)封裝中的--TSV/硅通孔技術(shù)

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

先進(jìn)封裝關(guān)鍵技術(shù)之TSV框架研究

簡單介紹硅通孔(TSV)封裝工藝

一文詳解硅通孔技術(shù)(TSV)

硅通孔(TSV)電鍍

3D IC集成與硅通孔TSV互連

3D封裝與硅通孔(TSV)工藝技術(shù)

中微推出用于3D芯片及封裝的硅通孔刻蝕設(shè)備Primo TSV200E(TM)

詳解TSV(硅通孔技術(shù))封裝技術(shù)

什么是TSV封裝?TSV封裝有哪些應(yīng)用領(lǐng)域?

技術(shù)資訊 I 3D-IC 中 硅通孔TSV 的設(shè)計(jì)與制造

硅通孔TSV-Through-Silicon Via

芯片先進(jìn)封裝硅通孔(TSV)技術(shù)說明

先進(jìn)封裝中的TSV/硅通孔技術(shù)介紹

先進(jìn)封裝中的TSV/硅通孔技術(shù)介紹

評(píng)論