絕緣體上硅(SOI)技術的基本思想是通過將承載電子器件的晶片表面的薄層與用作機械支撐的塊晶片電絕緣來解決器件和襯底之間的寄生效應。

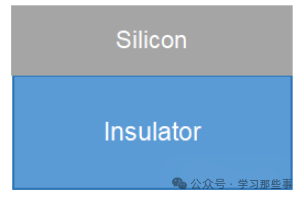

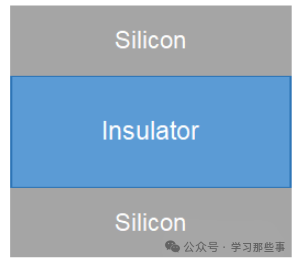

大多數微電子器件僅利用硅晶圓頂部前幾百納米用于電路傳輸。晶片厚度的其余幾百微米幾乎完全用作器件的機械支撐。器件和襯底之間的電相互作用可能會導致許多有害的寄生效應。絕緣體上硅(SOI)技術的基本思想是通過將承載電子器件的晶片表面的薄層與用作機械支撐的塊晶片電絕緣來解決這個問題。這可以通過將器件層放置在由絕緣材料制成的晶片上來實現(見圖1),或者通過使用絕緣夾層將器件層與硅塊分離(見圖 2)。大多數當前的SOI方法都集中在絕緣夾層結構上。

圖1硅器件層在絕緣體上

圖2埋層絕緣體層將表面 Si 層與Si襯底分隔開

為什么要使用SOI?

①避免器件和襯底之間相互作用而產生不必要的寄生效應,主要是降低源極和漏極與襯底之間產生的寄生電容。

②防止閂鎖,由于在CMOS工藝中形成寄生pnp和npn 雙極型晶體管,導致Vdd和Vss軌道之間產生低阻抗路徑。這些BJT形成具有正反饋的pnpn結構,將電源軌道短路至接地,從而導致過大電流流動,造成器件損壞。

③器件的完全電介質隔離降低了寄生電容,從而提高了性能。克服了亞微米器件固有的短溝道效應。

④隨著晶體管的縮小,柵極的長度也隨之減小。柵極對通道區域的控制也隨之減小,從而降低了晶體管的性能。SOI使用體偏置來提供對通道的更多控制。

⑤減少因亞閾值漏電和二極管漏電流而增加的漏電功率。

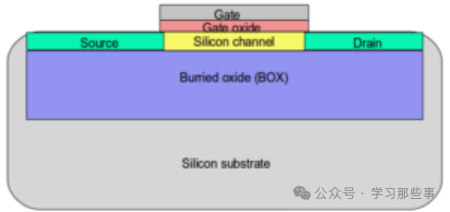

SOI 晶圓的結構

SOI晶圓結構具有三個基本特征:

頂部硅器件層:該超薄層能夠形成有源器件,一般5nm~2μm;

埋氧層(BOX):隔離器件層,一般5nm~2μm;

硅襯底:提供機械強度和支撐,一般200~700μm。

-

硅晶圓

+關注

關注

4文章

270瀏覽量

20728 -

晶片

+關注

關注

1文章

403瀏覽量

31575 -

SOI

+關注

關注

4文章

70瀏覽量

17698

原文標題:為什么要用SOI(Silicon-on-insulator)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

氣密性檢測干貨!150個核心關鍵詞,一文看懂

PCB板元器件點膠加固的重要性

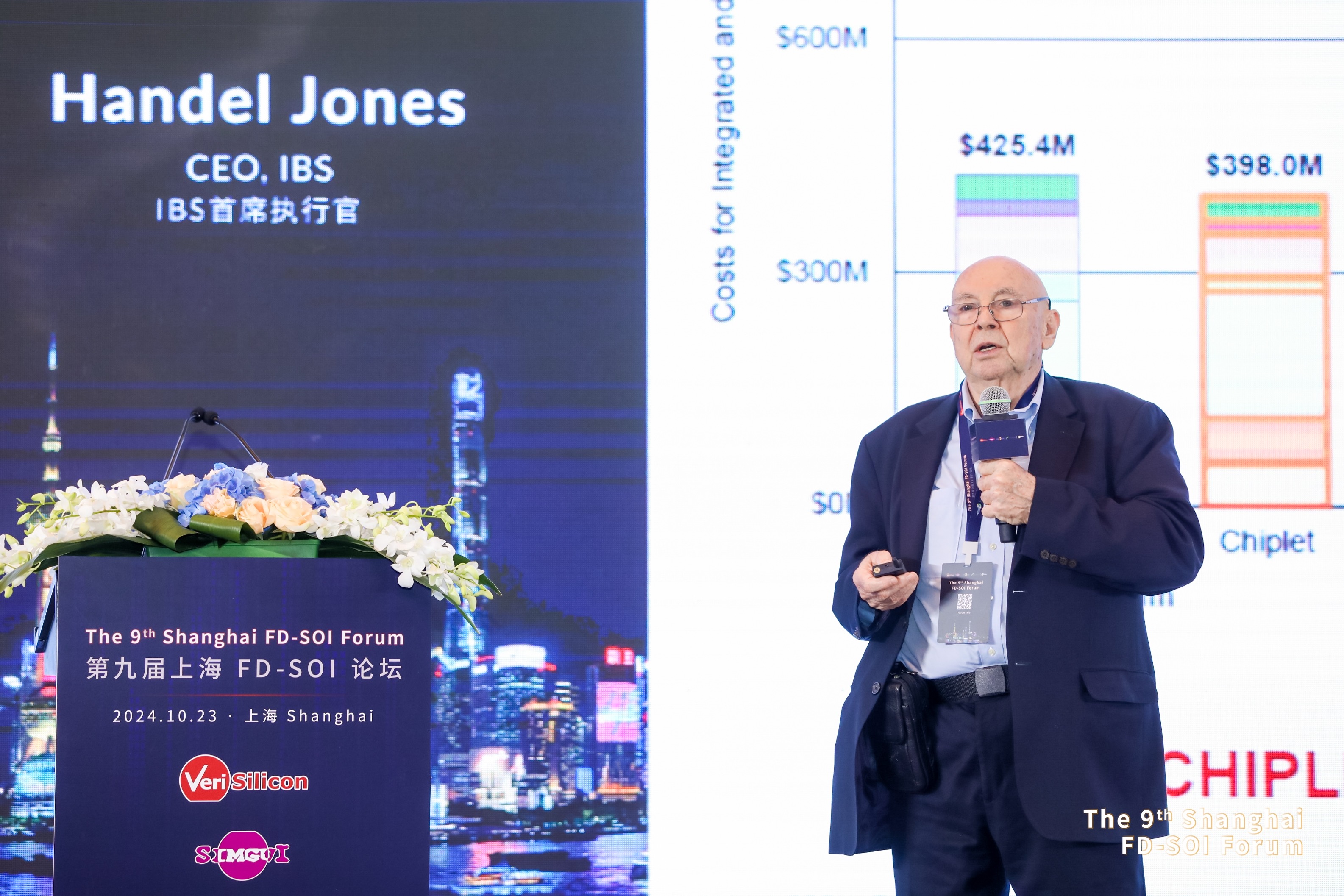

IBS首席執行官再談FD-SOI對AI的重要性,在≥12nm和≤28nm區間FD-SOI是更好的選擇

一文看懂SOI的重要性

一文看懂SOI的重要性

評論