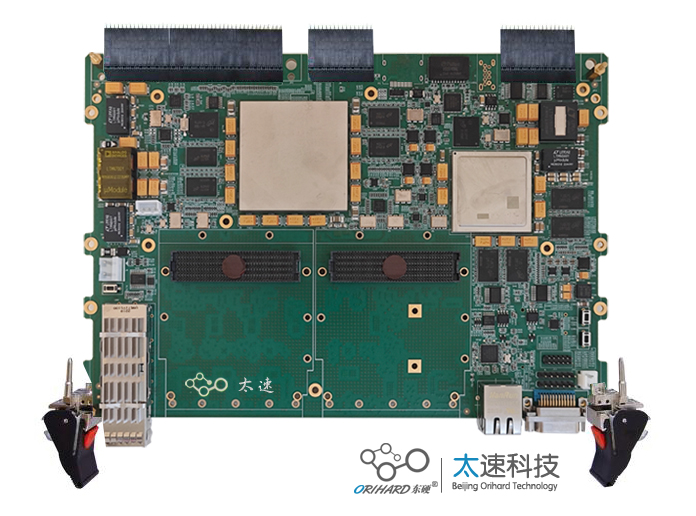

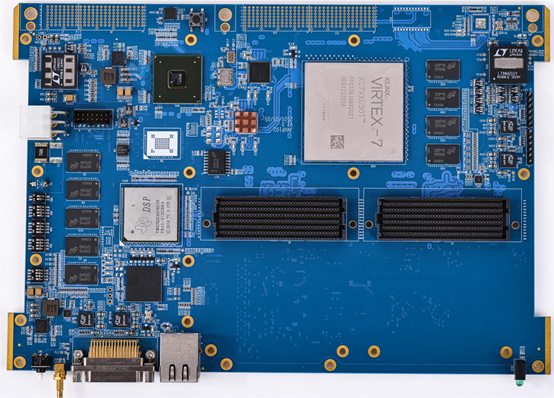

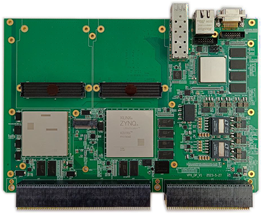

1、板卡概述

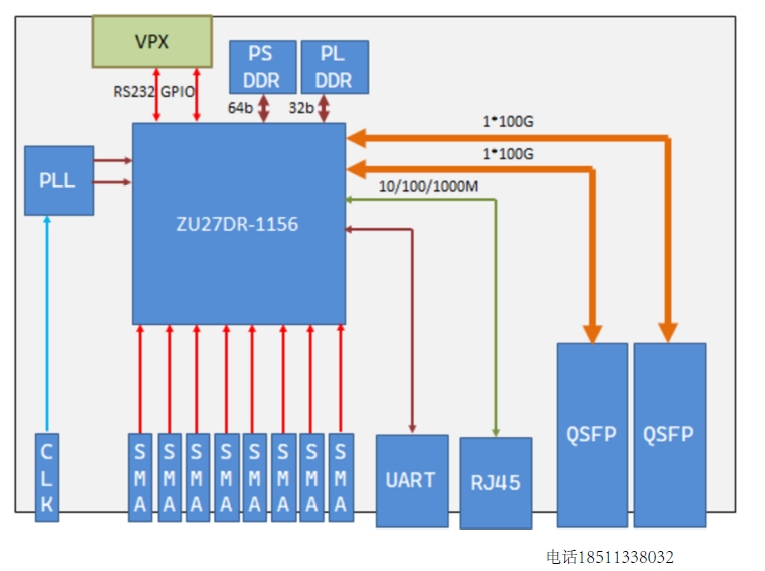

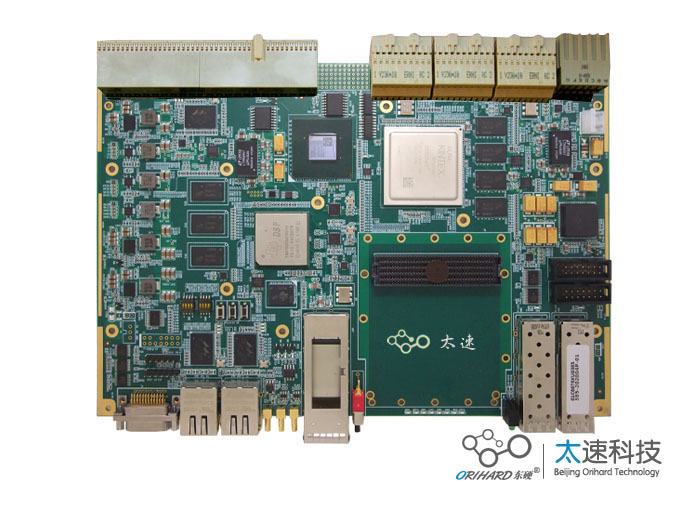

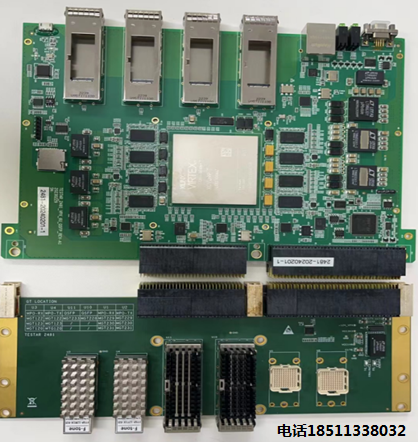

板卡由我公司自主研發,基于6UCPCI架構,處理板包含雙片TI DSP TMS320C6678芯片;一片Xilinx公司FPGA XC7K420T-1FFG1156 芯片;六個千兆網口(FPGA兩個,DSP四個);DSP與FPGA之間 RapidIOX4互聯, DSP 之間 Hyperlink X4 互聯;FPGA 提供12個GTX連于背板(GTX支持6.25Gbps的傳輸頻率);每顆DSP外接1GB的DDR3,64bit位寬,32MB Nor Flash;FPGA 外接2組DDR3,各512MB,64bit位寬,32MB Nor Flash;通過PCIe橋連接DSP的PCIe和FPGA的PCIe口,PCIe對外X4模式;FPGA連接不少于160根普通IO到CPCIe的P4,P5連接器。

2、處理板技術指標

板卡要求采用雙片TI DSP TMS320C6678芯片,8核,主頻1G。

板卡采用Xilinx公司FPGA XC7K420T-1FFG1156 芯片。

前面板 兩個DSP各出一個千兆網口,另外2個網絡連于背板。

前面板FPGA出兩個千兆網口,6個SFF模塊光纖,支持5Gbps

前面板出4個指示燈,1個復位按鈕。

DSP與FPGA之間 RapidIOX4互聯,DSP的Uart,SPI,I2C連接于FPGA。

DSP 之間 Hyperlink X4 互聯。

FPGA 提供12個GTX連于背板,支持4個X2,1個X4的工作模式配置。GTX高工作頻率為6.25Gbps。

每顆DSP外接1GB的DDR3,64bit位寬;32MB Nor Flash.

FPGA 外接2組DDR3,各512MB,64bit位寬,32MB Nor Flash,在原理圖設計階段,如FPGA的I/O引腳資源不夠,則可將DDR3位寬調整為32BIT寬。

DSP 支持遠程網絡加載,PCIe加載;FPGA支持Master SelectMAP和Master BPI加載,同時支持DSP0或者DSP1的SPI口對FPGA進行動態加載和對配置芯片程序更新。

FPGA連接不少于160根普通IO到CPCIe的P4,P5連接器。

FPGA能讀取背板槽位信息,ID[3:0]。

FPGA 外接E2PROM。

板卡芯片要求工業級。

供電 采用 +5V +12V 雙電源。

板卡結構標準CPCIe 6U大小。

整板冷卻,支持加固。

3、軟件系統

3.1 DSP底層軟件包括

(1)DSP的DDR3測試程序;

(2)DSP的Nor Flash 擦寫程序;

(3)DSP的網絡接口測試,SGMII互傳程序;

(4)DSP的HyperLink互連傳輸程序;

(5) DSP的SPI接口程序;

(6)DSP的I2C E2PROM操作程序;

(7)DSP的RapidIO接口驅動程序;

(8)DSP的Boot Load引導程序;

(9)DSP的多核加載測試程序;

(10)DSP的網絡加載程序;

(10)DSP的GPIO中斷服務測試程序;

(11) DSP對 FPGA的動態加載和配置程序更新程序;

3.2 FPGA底層軟件包括

(1)FPGA的DDR3驅動接口程序;

(2)FPGA的網絡接口驅動程序;

(3)FPGA的 Nor Flash接口驅動程序;

(4)FPGA與DSP的RapidIO驅動程序;

(5)與背板互連DSP板卡的GTX傳輸程序;

(6) FPGA的光纖接口驅動程序;

(7) 配置FPGA的控制程序;

(8) 從FPGA的電源管理,復位管理,配置管理程序;

4、物理特性:

尺寸:6U CPCIe板卡,大小為160X233.35mm。

工作溫度:0℃~ +55℃ ,支持工業級 -40℃~ +85℃

工作濕度:10%~80%

5、供電要求:

雙直流電源供電。整板功耗 50W。

電壓:+5V 5A ,+3.3V 6A。

紋波:≤10%

審核編輯 黃宇

-

板卡

+關注

關注

3文章

116瀏覽量

16879 -

CPCI

+關注

關注

6文章

71瀏覽量

32901 -

高速數據

+關注

關注

0文章

14瀏覽量

9554

發布評論請先 登錄

相關推薦

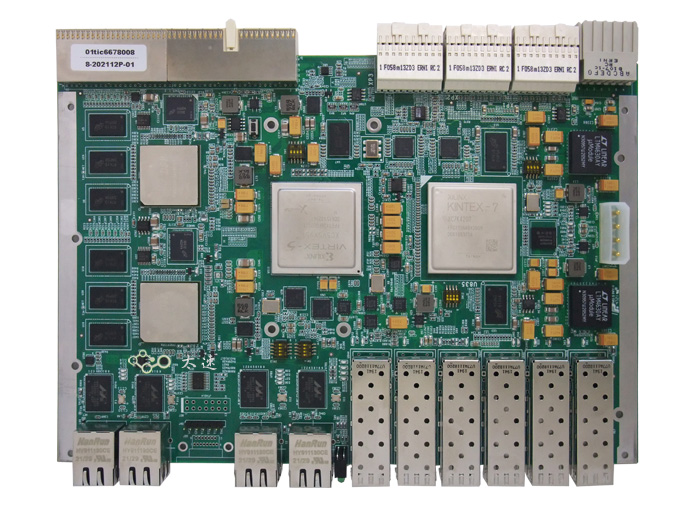

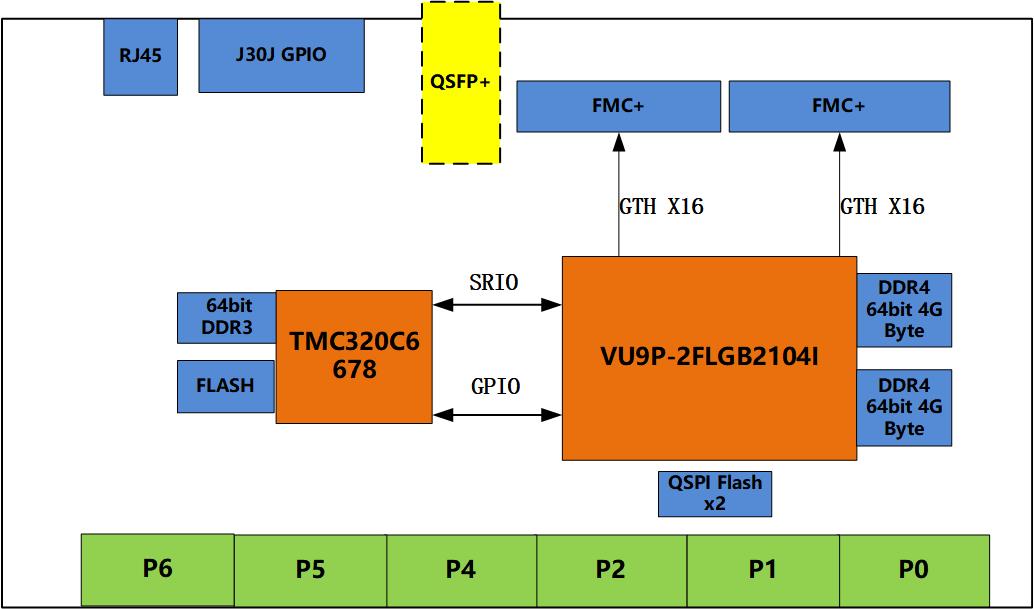

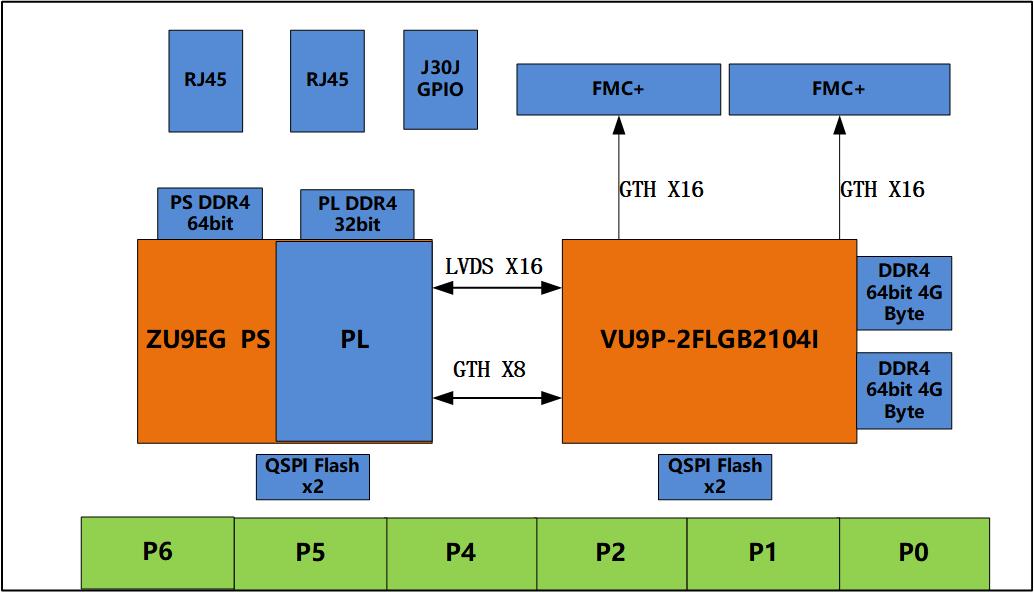

基于6U VPX的TMS320C6678+XCVU9P的高性能處理平臺

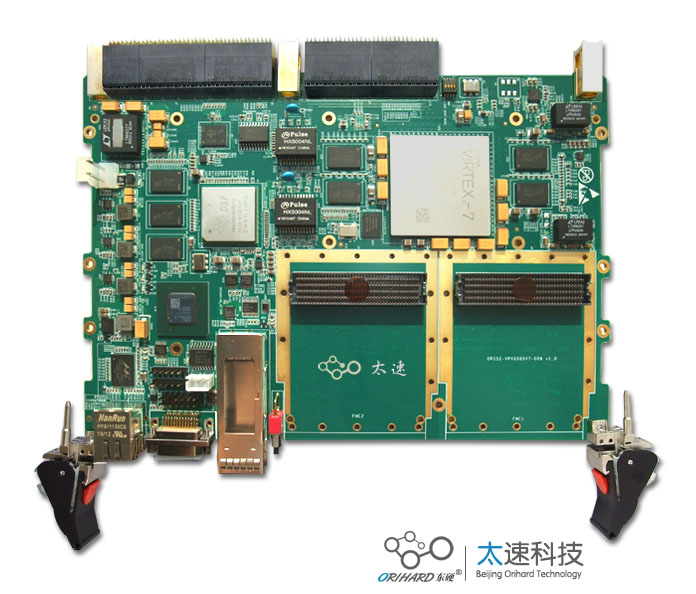

高速圖像處理卡設計原理圖:527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

高速圖像采集卡設計方案:204-基于Xilinx Virtex-6 XC6VLX240T 和TI DSP TMS320C6678的信號處理板

FMC子卡設計方案:202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC7K325T的高速數據處理核心板

基于6U VPX XCVU9P+XCZU7EV的雙FMC信號處理板卡

V7-690T和DSP6678雙FMC+ 6U VPX 高性能載板

KU115+ZU19EG+DSP6678的雙FMC 6U VPX處理板

VPX信號處理卡設計原理圖:18-基于雙TMS320C6678 DSP的3U VPX的信號處理平臺

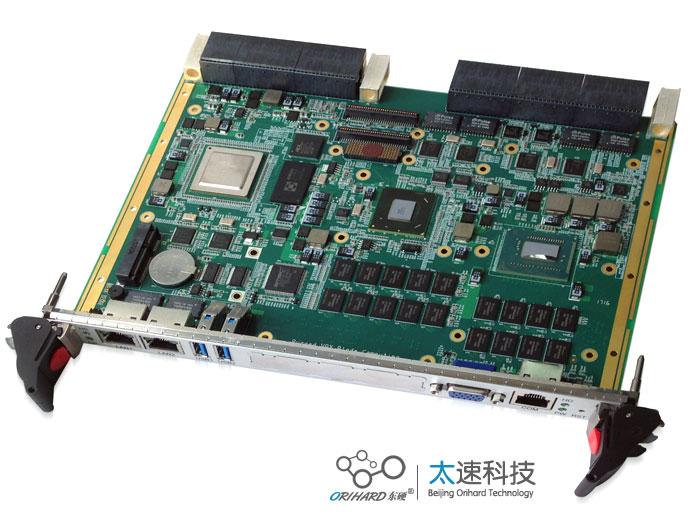

6U CPCI板卡設計方案:8-基于雙TMS320C6678 + XC7K420T的6U CPCI Express高速數據處理平臺

6U CPCI板卡設計方案:8-基于雙TMS320C6678 + XC7K420T的6U CPCI Express高速數據處理平臺

評論