本文介紹了隧穿晶體管的原理及它的優勢。

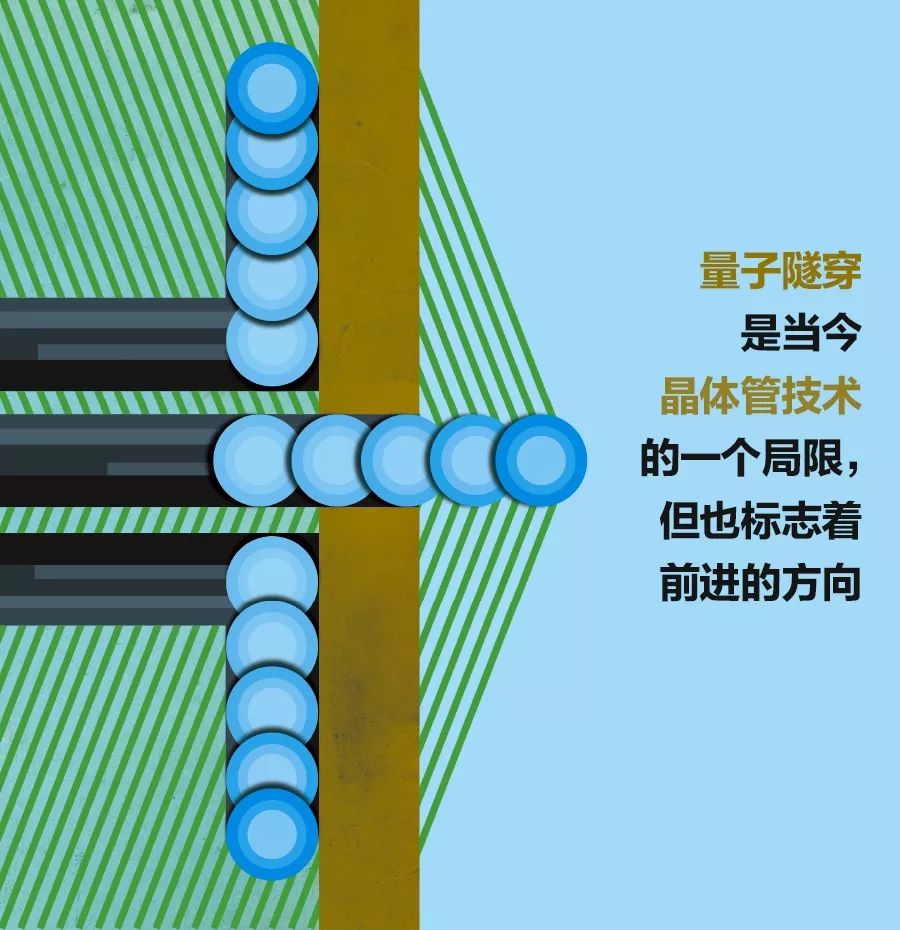

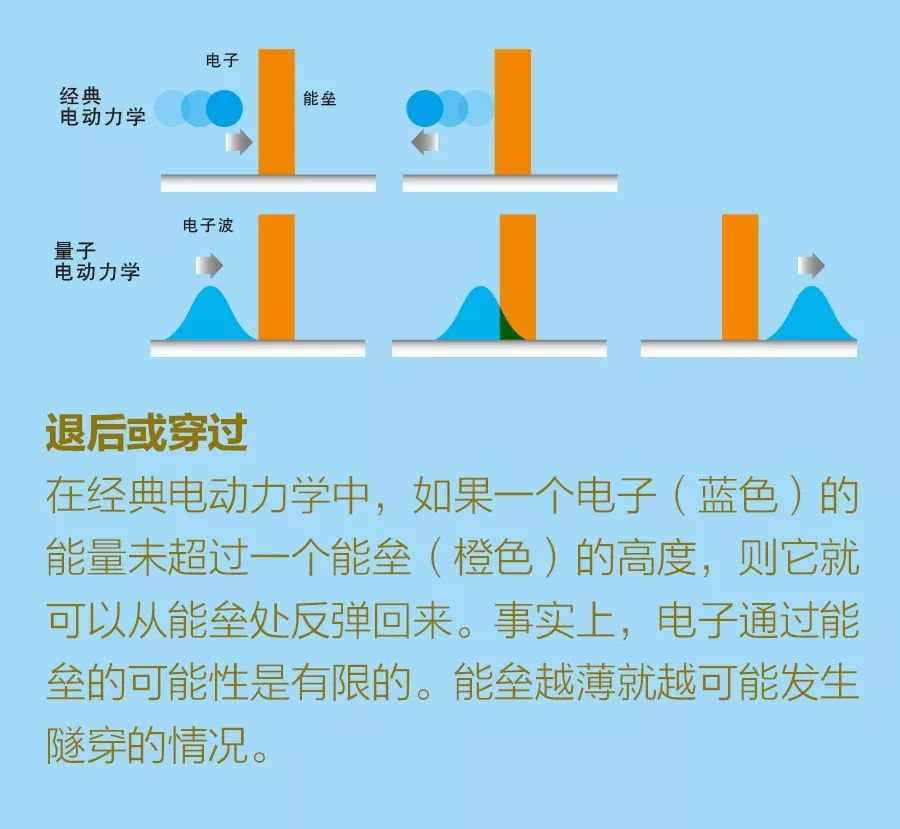

我們所處的這個由永遠在線的個人電腦、平板電腦和智能手機構成的世界的誕生,要歸功于一個了不起的趨勢:金屬氧化物半導體場效應晶體管(MOSFET)的不斷微型化。MOSFET是大多數集成電路的基礎構件,在過去的半個世紀內,其體積已經縮小到了原來的千分之一,從20世紀60年代的數十微米到如今僅數十納米。隨著一代代MOSFET變得越來越小,基于MOSFET的芯片與以前相比運行得更快,也更加省電。 這個趨勢帶來了工業史上持續時間最長、也是最偉大的一系列勝利,使我們獲得了前幾代人所無法想象的器件、容量和便利。但是這一穩定的進步受到了威脅,而問題的核心就在于量子力學。 電子有一個讓人傷腦筋的能力,即可以穿透能壘——這一現象被稱為量子隧穿。隨著芯片制造商在一個芯片上安裝越來越多的晶體管,晶體管變得越來越小,于是不同晶體管區域之間的距離就被壓縮了。因此,曾經厚度足以阻擋電流的電子屏障現在卻變得非常薄,使得電子能夠從中快速通過。

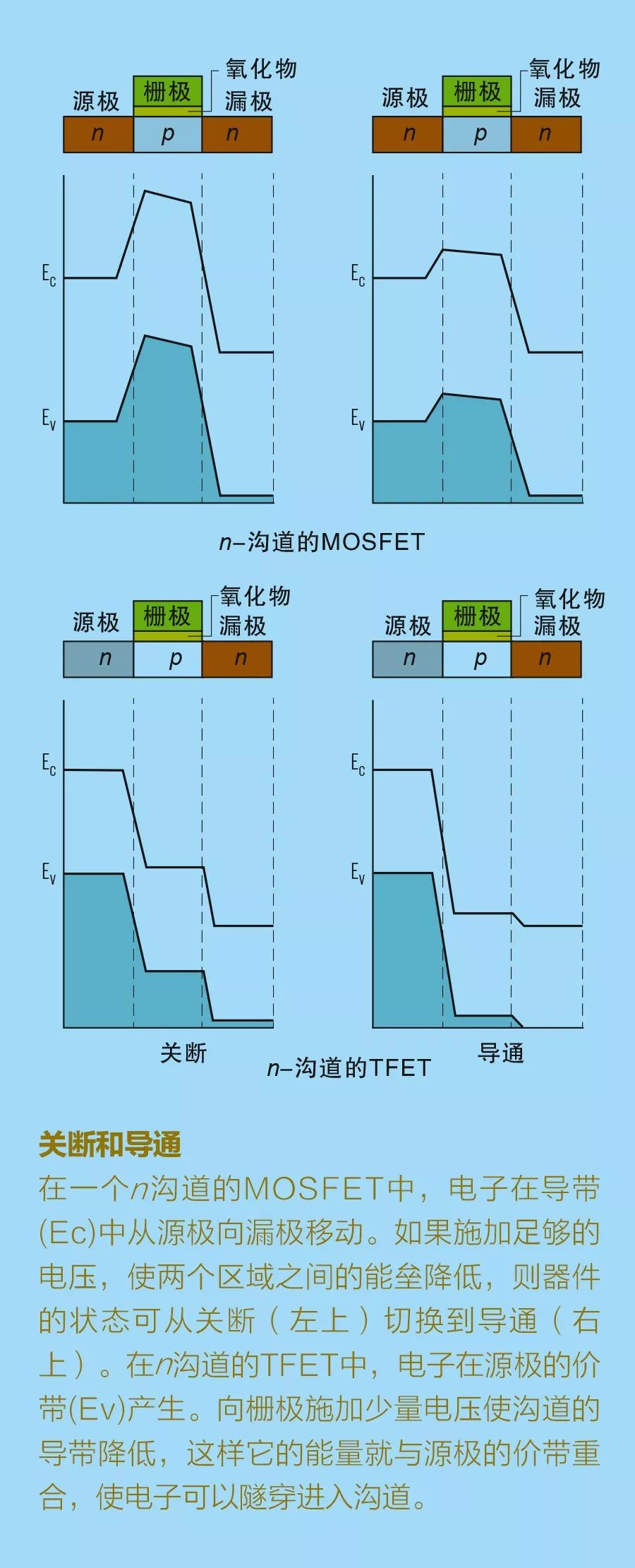

我們已經不再削薄構成晶體管的一個重要部分——柵氧化層。該層通過電子將控制晶體管導通和關斷的柵極與導電溝道隔開。通過將該氧化層削薄,就可以將更多的電荷導入溝道,加快電流流動,使晶體管運行速度更快。但是,氧化層厚度不能比1納米小太多,這也是我們今天大概所能達到的程度。如果超出這個限度,當晶體管處于“關斷”狀態時,會有過多的電荷在溝道內流動,而此時理想的狀態是沒有任何電荷在流動。這只是若干泄漏點之一。 我們無法阻止電子隧穿過這個薄薄的屏障,但是,我們可以使這一現象為我們所用。在最近的幾年中,一種較新的晶體管設計——隧穿場效應晶體管(TFET)——加速發展。與通過提高或降低能壘來控制電流流動的MOSFET的工作原理不同,TFET的能壘保持高位。該裝置通過改變能壘一側的電子在另一側出現的可能性來控制導通和關斷。 這個工作原理與傳統晶體管的工作方式有很大的差別。然而,這也許正是在MOSFET停止發展之時我們所需要大力發展的。它為開發更快、更密集和更加節能的電路來將摩爾定律拓展至下一個十年鋪平了道路。 這不是晶體管第一次改變形態。最初,基于半導體的計算機使用的是由雙極晶體管制造的電路。但就在硅制的MOSFET于1960年問世的幾年之后,工程師們意識到他們可以制造出兩個互補的開關,這樣它們可以共同組成互補金屬氧化物半導體(CMOS)電路。該電路與雙極晶體管邏輯不同,只在導通時消耗能量。自從第一個基于CMOS的集成電路在上世紀70年代早期出現后,MOSFET就開始占據市場的主導地位。 從許多方面來看,MOSFET都與雙極晶體管沒有太大不同。二者都通過提高或降低能壘來控制電流流動——有點像提高或降低河上的水閘。在這個情況下,“河水”即由兩種載流子構成:電子和空穴,后者是一個帶正電荷的實體,本質上是材料中一個原子的外層能殼上缺少一個電子。 對這些載流子來說,存在兩個可被允許的能量范圍,或者稱能帶。擁有足夠能量可以在材料中自由流動的電子位于導帶。空穴則在低能帶(稱為“價帶”)流動,從一個原子流向另一個原子,很大程度上就像,由于附近的汽車不斷開進開出,一個空停車場可能變成一個停滿車的停車場。 這些能帶都是固定的,但我們可以改變與之相關的能量,通過添加雜質或者摻雜原子的方式使能量變高或者變低,從而改變半導體的傳導性。摻雜了額外電子的n型半導體傳導帶負電荷的電子;通過摻雜造成電子減少的p型半導體傳導帶正電荷的空穴。 如果我們將這兩種半導體類型結合到一起,就會得到一個錯位的能帶,從而創造了一個介于兩者之間的能壘。為制造一個MOSFET,我們在兩個互補類型之間注入一種材料,采用n-p-n或者p-n-p的構形。這就在晶體管中間創造出了3個區域:源極(電荷由此進入組件)、溝道和漏極(電荷出口)。

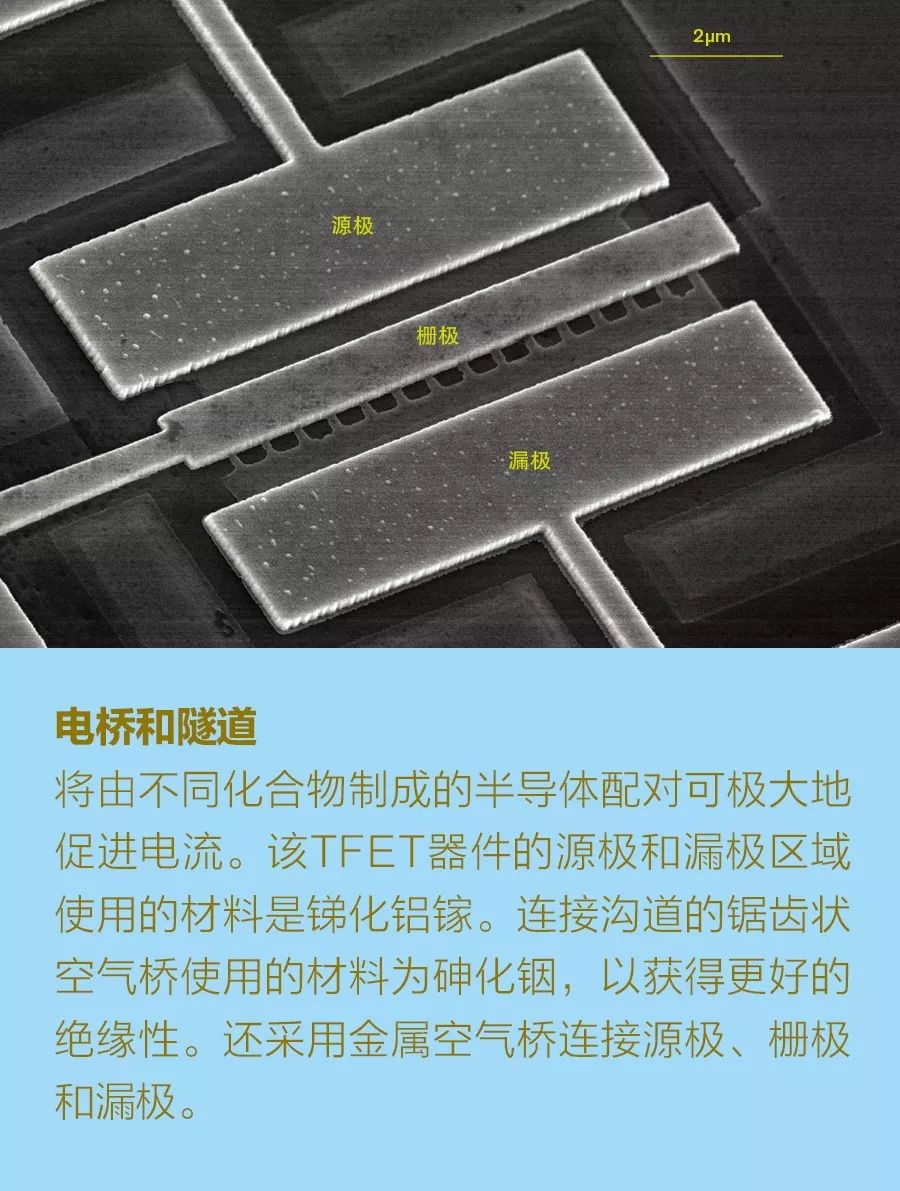

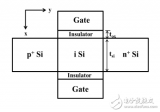

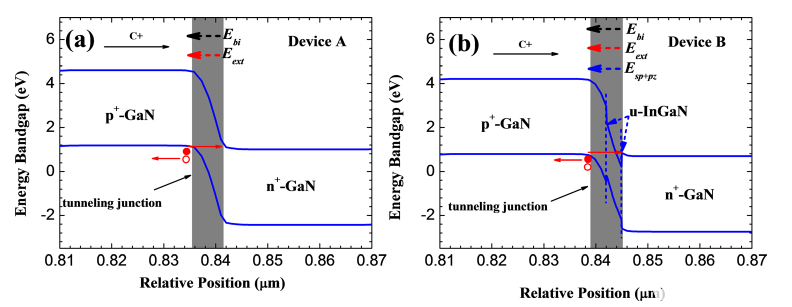

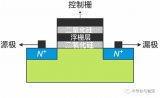

每個晶體管的兩個p-n結提供了電荷流動的電子能壘,而晶體管可以通過向溝道上方的柵極施加電壓來導通。向n溝道的MOSFET施加一個正電壓可使得溝道吸引更多的電子,因為它減少了電子向溝道移動所需的能量。向p溝道的MOSFET施加一個負電壓可以對空穴產生相同的效果。 這個簡單的降低能壘的方式是半導體電子中應用得最為廣泛的電流控制機制。二極管、激光、雙極晶體管、晶閘管和大部分場效應晶體管都利用了這種方式。但是這種方式有一個物理局限:晶體管需要一定量的電壓才可以被導通或者關斷。這是因為電子和空穴由于熱能的緣故一直處于運動中,而它們中能量最強的部分會溢出能壘。在室溫下,如果能壘減少60毫伏,流經能壘的電流就會增加10倍;每個“十進位”的電流變化需要60毫伏的變化。 所有這些電流泄漏都發生在低于器件的閥值電壓時。閥值電壓是導通晶體管所需的電壓。器件物理學家將這一能壘降低區域稱為亞閥值區域,而每十進位60毫伏的電壓被認為是最小亞閥值擺幅。為保持低水平能耗,應盡可能降低亞閥值擺幅。這樣器件導通所需的電壓就會減少,而當關斷時泄漏的電流就會減少。 亞閥值擺幅在過去不算是個大問題,當時芯片運行需要的電壓較高。但是現在,亞閥值擺幅開始對我們降低能耗的努力造成干擾。這部分是由于電路設計者希望確保他們的邏輯組件在定義“0”和定義“1”的電流之間有明顯區別。晶體管通常的設計是它們處于導通狀態時所載的電流是處于關斷狀態時所泄漏的電流的1萬倍。這就意味著要導通一個晶體管,需要至少向它施加240毫伏的電壓,即4個十進位的電流,因為每十進位需要60毫伏電壓。 在實踐中,CMOS電路使用的工作電壓通常要高得多,接近1伏。這是因為CMOS中最基礎的邏輯電路,即逆變器,采用的是兩個串聯晶體管。NAND柵極需要3個串聯晶體管,這就意味著其需要比逆變器更高的電壓。如果要進行調整以應對過程的可變性——意味著需要設置更寬的電壓裕度以應對器件與器件的差異——于是就需要如今所看到的接近1伏的電壓以確保運行。 這些對電壓的需求,加上泄漏的問題,意味著MOSFET微型化正日漸式微,沒有出路。如果我們想要進一步降低電壓以減少能量消耗,有兩個選擇(這兩個選擇都沒有什么吸引力):我們可以降低通過器件的電流,這會降低啟動速度,從而犧牲了性能;或者,可以保持電流的高水平,同時在關斷的時候允許更多電流向器件外泄漏。 這就是可以利用TFET之處。與在MOSFET中提高或降低源極和漏極之間的物理能壘不同,在TFET中我們采用柵極來控制能壘的實際電厚度,從而控制電子通過能壘的可能性。 這個做法的奧妙還是在于p-n結——但進行了一些扭轉。在一個TFET中,半導體材料被安置在p-i-n和n-i-p的構形中。其中“i”代表“固有”,意味著溝道擁有和空穴一樣多的電子。固有狀態與一個半導體所擁有的最大電阻率相對應。它同時提高與溝道內的能帶相關的能量,形成一個源極內的電荷載子不太可能穿過的厚能壘。 電子和空穴都遵守量子力學定律,這意味著它們的大小是模糊不定的。當能壘的厚度不到10納米時,一開始在能壘一側的電子就不太可能(但并非完全不可能)出現在另一側。 在TFET中,我們通過在晶體管柵極上施加電壓的方式來提高這種可能性。這使得源極內的導帶和溝道內的價帶重疊,開啟了一個隧穿窗口。要注意的是,在一個TFET中,電子在移動至溝道時在導帶和價帶之間隧穿。這與MOSFET中發生的情況形成鮮明對比。在一個MOSFET中,電子或者空穴主要是在一個帶或者另一個帶中穿行,一路從源極穿過溝道,最后到達漏極。 由于隧穿機制不是由能壘上的載流子流動所控制的,啟動TFET所要求的電壓擺幅可以比MOSFET小很多。只需施加足夠制造或移動一個使導帶和價帶交叉或不交叉的重疊的電壓足矣。(見插圖“關斷和導通”。)

-

MOSFET

+關注

關注

147文章

7242瀏覽量

214277 -

晶體管

+關注

關注

77文章

9746瀏覽量

138914

原文標題:隧穿晶體管

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電子新紀元:不使用半導體的晶體管

關于隧穿二極管( RTD)的問題

隧穿場效應晶體管是什么_隧穿場效應晶體管的介紹

什么是晶體管 晶體管的分類及主要參數

什么是達林頓晶體管?

氮化鎵晶體管GaN的概述和優勢

東芝面向超低功率MCU開發隧穿場效應晶體管

7nm制程工藝或為物理極限 1nm晶體管又是怎么回事

隧穿場效應晶體管是什么_隧穿場效應晶體管的介紹

帶間隧穿結的若干種架構及其應用的詳細講解

?量子隧穿會超光速嗎?

浮柵晶體管的組成結構以及原理

隧穿晶體管的原理及優勢

隧穿晶體管的原理及優勢

評論