縱觀歷史,但凡能夠大幅提升生產力的技術必將大規模應用并深刻改變社會發展進程。以大模型為代表的新AI第一次使智能體具備了主動學習和泛化能力,為生產力的發展帶來質的飛躍,未來數字世界和物理世界的絕大多數事物都將接入大模型新AI,進行智能化升級,引發新一輪工業革命。

互聯網和移動互聯網的發展歷史表明,越貼近用戶,其應用場景越大,產業價值越高。大模型最大的應用場景在終端和邊緣端。未來所有的終端和邊緣端設備都值得用大模型重新做一遍,為數十萬億規模的電子信息制造業提供增量市場和高質量發展的機遇。

大模型需要在資源有限的終端設備上高效運行,對芯片的AI部署通用性、易用性、經濟性等提出了更高的要求。進迭時空的實踐表明,RISC-V作為開源開放的下一代計算架構,以通用CPU核為基礎,結合少量DSA定制和大量微架構創新,不僅具備完整CPU功能,更擁有強大的原生AI算力,可以為端側大模型落地應用提供全新的解決方案。

1

RISC-V新CPU提供強大的AI通用性

進迭時空SpacemiT Key StoneK1憑借其開放性和可編程性,能夠輕松接入ONNXRuntime等主流開源生態。這一特性不僅降低了部署大量現有AI模型的門檻,還天然支持了timm、onnx modelzoo、ppl modelzoo等開源模型倉庫的模型,以及所有的公開onnx模型。這意味著,無論是傳統的小模型還是當下火熱的大模型,如qwen系列、llama系列、minicpm系列、phi系列、chatglm系列、gemma系列等,都能在這款AI CPU上得到高效支持。

尤其是,進迭時空SpacemiT Key StoneK1的原生AI算力具有極強的可編程性,支持主流低bit量化方式,從而極大地降低了大模型的帶寬需求。K1芯片運行主流的5億參數大模型可以實現每秒20個token的優異性能。

2

RISC-V新CPU提供強大的AI便捷性

借助主流開源生態,進迭時空不僅擴充了模型倉庫,還實現了低成本的遷移ONNXRuntime生態中的各種案例。此外,通過云端通用AI助手,用戶只需通過自然語言描述,即可實現AI部署。由于AI CPU支持全集ONNX算子,用戶只需修改模型路徑和攝像頭設備號,即可成功進行部署,極大地簡化了操作流程。

3

RISC-V新CPU構建本地大模型推理應用

進迭時空在SpacemiT Key StoneK1芯片上構建了以通義千問(qwen2.5-1.5B-coder)為基礎的本地AI助手。借助本地AI助手,用戶可以通過自然語言描述實現AI部署,無需依賴網絡連接,進一步提升了AI應用的便捷性和安全性。

未來,進迭時空將繼續堅持RISC-V+AI技術路線,通過技術創新帶來更具競爭力的解決方案,為大模型在終端和邊緣端的普及提供強有力的支持。

來源:進迭時空

-

cpu

+關注

關注

68文章

10905瀏覽量

213029 -

RISC-V

+關注

關注

45文章

2324瀏覽量

46596 -

大模型

+關注

關注

2文章

2551瀏覽量

3171

發布評論請先 登錄

相關推薦

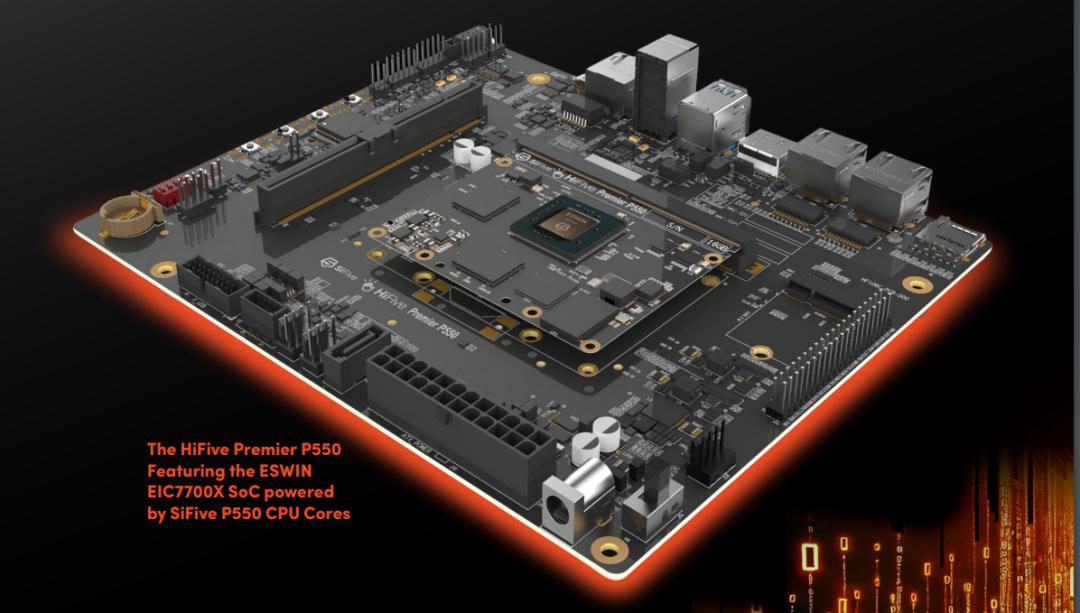

SiFive 推出高性能 Risc-V CPU 開發板 HiFive Premier P550

RISC-V,即將進入應用的爆發期

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

建設進展 | 全球首家 RISC-V 開源創新中心落地深圳

RISC-V為何如此重要?

IC咖啡沙龍“芯未來”公益講座丨仇健樂:RISC-V指令架構賦能端側智能芯片產業化落地

解鎖RISC-V技術力量丨曹英杰:RISC-V與大模型探索

瑞薩推出采用自研CPU內核的通用32位RISC-V MCU 加強RISC-V生態系統布局

RISC-V 基礎學習:RISC-V 基礎介紹

Imagination:RISC-V CPU的重要力量

RISC-V新CPU為端側大模型落地應用提供新范式

RISC-V新CPU為端側大模型落地應用提供新范式

評論