雖然對系統級芯片開發人員來說電源管理的重要性越來越高,但有個關鍵區域經常被忽視,那就是互連。雖然大多數電源管理工作集中于SoC的運算部分,但采用更加模塊化互連的設計師可以減小裸片尺寸、減輕布線擁塞,這就可以將總的芯片功耗最多降低達0.7mw。如此顯著的功耗下降將成為下一代移動和功耗敏感性數據中心應用系統中的游戲規則改變者。

模塊化概念有別于其它類型的互連,因為它由分布式架構的開關、緩沖器、防 火 墻、管線結構以及時鐘和電源域交叉組成。通過在芯片上的所有獨立單元之間使用通用傳輸協議,模塊化方法可以幫助設計師實現單元級時鐘選通,從而消除沒有事務處理區域的時鐘樹開關功耗。

模塊化片上網絡級芯片(NoC)技術還能通過邏輯局部化、盡量縮短長的走線并保持低電容來降低功耗。想要進一步增強SoC設計的電源管理能力的設計師可以采取一定的措施減小芯片的面積和泄漏功耗,方法是使用NoC傳輸協議的簡易性實現數據路徑的串行化,進而最大程度地減少邏輯用量。

低功耗

目前常用的頂層互連結構一般都要依賴于較長的走線,而這些走線會消耗與它們在芯片上占用的邏輯區域面積不成比例的功耗。時鐘樹通常是互連內最大的功耗源,而時鐘選通提供了降低功耗的最大潛力。另外,漏電功耗是第二大功耗源,減小這種結構所需的邏輯面積可以最大限度地減小漏電功耗。

采用模塊化NoC互連的設計師可以從本文中了解到時鐘樹管理的局部化、數據路徑的串行化和精確定位的管線結構所帶來的功耗和面積方面的好處。

總線和交叉矩陣:互連歷史簡介

了解互連結構的歷史就能知道模塊化NoC設計的由來了,它能解決可擴展性問題。

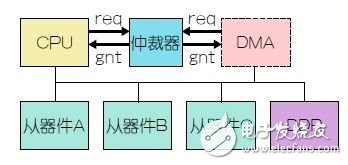

SoC是一種含CPU和外設的芯片,開發人員提出的接口協議標準可以將各單元鏈接在一起。借助新增總線主器件的推出,到外設的連接可以得到共享。控制對總線的訪問要求一個中央仲裁器,比如在板級協議中使用的仲裁器。

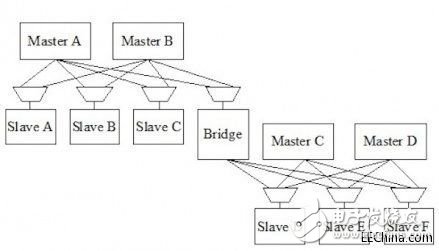

圖1:帶仲裁器的共享型總線展示了訪問控制為何要使用中央仲裁器。

隨著時間的推移,SoC設計增加了越來越多的IP內核。由于這些設計變得越來越復雜,他們要求更多的總線接口。當對接口進行密集操作時,總線主器件可能會浪費很多時間等待對總線的訪問權,即使在不同的主器件請求操作不同的從器件時,也是如此。

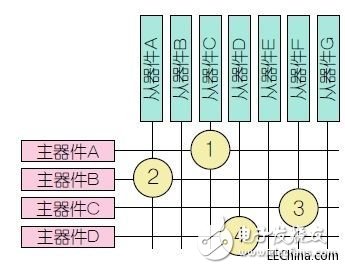

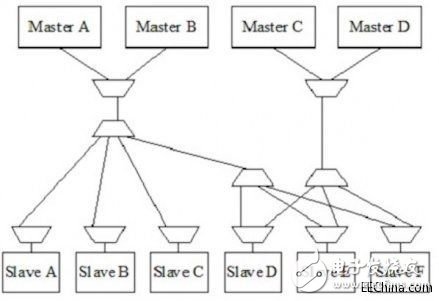

為了解決等待延時問題,交叉矩陣開關應運而生,它們支持在片上互連內不同的主和從器件之間開展并行訪問。下面這個邏輯框圖顯示了4個主器件同時對4個不同從器件進行事務操作。

圖2:SoC設計中的交叉矩陣開關邏輯視圖,展示了每個從器件端復用器的關系。

從物理上看,交叉矩陣開關是用每個從器件端的復用器(mux)實現的。每個復用器以分布式仲裁機制與仲裁器相耦合。

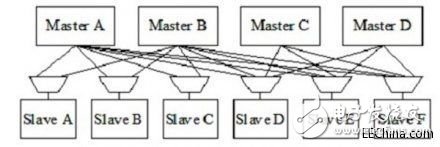

圖3:4個主器件、6個從器件的交叉矩陣實現表明,在SoC周圍采用完整數據路徑的尺寸路由是不切實際的。

這種方法最多只能擴展到幾個主和從器件接口。然而,除了特定數量外,在SoC周圍路由完整數據路徑的尺寸對布局布線來說也變得不切實際。

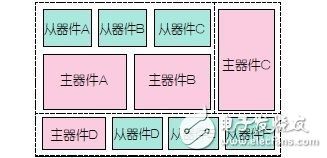

圖4:隨著功能清單的增長和IP模塊的增加,SoC底層規劃變得更加復雜。

對于具有很多個主/從接口的更加復雜的芯片來說,有必要在多個物理區域設計獨立的互連,具體取決于IP內核分組的布局情況。不同區域之間的橋接提供了主器件和從器件之間必要的互連。

圖5:4個主器件與6個從器件的互連,用了一個橋承載邏輯延時開銷。

橋會為數據處理的增加延時周期,因為它們承載了邏輯延時部分。

交叉矩陣互連可以解決并行訪問帶來的系統架構問題,但在有大量主和從IP模塊的情況下,又會造成芯片中的物理實現問題。

模塊化設計和NoC

為了減小延時,地址可以在主接口側解碼,并轉換為簡單的路由ID號。片上的仲裁器-復用器和路由器-解復用器網絡可以使用簡單的路由ID,并通過鏈路芯片周圍的簡單偽開關復用器擴展路由分布。這樣做還能實現更好的互連邏輯布局。對于芯片中越來越多的走線來說,布局越來越重要,因為它會使路由更加容易。

NoC互連可以同時解決這兩個問題,因此在手機應用處理器、數字電視和機頂盒控制器等先進設計中得到了廣泛使用。

圖6:利用一個NoC實現的4個主器件與6個從器件的互連。

設計師一直被要求在SoC中集成更多的功能,因此對互連技術的需求與日俱增。為了跟上形勢,對以下功能的需求非常迫切:

●到不同事務處理協議的接口

●開關(解復用-路由器和仲裁器-復用器)

●QoS(優先級)

●緩沖器

●數據路徑串行化

●統計性探測

●調試跟蹤

●防 火 墻

●寄存器片(管線結構)

●時鐘域交叉

●電壓域

●電源域

這對互連設計提出了新的挑戰。設計師希望IP可以重復使用并且可以重復配置。而在交叉矩陣邏輯中支持不斷增加的功能要求將會提高復雜性,減慢關鍵路徑速度。另外,許多走線即使在少量數據操作時也會被觸發,因此消耗了與之不成比例的功耗。然而,可復用的模塊化互連設計在簡便性、速度、面積和功效方面有很大的優勢,可克服傳統總線和交叉矩陣技術的復雜性。

事務、傳輸和物理層

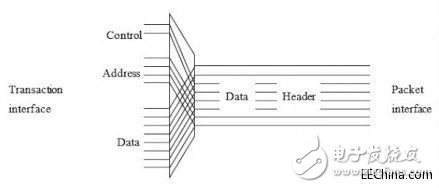

NoC技術采用了一種三層協議,其中事務層作為最高層。該技術使用AMBA、PIF、OCP或其它工業標準協議執行所要求的讀寫操作,同時也是對于通過互連連接的IP模塊的設計師來說,也是可見的接口。

NoC中的傳輸層協議由網絡接口單元(NIU)進行管理。它為每個事務創建一個或多個數據包。所有數據包都一個包頭。讀數據包和寫數據包都在包頭后包含數據載荷。包頭將地址、事務參數和邊帶信號作為域進行解碼。NIU控制顯著的事務和帶標簽的序列。包頭格式是最小的,并針對每個NoC作了不同程度的優化。包頭在互連內的每個偽開關處將來自發起者的請求路由到目標,并將來自目標的響應路由到發起者。請求和響應路徑是獨立的,因此可以消除邏輯和架構方面的依賴性,從而避免死鎖。

圖7:將地址/控制信號與事務接口和包傳輸接口間的數據復用起來可以簡化互連設計。

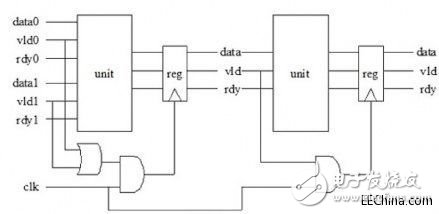

模塊化設計支持使用非常簡單的協議在物理層上傳輸傳送包。這種協議由以下信號組成:

●Data [N 位] (由發送者驅動)

●Valid [1 位] (由發送者驅動)

● Ready [1 位] (由接收者驅動)

“Valid”和“Ready”實現流程控制,支持后壓式反饋。這種簡單的握手協議存在于NoC的所有單元之間。簡單接口標準化后允許所有單元可交換地連接在一起,就像兒童的積木一樣。

時鐘樹選通

利用眾所周知的芯片設計方法,可以在不要求觸發的周期內選通每個觸發器端的時鐘。這種方法適用于采用所有互連技術的觸發器,不過不能解決時鐘樹功耗問題。

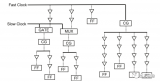

時鐘樹是個單一信號,因此比數據路徑要窄得多。然而,為了到達所有物理上分布的觸發器,時鐘樹比每個數據路徑位有多得多的基本特征。根據定義,時鐘在每個時鐘周期內會觸發兩次,因此時鐘樹的功耗一般要顯著大于數據路徑。

在交叉矩陣中,每個時鐘網絡即使在數據不流動時也會觸發。雖然理論上在交叉矩陣中的任何地方都沒有數據傳送時仍能在周期中實現到所有交叉矩陣邏輯的時鐘選通,但有些不切實際。它要求對多個遠端信號進行大的時鐘選通復用,以產生激活信號并回送至多個遠端觸發器。

因此,用組合邏輯的最簡模塊搭建互連可以實現單元級時鐘選通功能,并且其顆粒遠比單片交叉矩陣中的精細得多。

圖8:通過模塊化方法搭建互連就可以使用組合邏輯的單元級時鐘選通功能。

只有在有效的握手信號有效時單元內和單元間的寄存器才會觸發,用于指示數據業務的存在。選通邏輯對每個單元來說是局部的,因此路徑更短,并且最大限度地減少了產生激活信號所需的復用電路。時鐘選通是分布式的,模塊化互連的每個模塊在空閑時鐘周期時關閉,而不管系統余下部分的狀態。這樣可以實現接近理想的最小開關功耗。

模塊化的其它好處

除了時鐘選通外,其它好處包括改進了混合式閾值電壓(Vt)綜合的使用、減少了漏電功耗、改善了邏輯簡易性,并實現了局部化。

在小模塊之間的任何地方插入管線結構以滿足最小延時時序要求提高了綜合工具收斂時序的能力。由于有更大的余量,綜合有效減少了從默認高Vt單元到更快的低Vt單元的路徑數量。這樣,模塊化設計單元之間的管線結構就能減少漏電功耗。另外,更容易的時序收斂也能改善EDA工具的使用,有助于實現最小面積方面的最優化(更小的裸片面積可減少漏電功耗)。

64位AXI事務接口協議要求至少272條走線。對于模塊化方法來說,一個64位數據包接口要求148條線(每個請求響應網絡中有64位數據+8字節激活+ready+valid=74)。因此,將事務打包并在發起者和目標傳輸時可以將芯片底層規劃內的走線數量減少1.8倍(272/148=1.8)。

因為這種方法針對單元之間的接口使用的是簡單物理層協議,所以很容易改變包數據的串行化處理。全部要求就是簡單的復用器和寄存器,以便減小數據路徑寬度。

改變數據路徑的串行化處理方式,使之不超過滿足芯片不同部分的帶寬要求所需的寬度,可以減少芯片所有部分的互連邏輯面積,而且這些芯片都要求小于最大帶寬。一般來說,大多數芯片中的絕大部分頂層互連不要求最大帶寬。

局部化

將接口之間的復用器等單元實現局部化處理后,單元之間的走線平均長度將變短。這意味著走線電容使得電流的消耗變得更小。這樣還能簡化后端版圖工藝,因為它能減少遠距離放置的邏輯之間對連接的依賴性。

機頂盒(STB)SoC上的結果

支持1080p120幀的中端機頂盒SoC就使用了模塊化NoC互連,它展示了模塊化方法的優勢。這種模型使用了11個主器件和6個從NIU的互連,消耗的邏輯面積是183k個門。

我們分析了三種時鐘選通式開關活動場景。首先是最差的視頻處理場景,其中被設為120Hz顯示輸出的視頻解碼器和CPU是系統的主要負載,它們消耗了幾乎所有可用的DDR內存帶寬。

第二種場景則呈現了普通案例視頻解碼器的復雜性。第三種場景沒有視頻解碼,只是用網絡瀏覽方式,可實現每秒30幀的中等顯示刷新率。

交叉矩陣在DDR活動期間的每個周期都必須要激活,因此在第一種情況下模塊化設計通過觸發DDR活動可以降低2.3倍的功耗,第二種情況是2.5倍,第三種情況是3.4倍。

在待機場景,模塊化NoC互連展示了比交叉矩陣更強的觸發節省效果。另外,更大的芯片有更多的主NIU邏輯要訪問同樣受限的共享資源。這些芯片需要用更大比例的時間選通更多數量的觸發器。因此對模塊化NoC設計來說觸發節省效果隨著芯片尺寸的增加而增強。

減少時鐘樹功耗

模塊化NoC可以極大地降低高集成度芯片中頂層互連結構的功耗。通過局部化時鐘選通功能,時鐘樹只在數據傳送的路線上并且只在傳送周期內有功耗。這樣可以顯著降低時鐘樹的功耗。另外,局部的串行化處理從最大程度地減少了支持每條鏈路的帶寬要求所需的數據路徑邏輯。這又進一步減小了漏電面積。另外,模塊化支持更加精細的管線顆粒,可以更好地收斂時序且不浪費余量。這又進一步允許綜合工具使用更小、更加高效的門。

-

SoC設計

+關注

關注

1文章

148瀏覽量

18817 -

NoC

+關注

關注

0文章

38瀏覽量

11766

發布評論請先 登錄

相關推薦

射頻識別芯片設計中時鐘樹功耗的優化與實現

前后端協同的時鐘樹設計方法

時鐘網格與時鐘樹設計方法對比研究

基于CCopt引擎的SMIC40nm低功耗工藝CortexA9的時鐘樹實現

射頻識別芯片設計的時鐘樹功耗實戰

什么是門控時鐘 門控時鐘降低功耗的原理

STM32F10X-時鐘樹詳細介紹

STM32時鐘樹

降低時鐘樹功耗

降低時鐘樹功耗

評論