今天我們要介紹的時(shí)序基本概念是Timing arc,中文名時(shí)序弧。這是timing計(jì)算最基本的組成元素,在昨天的lib庫(kù)介紹中,大部分時(shí)序信息都以Timing arc呈現(xiàn)。如果兩個(gè)pin之間在timing上存在因果關(guān)系,我們就把這種時(shí)序關(guān)系稱為Timing arc,主要分為定義時(shí)序延遲,和定義時(shí)序檢查兩種。為啥叫它時(shí)序弧?因?yàn)闀r(shí)序圖中經(jīng)常用一條弧形線段來表示它。如下圖所示:cell的timing arc定義在lib中,net之間沒有timing arc, 它的delay則有RC參數(shù)計(jì)算而出。

時(shí)序延遲的Timing arc:有以下幾種

Combinational Timing Arc

Edge Timing Arc

Preset and Clear Timing Arc

Three State Enable & Disable Timing Arc

時(shí)序檢查的Timing arc:有以下幾種

Setup Timing Arc

Hold Timing Arc

Recovery Timing Arc

Removal Timing Arc

Width Timing Arc

首先看Combinational Timing Arc,Combinational Timing Arc 是最基本的Timing Arc。Timing Arc 如果不特別指明的話,就是屬于此類。如下圖所示,定義了從特定輸入到特定輸出(A到Z)的延遲時(shí)間。Combinational Timing Arc 的Sense有三種,分別是inverting(或 negative unate),non-inverting(或 positive unate)以及non-unate。當(dāng)Timing Arc 相關(guān)之特定輸出(下圖Z)信號(hào)變化方向和特定輸入(下圖A)信號(hào)變化方向相反(如輸入由0變1,輸出由1變0),則此Timing Arc 為inverting sense。反之,輸出輸入信號(hào)變化方向一致的話,則此Timing Arc 為non-inverting sense。當(dāng)特定輸出無法由特定輸入單獨(dú)決定時(shí),此Timing Arc 為non-unate。

其它的Timing Arc 說明如下。

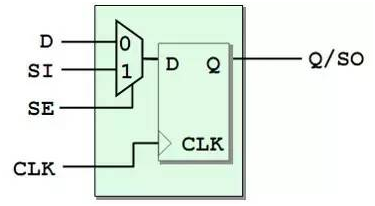

Setup Timing Arc:定義時(shí)序組件(Sequential Cell,如Flip-Flop、Latch 等)所需的Setup Time,依據(jù)Clock上升或下降分為2類(圖五)。Hold Timing Arc:定義時(shí)序組件所需的 Hold Time,依據(jù)Clock 上升或下降分為2類(圖六)。Edge Timing Arc:定義時(shí)序組件Clock Active Edge 到數(shù)據(jù)輸出的延遲時(shí)間,依據(jù)Clock上升或下降分為2類(圖七)。Preset and Clear Timing Arc:定義時(shí)序組件清除信號(hào)(Preset或Clear發(fā)生后,數(shù)據(jù)被清除的速度,依據(jù)清除信號(hào)上升或下降及是Preset或Clear分為4類(圖八)。這個(gè)Timing Arc 通常會(huì)被取消掉,因?yàn)樗鼤?huì)造成信號(hào)路徑產(chǎn)生回路,這對(duì)STA而言是不允許的。Recovery Timing Arc:定義時(shí)序組件Clock Active Edge 之前,清除信號(hào)不準(zhǔn)啟動(dòng)的時(shí)間,依據(jù)Clock上升或下降分為2類(圖九)。Removal Timing Arc:定義序向組件Clock Active Edge 之后,清除信號(hào)不準(zhǔn)啟動(dòng)的時(shí)間,依據(jù)Clock上升或下降分為2類(圖十)。Three State Enable & Disable Timing Arc:定義 Tri-State 組件致能信號(hào)(Enable)到輸出的延遲時(shí)間,依據(jù)Enable或Disable分為2類。(圖十一)Width Timing Arc:定義信號(hào)需維持穩(wěn)定的最短時(shí)間,依據(jù)信號(hào)維持在0或1的位準(zhǔn)分為2類。(圖十二)

-

時(shí)序

+關(guān)注

關(guān)注

5文章

392瀏覽量

37427 -

時(shí)序弧

+關(guān)注

關(guān)注

0文章

1瀏覽量

1399

原文標(biāo)題:時(shí)序分析基本概念介紹——Timing Arc

文章出處:【微信號(hào):IC_Physical_Design,微信公眾號(hào):數(shù)字后端IC芯片設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

時(shí)序分析基本概念介紹——時(shí)序庫(kù)Lib,除了這些你還想知道什么?

【時(shí)序約束資料包】培訓(xùn)課程Timing VIVADO

時(shí)序分析的基本概念ETM的詳細(xì)介紹及如何應(yīng)用的資料概述

時(shí)序分析和時(shí)序約束的基本概念詳細(xì)說明

FPGA設(shè)計(jì)中時(shí)序分析的基本概念

時(shí)序分析概念min pulse width介紹

時(shí)序分析基本概念介紹<Latency>

介紹時(shí)序分析基本概念MMMC

時(shí)序分析Slew/Transition基本概念介紹

時(shí)序分析基本概念介紹—時(shí)序庫(kù)Lib

時(shí)序分析基本概念介紹—花一樣的“模式”

詳細(xì)介紹時(shí)序基本概念Timing arc

詳細(xì)介紹時(shí)序基本概念Timing arc

評(píng)論