SiO?膜層鍍膜過程中出現(xiàn)的膜裂問題,可以通過多種方法來解決。以下是一些主要的解決策略:

1. 優(yōu)化鍍膜工藝

- 蒸發(fā)速度控制 :蒸發(fā)速度的設置對膜層厚度有直接的影響,進而影響膜層的應力和均勻性。需要根據(jù)材料的熔點和熔液粘度等因素,通過實驗確定最佳的蒸發(fā)速度。

- 蒸發(fā)溫度選擇 :蒸發(fā)溫度應高于材料的熔點,以確保材料充分蒸發(fā)。過低的溫度可能導致材料揮發(fā)不充分,影響膜層質量。

- 裝量控制 :裝量的大小影響蒸發(fā)速度的穩(wěn)定性和膜層厚度的均勻性。需要通過精準的稱重、體積計量或流量計來控制裝量。

2. 應力管理

- 應力匹配 :通過調整SiO?薄膜的鍍膜工藝,改變其應力匹配狀態(tài),從而控制膜裂。例如,可以調整鍍膜過程中的溫度、壓力等參數(shù),使薄膜的應力分布更加均勻。

- 吸潮控制 :SiO?薄膜在大氣中久置會由于吸潮而發(fā)生應力變化,導致膜裂。因此,在鍍膜后應及時對薄膜進行干燥處理,并儲存在干燥的環(huán)境中,以減少吸潮對薄膜應力的影響。

3. 退火處理

- 退火是一種有效的消除薄膜應力的方法。通過控制退火溫度和時間,可以使薄膜內部的應力得到釋放,從而提高薄膜的穩(wěn)定性和抗裂性。需要注意的是,退火溫度和時間的選擇應根據(jù)具體材料和工藝要求來確定。

4. 膜層厚度控制

- 膜層厚度與反射率成反比,因此需要根據(jù)實際需求選擇合適的膜層厚度。同時,膜層厚度的均勻性也是影響薄膜質量的重要因素之一。在鍍膜過程中,需要采用合適的工藝參數(shù)和操作方法,確保膜層厚度的均勻性。

5. 設備和環(huán)境控制

- 確保鍍膜設備處于良好的工作狀態(tài),定期進行維護和保養(yǎng)。同時,保持鍍膜環(huán)境的清潔和穩(wěn)定,避免雜質和污染物的引入對薄膜質量造成影響。

綜上所述,解決SiO?膜層鍍膜過程中的膜裂問題需要從多個方面入手,包括優(yōu)化鍍膜工藝、管理應力、進行退火處理、控制膜層厚度以及確保設備和環(huán)境的穩(wěn)定性等。通過綜合應用這些方法,可以顯著提高SiO?薄膜的質量和穩(wěn)定性。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

參數(shù)

+關注

關注

11文章

1859瀏覽量

32427 -

鍍膜

+關注

關注

1文章

32瀏覽量

10655 -

SiO2

+關注

關注

0文章

22瀏覽量

8545

發(fā)布評論請先 登錄

相關推薦

sio2_sio2是什么意思

在自然界中sio2二氧化硅的存在是非常廣泛的,本內容解釋了sio2是什么意思,sio2的物理性質是什么,讓大家充分了解sio2

發(fā)表于 12-13 10:41

?2.1w次閱讀

VirtualLab Fusion應用:氧化硅膜層的可變角橢圓偏振光譜(VASE)分析

al., Proc. SPIE 10294, 1029402 (1999)

仿真結果與參考文獻的比較

被研究的SiO2層厚度變化為1埃時,?和?的差異。

發(fā)表于 02-05 09:35

【轉】無感電阻中金屬膜電阻與碳膜電阻的區(qū)別

金屬膜電阻它所需是采用的材料就是鎳鉻或者是相類似的合金。做法就是將合金通過高溫真空鍍膜技術將其僅僅的附在基體的表面上形成皮膜,接著將阻值調整到最精確之后,在表面涂上一層環(huán)氧樹脂進行保護即可。碳

發(fā)表于 07-27 22:13

芯片制作工藝流程 一

芯片制作工藝流程 工藝流程1) 表面清洗 晶圓表面附著一層大約2um的Al2O3和甘油混合液保護之,在制作前必須進行化學刻蝕和表面清洗。2) 初次氧化 有熱氧化法生成

發(fā)表于 08-16 11:09

透明導電膜玻璃有什么用途?

透明導電膜玻璃是指在平板玻璃表面通過物理或化學鍍膜方法均勻的鍍上一層透明的導電氧化物薄膜而形成的組件。對于薄膜太陽能電池來說,由于中間半導體層幾乎沒有橫向導電性能,因此必須使用透明導電

發(fā)表于 10-29 09:00

真空電弧離子鍍膜方法沉積類金剛石膜在PMMA樹脂義齒表面的應

采用電弧離子鍍膜方法,以高純石墨為碳離子源在PMMA樹脂義齒表面沉積類金剛石膜。應用xps譜和Raman譜對膜層的結構進行了理論分析,對鍍膜

發(fā)表于 04-26 22:20

?29次下載

多層膜界面結構探測技術

分別以丙醇鋯和正硅酸乙酯為原料,采用溶膠-凝膠工藝制備了性能穩(wěn)定的ZrO2和SiO2溶膠。用旋轉鍍膜法在K9玻璃上分別制備了SiO2單層膜、

發(fā)表于 03-03 13:50

?21次下載

鍍復SiO2膜的電容器介質膜

鍍復SiO2膜的電容器介質膜

成功一種能在幾百小時連續(xù)沉積SiO2膜的新穎電子束蒸發(fā)裝置,獲國家發(fā)明專利,在此基礎上

發(fā)表于 12-08 09:03

?821次閱讀

碳膜電阻和金屬膜電阻的區(qū)別

碳膜電阻器是采用高溫真空鍍膜技術將碳緊密附在瓷棒表面形成碳膜,然后加適當接頭切割,并在其表面涂上環(huán)氧樹脂密封保護而成的。金屬膜電阻器就是以特種金屬或合金作電阻材料,用真空蒸發(fā)或濺射的方

發(fā)表于 01-24 09:41

?8.6w次閱讀

手機鍍膜的功能,實驗證明一切!比鋼化膜牛!

手機鍍膜的原理。納米鍍膜打破了人們對傳統(tǒng)保護膜的認知,它是一款液體的納米鍍膜,采用最先的德國納米技術,只需3個簡單步驟,5分鐘內即可涂抹完成。在涂抹完成之后,能再屏幕上形成晶瑩靚麗的隱

發(fā)表于 08-13 14:09

?2173次閱讀

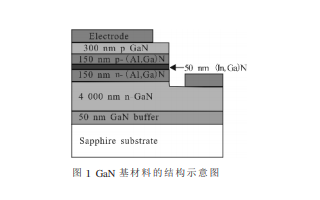

PECVD沉積SiO2和SiN對P-GaN有什么影響

在等離子增強化學氣相沉積法PECVD沉積 SiO2和 SiN掩蔽層過程中!分解等離子體中濃度較高的H原子使MG受主鈍化!同時在P-GaN材料表面發(fā)生反應形成淺施主特性的N空位。

發(fā)表于 12-17 08:00

?17次下載

3D NAND的主要制作流程

SiO2與SiNx交替鍍膜,每層膜層在幾十納米左右。根據(jù)產(chǎn)品的不同,膜層的層數(shù)也不同。圖中只是示

發(fā)表于 03-19 12:26

?1113次閱讀

SiO2薄膜的刻蝕機理

本文介紹了SiO2薄膜的刻蝕機理。 干法刻蝕SiO2的化學方程式怎么寫?刻蝕的過程是怎么樣的?干法刻氧化硅的化學方程式? 如上圖,以F系氣體刻蝕為例,反應的方程式為: ? SiO2(s)+ CxFy

sio2膜層鍍膜如何解決膜裂

sio2膜層鍍膜如何解決膜裂

評論