本系列,我們的產品技術專家將結合電子系統設計軟件的新功能和應用熱點進行選題,本期主題為Xpedition Schematic Analysis 原理圖完整性分析工具簡介,敬請參閱!

如今的原理圖設計變得非常復雜,無法僅憑目視評審進行全面檢查。如果沒有適當的原理圖驗證,可能會導致額外的硬件重新設計、延遲上市時間、增加現場退貨率以及降低產品質量的風險。通過進行原理圖完整性分析,可以避免潛在的設計缺陷和邊際性問題。

Xpedition Schematic Analysis提供了預定義的檢查和廣泛的智能組件模型庫,能夠自動對原理圖上的所有網絡進行全面檢查,從而節省設計團隊數百小時的目視檢查和實驗室調試時間。

Xpedition Schematic Analysis原理圖完整性分析可以集成多個板設計的數據進行系統級驗證。它是一種基于規則且不限定CAD軟件的技術,可以與您的設計同時進行,提高設計質量,而不會影響硬件開發的進度。

使用Xpedition Schematic Analysis,可以在產品設計的早期階段通過原理圖網表和BOM來查找原理圖上的缺失或錯誤,從而避免在項目晚期浪費時間和材料。

由于對原理圖上的所有網絡進行全面檢查,Xpedition Schematic Analysis有可能發現僅使用仿真工具無法察覺的問題。以下是一些示例:

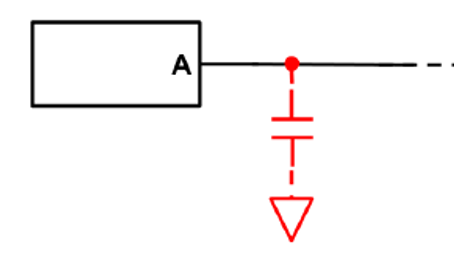

例如,某個IC的管腳根據廠家規范需要連接一個電容到地,如果在原理圖中未進行連接,將會觸發錯誤提示。

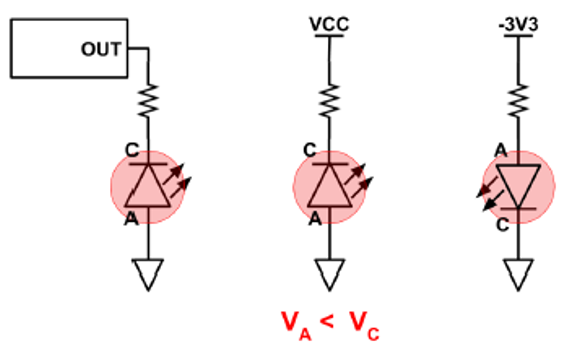

或者如下圖所示的二極管方向驗證。

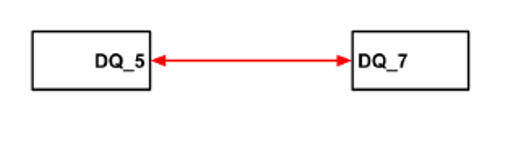

又或者是總線上的錯誤。如下圖所示,一個IC的bit 5連接到另一個IC的bit 7。

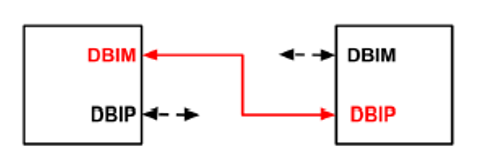

還有差分管腳驗證,例如下圖所示的差分對的正負兩端接反的情況。

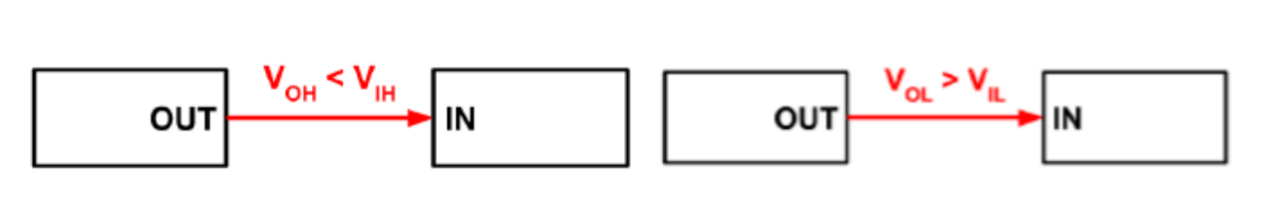

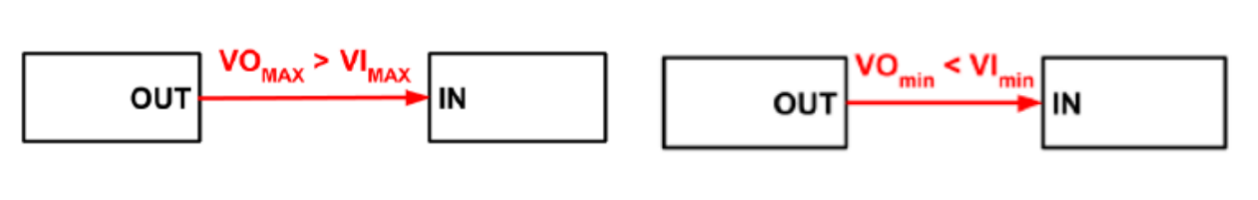

此外,還可以驗證組件的管腳電壓參數,包括最大、最小和邏輯閾值。例如,過高或過低的輸出電平可能導致接收端的邏輯位誤判:

或者過高或過低的電平輸出可能導致接收端組件損壞:

要進行這些類型的檢查,需要有相應的組件模型來提供每個管腳的特性和要求。Xpedition Schematic Analysis提供了一個包含數百萬個組件的在線模型庫,方便用戶使用。對于特殊的組件,用戶還可以利用付費咨詢服務或使用Xpedition Schematic Analysis提供的模板自行對有源或無源組件進行建模。

通過在原理圖捕捉過程中而不是之后進行全自動化的原理圖驗證,開發過程可以向左移動。其中一個明顯的好處是減少硬件重新設計,從而縮短設計周期和降低成本。

-

原理圖

+關注

關注

1300文章

6358瀏覽量

235159 -

電子系統

+關注

關注

0文章

438瀏覽量

31242 -

總線

+關注

關注

10文章

2903瀏覽量

88387 -

Xpedition

+關注

關注

0文章

19瀏覽量

8466

原文標題:Xpedition Schematic Analysis原理圖完整性分析工具簡介

文章出處:【微信號:gh_a47ef5dbc902,微信公眾號:西門子PCB及IC封裝設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB信號完整性分析入門

信號完整性與電源完整性的仿真分析與設計

Altium Designer中進行信號完整性分析

【下載】《信號完整性分析》

基于信號完整性分析的PCB設計流程步驟

電源完整性分析

Mentor Expedtion PCB信號完整性分析入門

信號完整性與電源完整性仿真分析

信號完整性分析

基于信號完整性分析的PCB設計解析

Xpedition Schematic Analysis原理圖完整性分析工具簡介

Xpedition Schematic Analysis原理圖完整性分析工具簡介

評論