來源:科技新報

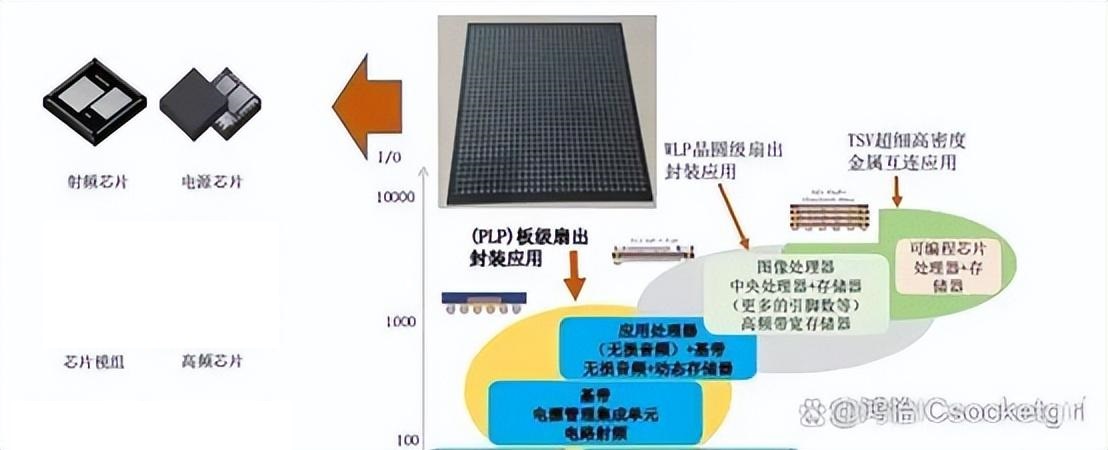

2024 年 Semicon Taiwan 國際半導體展完美落幕,先進封裝成為突破摩爾定律的關鍵,尤其以面板級扇出型封裝(FOPLP)成為備受關注的下一代技術,同時也是封測廠、面板廠極力布局的方向。

事實上,臺灣地區封測廠推動 FOPLP 已有七八年,但因為良率問題未見顯著成效,客戶也持觀望態度,因此沒有太多終端應用落地。然而,臺積電董事長魏哲家在 7 月 18 日法說會指出,正在研究 FOPLP 技術,預期三年后技術可成熟,無疑是給這項技術「添一把火」,內外地區設備商、封測廠、面板廠全熱起來,一起沖刺技術落地。

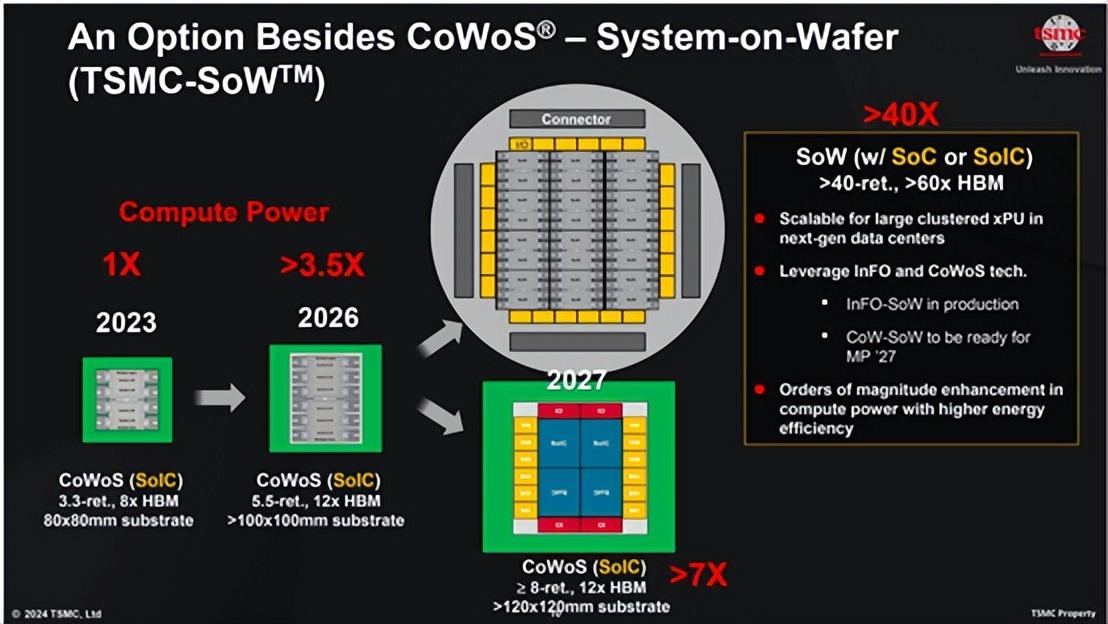

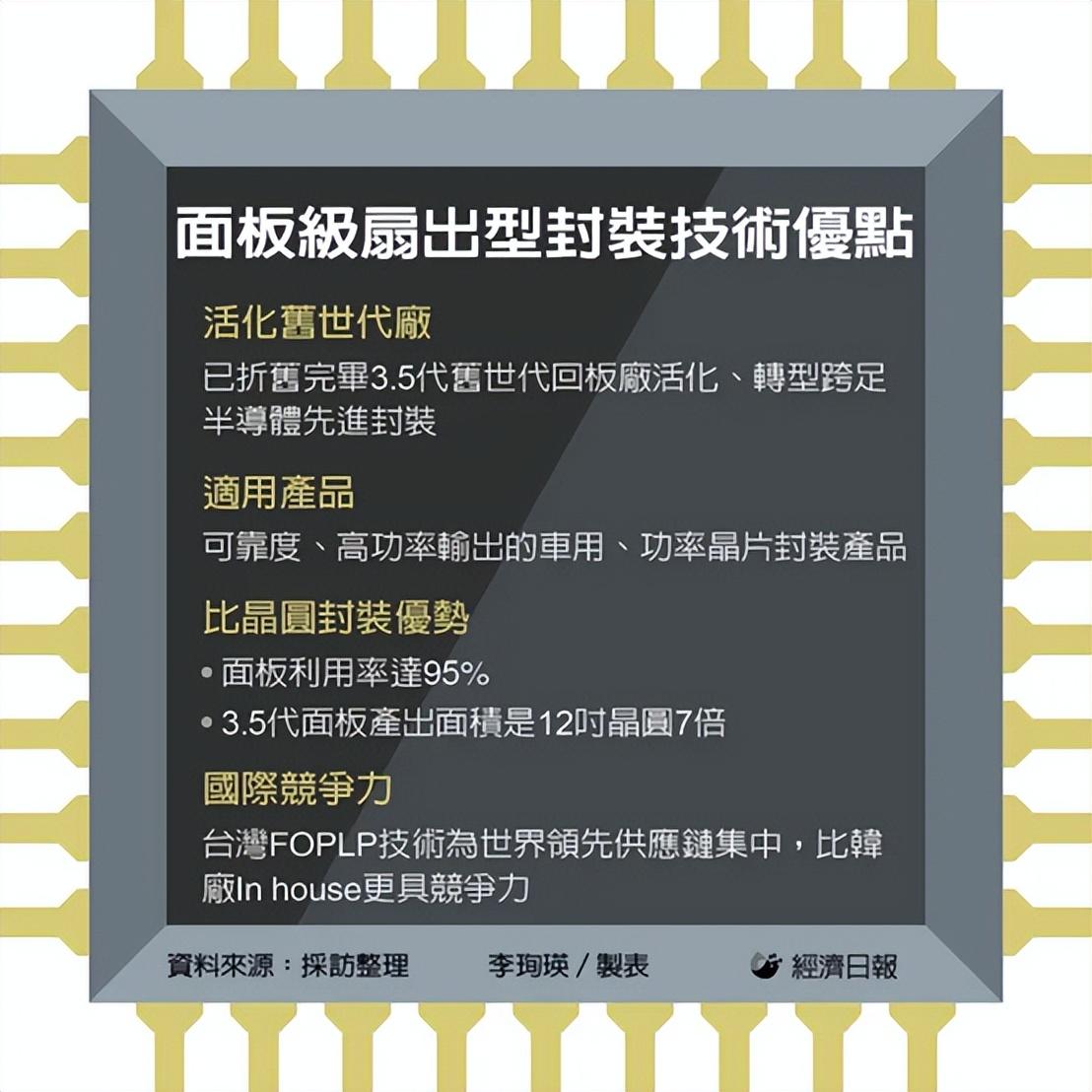

FOPLP 會取代 CoWoS 嗎?

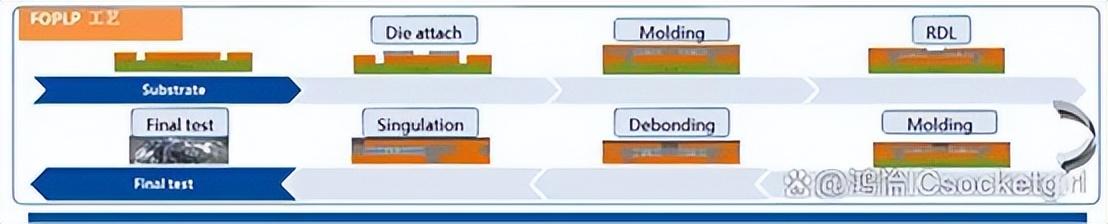

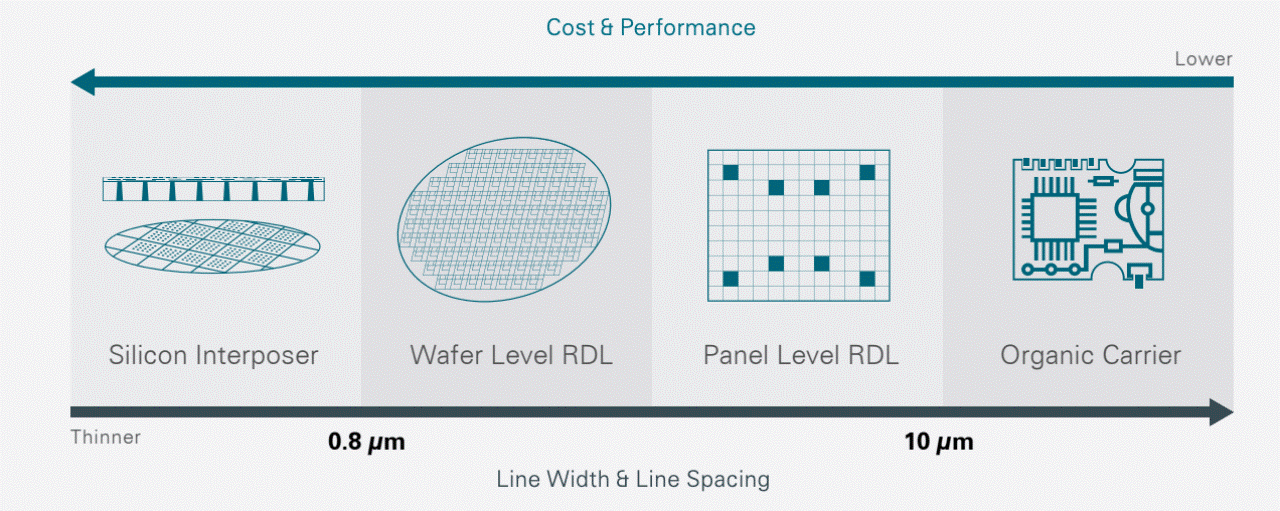

FOPLP 技術是 FOWLP 技術的延伸,以方形基板進行 IC 封裝,可使封裝尺寸更大、降低生產成本。據經濟部說法,以面板產線進行 IC 封裝,方形面積相較晶圓有更高的利用率,達到 95%,即相同單位面積下,可擺放更多的芯片數量。然而,因封裝尺寸更大,面臨面板翹曲、均勻性和良率問題。至于 FOPLP 的 Panel(面板)載板可采用 PCB 或者液晶面板用的玻璃載板,包括臺積電在內廠商都開始研究玻璃載板的可行性。

G3.5 FOPLP Glass Panel 生產面積。(Source:群創)

臺積電開發的 FOPLP 可想象成「矩形 InFO」,整合臺積電 3D fabric 平臺其他技術,發展出 2.5D / 3D 等先進封裝,以用于高階產品應用,最快 2027 年亮相。據日經報導,臺積電正與設備及原物料供應商合作研發面板級芯片封裝技術,目前仍在早期階段。據悉,試驗中的矩形基板尺寸為 510×515mm,但有消息稱新定案版本為 600×600mm。

半導體設備業者認為,FOPLP 生態鏈發展主要看臺積電,但隨著 AI 持續發展,在算力提升又必須兼顧成本的考量下,FOPLP 仍是未來需發展的方向。這項技術應該不會取代 CoWoS,而是提供客戶在成本考量下的新解決方案。

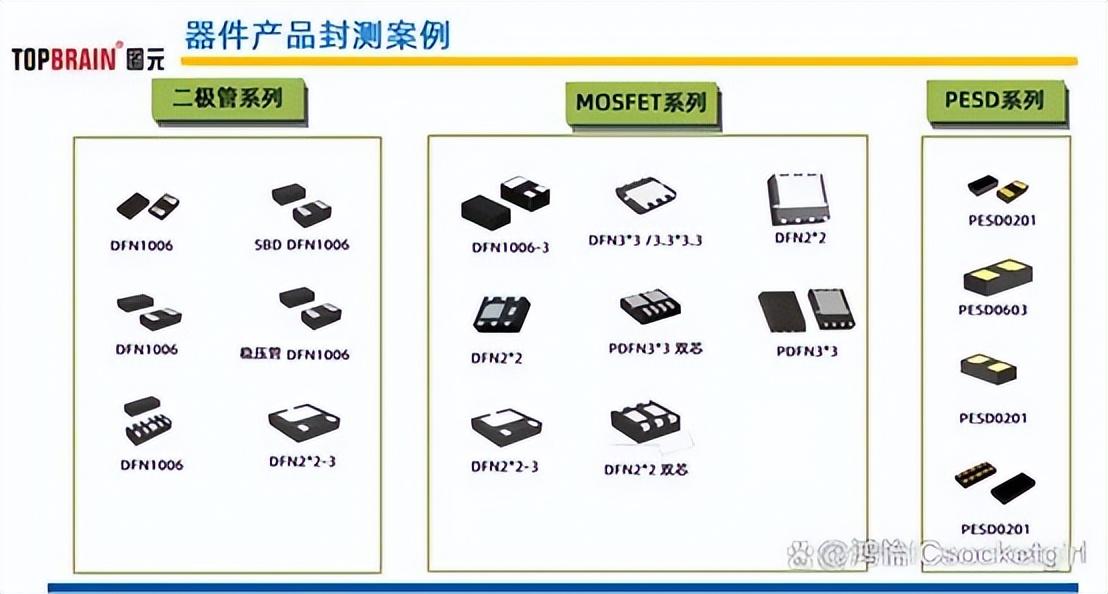

隨著半導體技術的迅猛發展,對芯片封裝工藝的要求也不斷增長。尤其是針對高頻、射頻、電源和傳感器等芯片的處理,封裝技術的發展顯得尤為重要。而在眾多封裝技術中,扇出型面板級封裝(Fan-Out Panel Level Packaging, FOPLP)以其獨特的優勢逐漸脫穎而出,成為行業的焦點。

FOPLP板級封裝技術特點

1. 擴展封裝面積

FOPLP技術將單個芯片及其周邊電路安裝在更大面積的材料面板上,形成扇出形狀。這種方法可以顯著減少芯片間連線的長度,從而降低傳輸損耗和訊號干擾,提高電性能。

2. 提高集成度

與傳統封裝技術相比,FOPLP能夠容納更多的芯片和功能集成在一起,適合于復雜的多芯片模組封裝。FOPLP通過增加面板面積來增加封裝密度,使得更多功能單元可以集成在有限的空間內,從而提高系統性能。

3. 優化熱管理

FOPLP技術在封裝過程中使用了更優質的熱導材料,通過合理設計提升散熱能力,降低芯片運行溫度,增強可靠性和壽命。

FOPLP在不同芯片類型中的應用

射頻芯片

在射頻芯片領域,FOPLP技術擁有顯著的優勢。射頻芯片對信號穩定性和降噪能力有很高的要求。FOPLP技術能夠更有效地隔離噪聲干擾,提供更好的信號傳輸路徑,同時通過封裝結構的優化提升信號質量和傳輸速率。

電源芯片需要高效的散熱性能,以及良好的電性能和機械強度。FOPLP技術通過高密度集成和優化散熱路徑,保障電源芯片在高功率條件下的穩定運行。此外,FOPLP技術還提供卓越的機械強度,確保封裝的穩定性和可靠性。

芯片模組

芯片模組是多種芯片協同工作的系統單元。FOPLP技術能夠通過集成多個芯片在一塊面板上,簡化模組設計,提高系統集成度。此外,FOPLP技術優化了芯片之間的互連結構,提高模塊的整體性能和可靠性。

高頻芯片

高頻芯片在通信設備中起著至關重要的作用,要求擁有高帶寬、低延遲和高信號傳輸質量。FOPLP技術在封裝過程中可以有效降低信號損耗,優化信號傳輸路徑,從而提高高頻芯片的性能和可靠性。

數字芯片

數字芯片涵蓋了處理器、控制器等核心組件。FOPLP技術通過改進封裝設計,提高芯片的散熱和電性能,使得數字芯片在工作過程中能夠更加穩定和高效地運行。

傳感器芯片

傳感器芯片用于檢測和反饋環境變化,對體積和能耗要求較高。FOPLP技術通過優化封裝面積和電路設計,提高傳感器芯片的靈敏度和精度,同時降低功耗和提升抗干擾能力。

FOPLP封裝對芯片測試的優勢

1. 更高的測試效率

FOPLP封裝由于集成度高、封裝面積大,能夠在一次測試過程中檢驗更多的芯片。相較于傳統封裝技術,FOPLP封裝顯著提高了測試效率和測試速度,降低測試成本。

2. 提供更全面的測試數據

由于FOPLP封裝技術優化了芯片之間的連接和信號傳輸路徑,使得在測試過程中能夠獲得更全面、更準確的測試數據,提供了更好的芯片性能評估基礎。

3. 改善散熱性能

在測試過程中,芯片的溫度管理尤為重要。FOPLP封裝技術通過優化散熱路徑,確保芯片在高功耗運行條件下的溫度控制,從而提高測試結果的準確性和穩定性。

4. 靈活的測試方案

FOPLP封裝技術具備高度的靈活性,因此可以根據不同芯片的特性和需求進行個性化的測試方案設計。無論是高頻芯片、射頻芯片還是電源芯片,FOPLP封裝技術都能夠提供適合的測試方案,保障測試結果的一致性和可靠性。

定制化測試座的必要性

盡管FOPLP封裝在許多方面展現了巨大的優勢,但在芯片測試過程中,測試座的設計和制造往往需要針對具體應用進行定制。這是因為不同類型的芯片及其應用場景對測試座的要求各不相同,包括:

1. 特定的電性和機械要求

不同類型的芯片在測試過程中需要具備特定的電性和機械要求。例如,高頻芯片需要具有優良的信號隔離能力,電源芯片需要良好的散熱性能等。因而,測試座的設計必須根據芯片的具體特性進行專門設計。

2. 高度靈活的連接結構

FOPLP封裝中的高集成度和多芯片共存特性,要求測試座需要具備高度靈活的連接結構,以適應不同芯片的測試需要。標準化的測試座往往難以滿足這一需求,因此定制化的設計成為必要。

3. 精確的數據采集和分析能力

高性能芯片對測試數據的精度和分析能力有著很高的要求,為了能夠精確采集和分析測試數據,測試座必須具備專業化和高精度的設計。標準產品無法完全滿足這一需求,必須根據具體芯片進行定制。#百家快評#

隨著芯片技術和封裝工藝的發展,FOPLP板級封裝憑借其優異的擴展性、高集成度和優化的熱管理能力,在射頻芯片、電源芯片、傳感器芯片等領域展現了顯著的技術優勢。同時,FOPLP封裝在芯片測試過程中具備更高的效率和更全面的數據獲取能力。但由于不同芯片在電性能、機械要求及連接結構方面的特性各異,測試座需針對具體應用進行定制,確保測試過程的準確性和可靠性。

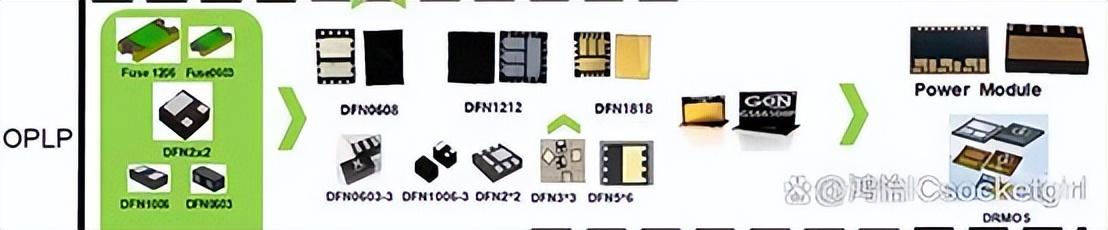

OSAT、面板大廠布局多年,2024 年逐步開花結果

臺積電布局 FOPLP 以前,早期投入這項技術的臺灣地區廠商包括力成、群創和日月光。力成 2018 年在新竹科學園區三廠開始興建,啟動全球第一座 FOPLP 量產基地,正式布局高階封裝領域。執行長謝永達指出,看好未來在 AI 世代,異質封裝將采用更多 FOPLP 解決方案,預計 2026~2027 年會導入量產。

封測龍頭日月光 FOPLP 產品將在明年第二季開始出貨,面板尺寸從 300×300mm 已經擴張至 600×600mm,目前高通與其洽談 PMIC(電源管理IC)產品。此外,AMD 也與日月光、力成洽談 PC CPU 產品。

面板大廠群創近年積極轉型,自 2017 年便投入研發,目前試量產線月產能約 1,000 片,今年下半年可望量產。目前首期產能已被訂光,并開始啟動第二期擴產計劃,主要客戶為恩智浦、意法半導體等國際 IDM 大廠,未來將視客戶需求將月產能逐步提升至 15,000 片,以 PMIC 產品為主。

盤點臺灣地區 FOPLP 相關供應鏈,有濕制程領域弘塑、濺鍍/水平式電漿蝕刻設備廠友威科、雷射修補設備商東捷、載板干制程設備廠群翊、RDL制程設備亞智科技、電漿清洗及雷射打印廠商鈦升、自動化設備商萬潤、開發 FOPLP 特殊合金載板鑫科材料等。

CoWoS、FOPLP 后,下一個是 CoPoS 嗎?

隨著先進封裝轉換至 panel level(面板級),半導體設備商將提出另一個說法,即所謂的「CoPoS」(Chip-on-Panel-on-Substrate),即是 CoWoS「面板化」,以面板(Panel)取代晶圓(Wafer),將芯片排列在矩形基板上,最后再透過封裝制程連接到底層的載板上,讓多顆芯片可以封裝一起。

CoPoS 這項技術處于早期初期,初步判斷需要三五年才有機會到位,目前仍以 CoWoS、FOPLP 是較為明確的技術路線圖。

然而,FOPLP 受限于線寬及線距問題,目前應用仍以 PMIC 等成熟制程為主,待技術成熟后才會導入到主流消費性 IC 產品,TrendForce 預期時間約落在今年下半年至 2026 年;至于更高階的 AI GPU 應用,則是 2027-2028年有望落地,與臺積電董事長魏哲家預期至少三年后的量產時間相一致,他表示,目前尚未有成熟的解決方案,支持大于十倍光罩尺寸(Reticle size)芯片,預期三年后 FOPLP 將開始導入后,臺積電也將做好準備。

-

臺積電

+關注

關注

44文章

5686瀏覽量

167002 -

日月光

+關注

關注

0文章

146瀏覽量

19199 -

先進封裝

+關注

關注

2文章

427瀏覽量

286

發布評論請先 登錄

相關推薦

整合為王,先進封裝「面板化」!臺積電、日月光、群創搶攻FOPLP,如何重塑封裝新格局?

整合為王,先進封裝「面板化」!臺積電、日月光、群創搶攻FOPLP,如何重塑封裝新格局?

評論