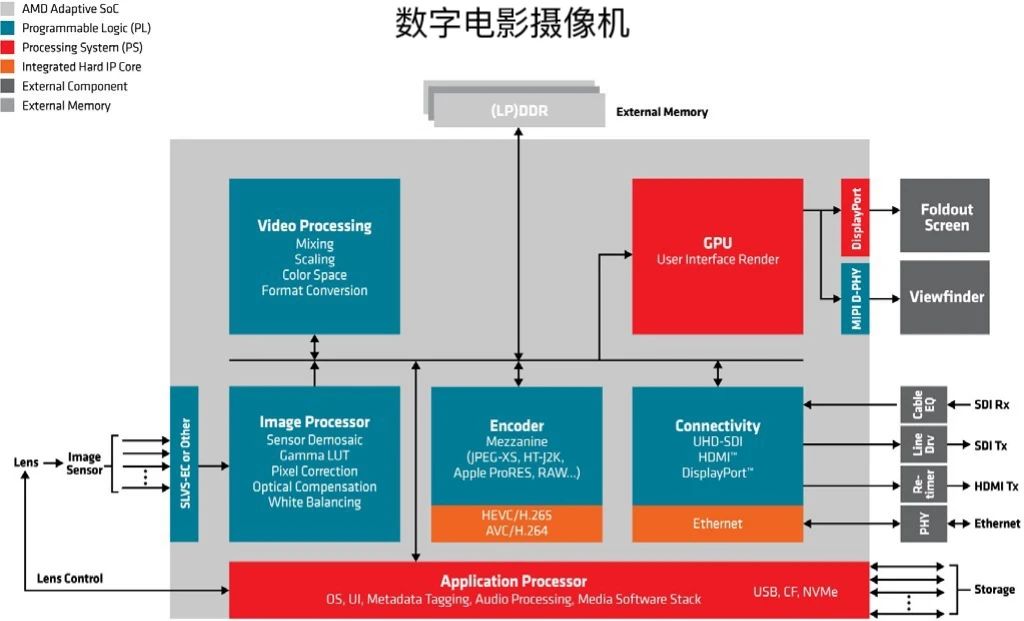

本文將從硬件設計和驅動使用兩個方面介紹基于 CPM5 QDMA 的 AMD Versal 自適應 SoC 的 Tandem 設計和啟動流程。

Versal QDMA 的兩個 PCIe 控制器都支持不同方式的 Tandem (Tandem PROM ? Tandem PCIe)。和其他系列的 Tandem 選項一樣,Tandem PROM 是 Tandem 配置的簡化模式,只是其中兩個階段都包含在同一個 pdi 里面,用戶可以把這個 pdi 文件存到 PROM 中,系統會先配置 CPM 然后再去配置其他部分這樣就能比較容易的滿足120ms 啟動時間的要求。

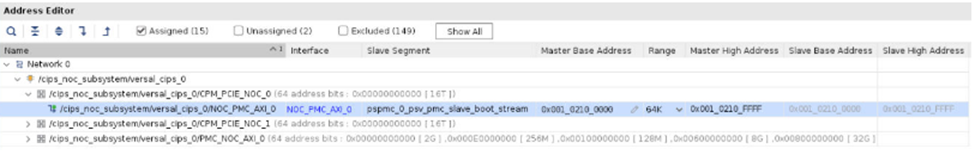

而 Tandem PCIe 則更為復雜,它第二部分的加載基于 PCIe 鏈路,在 BD 設計中必須包含從 CPM MASTER 到 PMC Slave 的路徑。而在 PMC 中需要使用特定的加載到的接口 Slave Boot Interface(SBI),其位于 AMD Versal設備地址 0x102100000。

Tandem PCIe 的軟硬件流程

首先在 CPM 生成界面選擇 DMA,把 Tandem mode 選擇為 Tandem PCIE。第二頁選擇 QDMA,其他都可以用默認選項。

CIPS 的 PCIE Reset 復位選擇和板上一致。

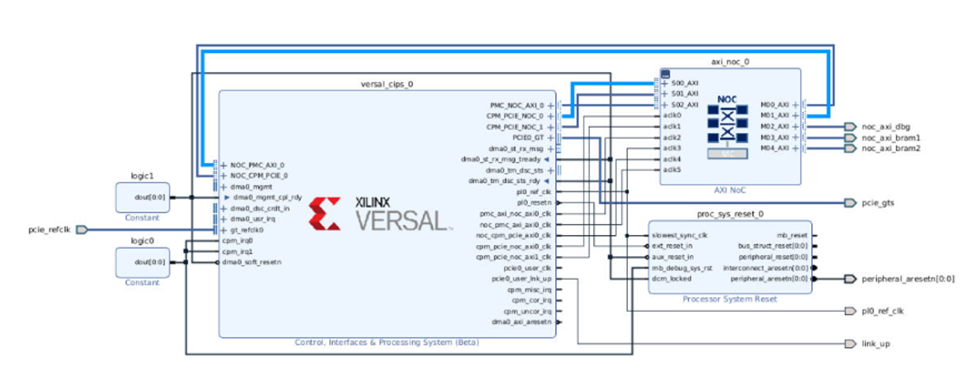

按照下圖連接 BD,需要連上復位 sys_reset ,連接 NOC, 并且把 CPM 的 Master 和 PMC 的 Slave 連上, 按照下圖把地址分配到 0x102100000 (slave boot stream), 這樣 QDMA 的傳輸目標地址就設置為從 0x102100000 開始。NOC 另一側可以連接 BRAM 和其他需要的用戶側 PL 邏輯。

由于工具并不會自動拉低 PL 的復位管腳所以用戶必須寫 XSDB (0xF1260330) 地址來拉低復位或者把 PL Reset 管腳從 CDO 中直接拉低并且重新生成 PDI。 如果 PL 的復位在 CIPS 外面,需要自己去控制這個復位保證加載完 pdi2 后 PL 可以工作。

生成 pdi 文件后,開始清除原來的驅動和加載新的驅動,以下為步驟。

首先可以通過 JTAG 或者 RPOM 的方式,把第一階段的pdi 文件下載進去 并且重啟主機。這個時候可以通過 lspci 看到 AMD Xilinx 的 bdf。然后準備好驅動和應用程序并運行以下程序。

獲取最新的驅動程序, 驅動可以從網站下載:

https://github.com/Xilinx/dma_ip_drivers/tree/master/QDMA

從內核中刪除舊模塊(僅在必要時)。 $> rmmod qdma-pf

編譯驅動程序和應用程序。 $> make -DTANDEM_BOOT_SUPPORTED

安裝(復制)驅動程序和應用程序到標準位置。$> make install

載入內核模塊。#> modprobe qdma-pf

產生 H2C 的隊列。 $> dma-ctl qdma10000 q add idx 0 dir h2c mode mm

啟動一個隊列, aperture size 是4k $> dma-ctl qdma10000 q start idx 0 dir h2c aperture_size 4096

傳輸 pdi2,這里的大小和名字需要按照實際情況修改:

$> dma-ctl qdma10000_MM_0-f design_wrapper.pdi -s 1384992 -a 0x102100000

卸載驅動沖 i 性能加載驅動重復2-5。

用 xsdb 去寫 o 0xF1260330,如果 pl_reset 連到了stag2 的邏輯上, 如果沒有這步可以省略。

完成其他測試 ,比如 BD design 后面連了 ddr 或者 bram,可以用 dma_to_device 來測試 PL 是否能正確接收數據。

-

amd

+關注

關注

25文章

5481瀏覽量

134346 -

控制器

+關注

關注

112文章

16412瀏覽量

178725 -

soc

+關注

關注

38文章

4184瀏覽量

218595 -

硬件

+關注

關注

11文章

3352瀏覽量

66331 -

PCIe

+關注

關注

15文章

1244瀏覽量

82862

原文標題:開發者分享|AMD Versal? 自適應 SoC CPM5 QDMA 的 Tandem PCIe 啟動流程介紹

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【ALINX 技術分享】AMD Versal AI Edge 自適應計算加速平臺之 Versal 介紹(2)

拓展AI數據中心內存,第二代AMD Versal Premium系列自適應SoC,首發支持CXL 3.1、 PCIe Gen6

Versal CPM AXI Bridge模式的地址轉換

AMD率先推出符合DisplayPort? 2.1 8K視頻標準的FPGA和自適應SoC

AMD發布第二代Versal自適應SoC,AI嵌入式領域再提速

AMD Versal? Adaptive SoC CPM PCIE PIO EP設計CED示例

第二代AMD Versal Prime系列自適應SoC的亮點

AMD推出第二代Versal Premium系列

AMD Versal自適應SoC GTM如何用XSIM仿真和觀察PAM4信號

AMD Versal自適應SoC DDRMC如何使用Micron仿真模型進行仿真

AMD Versal自適應SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

AMD Versal自適應SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

評論