時序邏輯電路本身并不直接“產生”鎖存器,但鎖存器是時序邏輯電路中的重要組成部分。時序邏輯電路(Sequential Logic Circuits)與組合邏輯電路(Combinational Logic Circuits)不同,它能夠在任何給定時刻的輸出不僅取決于當前的輸入,還取決于電路過去的輸入(即電路的當前狀態)。這種記憶功能使得時序邏輯電路能夠處理更復雜的問題,如存儲數據、進行狀態轉換等。

鎖存器(Latch)是時序邏輯電路中的一種基礎元件,用于存儲一位或多位二進制數據。鎖存器通過控制信號(如使能信號或時鐘信號)來鎖定或更新其存儲的數據。當控制信號有效時,鎖存器將輸入的數據存儲在內部,并在控制信號無效時保持該數據不變。這種特性使得鎖存器成為實現時序邏輯電路的關鍵元素之一。

常見的鎖存器類型包括RS鎖存器、D鎖存器等。這些鎖存器通過不同的控制邏輯和反饋機制來實現數據的存儲和更新。例如,RS鎖存器具有兩個控制輸入端S和R,分別用于置位(Set)和復位(Reset)操作;D鎖存器則具有一個數據輸入端D和一個控制輸入端(通常是時鐘信號或使能信號),用于在控制信號有效時將D端的數據鎖存到輸出端。

時序邏輯與鎖存器概述

1. 數字邏輯基礎

數字邏輯是電子工程和計算機科學中的一個基礎領域,它涉及到使用二進制數字信號來表示和處理信息。數字邏輯的核心是邏輯門,包括與門(AND)、或門(OR)、非門(NOT)、異或門(XOR)等,這些邏輯門可以組合成更復雜的邏輯電路。

2. 時序邏輯的定義

時序邏輯是一種特殊的數字邏輯,它使用時鐘信號來同步電路的操作。在時序邏輯中,數據的傳輸和處理是按照時鐘信號的周期性變化進行的。這種同步機制可以減少電路中的競爭條件和冒險,提高電路的穩定性和可靠性。

3. 鎖存器的概念

鎖存器是一種存儲一位二進制信息的電路,它可以在沒有時鐘信號的情況下保持其輸出狀態。鎖存器通常由一個或多個觸發器(Flip-Flops)組成,這些觸發器可以在特定條件下改變其狀態。

鎖存器的類型和工作原理

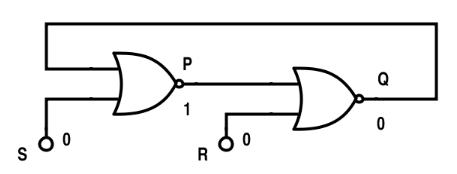

1. SR鎖存器(Set-Reset Latch)

SR鎖存器是最基本的鎖存器類型,它有兩個輸入端:置位(Set)和復位(Reset)。當置位端被激活時,鎖存器的輸出將被設置為高電平;當復位端被激活時,輸出將被設置為低電平。

2. D鎖存器(Data Latch)

D鎖存器是一種單數據輸入的鎖存器,其輸出直接反映輸入端的數據狀態。D鎖存器通常用于數據的暫存和傳輸。

3. JK鎖存器(Jack-Kill Latch)

JK鎖存器是一種具有兩個輸入端的鎖存器,分別標記為J和K。JK鎖存器可以執行置位、復位、保持和翻轉操作,這使得它在時序邏輯設計中非常靈活。

時序邏輯中的鎖存器應用

1. 數據暫存

在數字電路中,鎖存器常用于暫存數據,以便在適當的時刻將數據傳輸到下一個邏輯階段。這種暫存機制可以減少電路中的數據沖突和延遲。

2. 信號同步

在復雜的數字系統中,不同的邏輯模塊可能以不同的速率運行。使用鎖存器可以實現信號的同步,確保數據在正確的時刻被處理。

3. 狀態機設計

狀態機是時序邏輯設計中的一個重要組成部分,它可以控制電路的狀態轉換。鎖存器在狀態機設計中用于存儲當前狀態,以便在下一個時鐘周期進行狀態轉換。

鎖存器與觸發器的區別

1. 觸發器的定義

觸發器是一種具有時鐘輸入的存儲元件,它可以在時鐘信號的控制下改變其狀態。觸發器通常由兩個鎖存器級聯而成,具有更嚴格的時序特性。

2. 鎖存器與觸發器的比較

- 鎖存器沒有時鐘控制,而觸發器有。

- 觸發器具有更嚴格的時序特性,可以減少亞穩態的風險。

- 在某些應用中,觸發器可以替代鎖存器,但反之則不一定。

時序邏輯設計中的挑戰

1. 時鐘偏斜和時鐘抖動

時鐘信號在傳輸過程中可能會受到干擾,導致時鐘偏斜或抖動。這些問題會影響時序邏輯的正確性。

2. 亞穩態問題

在某些條件下,鎖存器或觸發器可能進入亞穩態,即輸出在一段時間內不確定。這可能會導致電路的不穩定和錯誤。

3. 競爭條件和冒險

在復雜的時序邏輯設計中,不同的信號路徑可能會導致競爭條件和冒險,從而影響電路的性能和可靠性。

-

二進制

+關注

關注

2文章

796瀏覽量

41757 -

鎖存器

+關注

關注

8文章

908瀏覽量

41645 -

時序邏輯

+關注

關注

0文章

39瀏覽量

9194 -

存儲數據

+關注

關注

0文章

89瀏覽量

14154

發布評論請先 登錄

相關推薦

時序邏輯會產生鎖存器嗎

時序邏輯會產生鎖存器嗎

評論