雙穩態觸發器(Bistable Trigger)是一種具有兩個穩定狀態的電子電路,廣泛應用于數字電路設計中。

- 雙穩態觸發器的工作原理

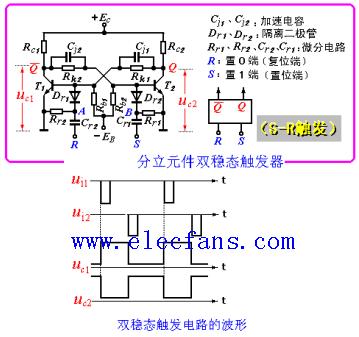

雙穩態觸發器是一種具有兩個穩定狀態的電路,即“0”狀態和“1”狀態。在沒有外部觸發信號的情況下,雙穩態觸發器可以保持在任意一個穩定狀態。當接收到外部觸發信號時,雙穩態觸發器會從一個穩定狀態切換到另一個穩定狀態。

雙穩態觸發器的工作原理基于正反饋機制。在電路中,輸出信號會通過正反饋回路反饋到輸入端,使得電路在接收到觸發信號后能夠迅速切換狀態。這種正反饋機制使得雙穩態觸發器具有很高的穩定性和抗干擾能力。

- 雙穩態觸發器的電路設計

雙穩態觸發器的電路設計有很多種,其中最常用的是RS觸發器和D觸發器。下面分別介紹這兩種觸發器的電路設計。

2.1 RS觸發器

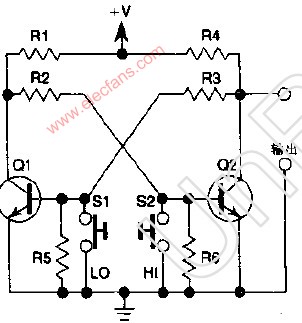

RS觸發器是一種基本的雙穩態觸發器,由兩個與非門(NAND)或兩個或非門(NOR)構成。RS觸發器的電路設計如下:

- 輸入端:RS觸發器有兩個輸入端,分別標記為R(Reset)和S(Set)。

- 輸出端:RS觸發器有兩個輸出端,分別標記為Q和Q'(Q的反相)。

- 正反饋回路:Q和Q'通過正反饋回路連接到輸入端。

RS觸發器的工作原理如下:

- 當R=0,S=1時,Q=1,Q'=0,觸發器處于“1”狀態。

- 當R=1,S=0時,Q=0,Q'=1,觸發器處于“0”狀態。

- 當R=0,S=0或R=1,S=1時,觸發器保持當前狀態不變。

2.2 D觸發器

D觸發器是一種具有數據輸入端的雙穩態觸發器,常用于數據存儲和傳輸。D觸發器的電路設計如下:

- 數據輸入端:D觸發器有一個數據輸入端,標記為D。

- 時鐘輸入端:D觸發器有一個時鐘輸入端,標記為CLK。

- 輸出端:D觸發器有兩個輸出端,分別標記為Q和Q'(Q的反相)。

D觸發器的工作原理如下:

- 當CLK信號上升沿到來時,D觸發器將D端的數據存儲到Q端,同時Q'端輸出Q的反相數據。

- 當CLK信號下降沿到來時,D觸發器保持當前狀態不變。

- 雙穩態觸發器的應用場景

雙穩態觸發器在數字電路設計中有廣泛的應用,主要包括以下幾個方面:

3.1 數據存儲

雙穩態觸發器可以用于存儲數字信號,實現數據的保持和傳輸。在計算機、通信設備等數字系統中,雙穩態觸發器被廣泛應用于寄存器、計數器、移位寄存器等數據存儲部件。

3.2 信號同步

在數字系統中,信號同步是一個重要的問題。雙穩態觸發器可以用于實現信號的同步,消除時鐘抖動和亞穩態現象。例如,在觸發器的輸出端添加一個緩沖器,可以實現信號的同步輸出。

3.3 脈沖整形

雙穩態觸發器可以用于脈沖整形,將不規則的脈沖信號轉換為規則的方波信號。在數字系統中,脈沖整形可以提高信號的穩定性和可靠性。

3.4 邏輯控制

雙穩態觸發器可以用于實現邏輯控制功能,如計數器、分頻器、序列發生器等。通過合理設計觸發器的輸入條件和反饋回路,可以實現復雜的邏輯控制功能。

- 雙穩態觸發器的實際應用注意事項

在實際應用中,需要注意以下幾個方面的問題:

4.1 抗干擾能力

雙穩態觸發器的抗干擾能力與其電路設計和工作環境有關。在設計時,應盡量選擇具有高抗干擾能力的觸發器,并在電路中添加適當的濾波和保護措施。

4.2 功耗問題

雙穩態觸發器的功耗與其工作頻率、電路復雜度等因素有關。在設計時,應盡量選擇低功耗的觸發器,并優化電路設計,降低功耗。

4.3 時鐘抖動和亞穩態

在雙穩態觸發器的應用中,時鐘抖動和亞穩態現象可能導致數據錯誤和系統不穩定。為避免這些問題,應選擇合適的時鐘源,并在電路中添加適當的同步和去抖動措施。

-

數字電路

+關注

關注

193文章

1629瀏覽量

80822 -

電子電路

+關注

關注

78文章

1227瀏覽量

67034 -

輸出信號

+關注

關注

0文章

291瀏覽量

11936

發布評論請先 登錄

相關推薦

雙穩態觸發器的實際應用注意事項

雙穩態觸發器的實際應用注意事項

評論