前言

我們聊聊芯片設(shè)計(jì)、流片、驗(yàn)證、制造、成本的那些事;流片對(duì)于芯片設(shè)計(jì)來說就是參加一次大考。

流片的重要性就在于能夠檢驗(yàn)芯片設(shè)計(jì)是否成功,是芯片制造的關(guān)鍵環(huán)節(jié),也就是將設(shè)計(jì)好的方案交給芯片制造廠生產(chǎn)出樣品。檢測(cè)設(shè)計(jì)的芯片是否達(dá)到設(shè)計(jì)要求,或者是否需要進(jìn)一步優(yōu)化;如果能夠生產(chǎn)出符合要求的芯片,那么就可以大規(guī)模生產(chǎn)了。

上圖流程的輸入是芯片立項(xiàng)設(shè)計(jì),輸出是做好的芯片晶圓。

一、晶圓術(shù)語

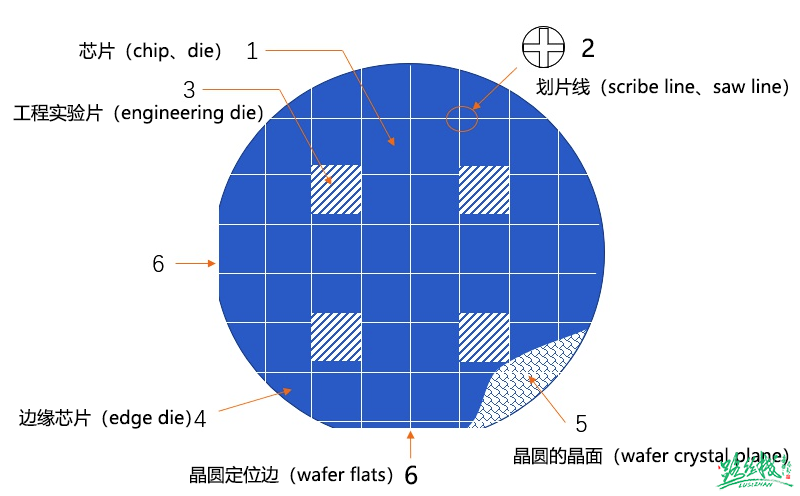

1. 芯片(chip、die)、器件(device)、電路(circuit)、微芯片(microchip)或條碼(bar):所有這些名詞指的是在晶圓表面占大部分面積的微芯片圖形;

2. 劃片線(scribe line、saw line)或街區(qū)(street、avenue):這些區(qū)域是在晶圓上用來分隔不同芯片之間的間隔區(qū)。劃片線通常是空白的,但有些公司在間隔區(qū)內(nèi)放置對(duì)準(zhǔn)標(biāo)記,或測(cè)試的結(jié)構(gòu);

3. 工程實(shí)驗(yàn)片(engineering die)和測(cè)試芯片(test die):這些芯片與正式芯片或電路芯片不同。它包括特殊的器件和電路模塊用于晶圓生產(chǎn)工藝的電性測(cè)試;

4. 邊緣芯片(edge die):在晶圓邊上的一些掩膜殘缺不全的芯片而產(chǎn)生的面積損耗。由于單個(gè)芯片尺寸增大而造成的更多邊緣浪費(fèi)會(huì)由采用更大直徑晶圓所彌補(bǔ)。推動(dòng)半導(dǎo)體工業(yè)向更大直徑晶圓發(fā)展的動(dòng)力之一就是為了減少邊緣芯片所占的面積;

5. 晶圓的晶面(wafer crystal plane):圖中的剖面標(biāo)示了器件下面的晶格構(gòu)造,此圖中顯示的器件邊緣與晶格構(gòu)造的方向是確定的;

6. 晶圓定位邊(wafer flats)/凹槽(notche):圖示的晶圓由注定位邊(major flat)和副定位邊(minor flat),表示這是一個(gè)P型<100>晶向的晶圓。300mm和450mm直徑的晶圓都是用凹槽作為晶格導(dǎo)向的標(biāo)識(shí)。這些定位邊和凹槽在一些晶圓生產(chǎn)工藝中還輔助晶圓的套準(zhǔn)。

二、芯片的流片方式(Full Mask、MPW)

Full Mask和MPW都是集成電路的一種流片(將設(shè)計(jì)結(jié)果交出去進(jìn)行生產(chǎn)制造)方式。Full Mask是“全掩膜”的意思,即制造流程中的全部掩膜都為某個(gè)設(shè)計(jì)服務(wù);而MPW 全稱為Multi Project Wafer,直譯為多項(xiàng)目晶圓,即多個(gè)項(xiàng)目共享某個(gè)晶圓,也即同一次制造流程可以承擔(dān)多個(gè)IC設(shè)計(jì)的制造任務(wù)。

1.Full Mask,“全掩膜”,即制造流程中的全部掩膜都為某個(gè)設(shè)計(jì)服務(wù);Full Mask的芯片,一片晶圓可以產(chǎn)出上千片DIE;然后封裝成芯片,可以支撐大批量的客戶需求。

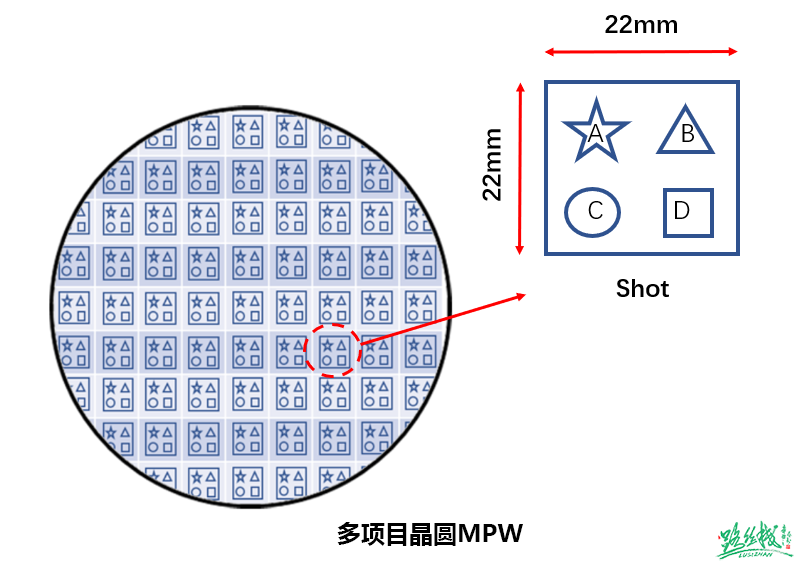

2.MPW全名叫Multi Project Wafer,和電路設(shè)計(jì)PCB的拼板打樣類似,叫多項(xiàng)目晶圓。多項(xiàng)目晶圓就是將多個(gè)使用相同工藝的集成電路設(shè)計(jì)放在同一晶圓片上流片,制造完成后,每個(gè)設(shè)計(jì)可以得到數(shù)十片芯片樣品,這一數(shù)量對(duì)于原型(Prototype)設(shè)計(jì)階段的實(shí)驗(yàn)、測(cè)試已經(jīng)足夠。這種操作方式可以讓流片費(fèi)下降90%-95%,也就大幅降低了芯片研發(fā)的成本。

晶圓廠每年都會(huì)有固定的幾次MPW機(jī)會(huì),叫Shuttle (班車),到點(diǎn)即發(fā)車,是不是非常形象不同公司拼Wafer,得有個(gè)規(guī)則,MPW按SEAT來鎖定面積,一個(gè)SEAT一般是3mm*4mm的一塊區(qū)域,一般晶圓廠為了保障不同芯片公司均能參與MPW,對(duì)每家公司預(yù)定的SEAT數(shù)目會(huì)限制(其實(shí)SEAT多成本就上去了,MPW意義也沒有了)。MPW優(yōu)勢(shì)投片成本小,一般就小幾十萬,可以很好降低風(fēng)險(xiǎn);需要注意的是MPW從生產(chǎn)角度是一次完整的生產(chǎn)流程,因此其還是一樣耗時(shí)間,一次MPW一般需要6~9個(gè)月,會(huì)帶來芯片的交付時(shí)間后延。

因?yàn)槭瞧碬afer,因此通過MPW拿到的芯片數(shù)目就會(huì)很有限,主要用于芯片公司內(nèi)部做驗(yàn)證測(cè)試,也可能會(huì)提供給極少數(shù)的頭部客戶。從這里大家可能已經(jīng)了解了,MPW是一個(gè)不完整的,不可量產(chǎn)的投片。

3.晶圓生產(chǎn)角度介紹MPW

畢竟芯片加工還是一個(gè)相對(duì)復(fù)雜的過程,我相信很多朋友看完第一和小二之前理解的晶圓結(jié)構(gòu),是下圖的,一個(gè)框歸屬于一個(gè)芯片公司。

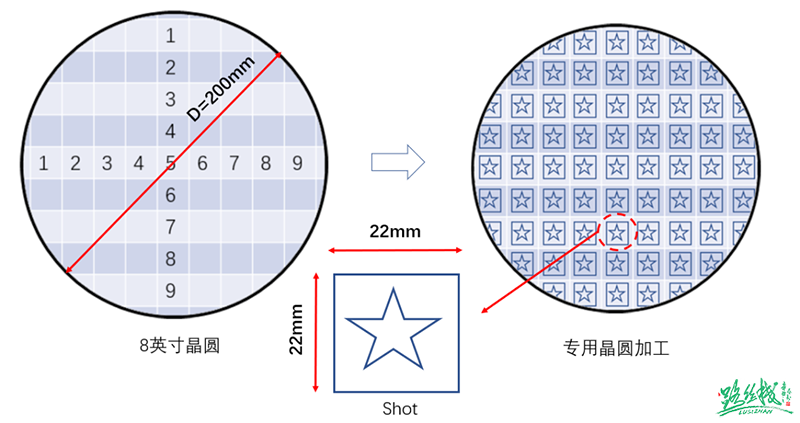

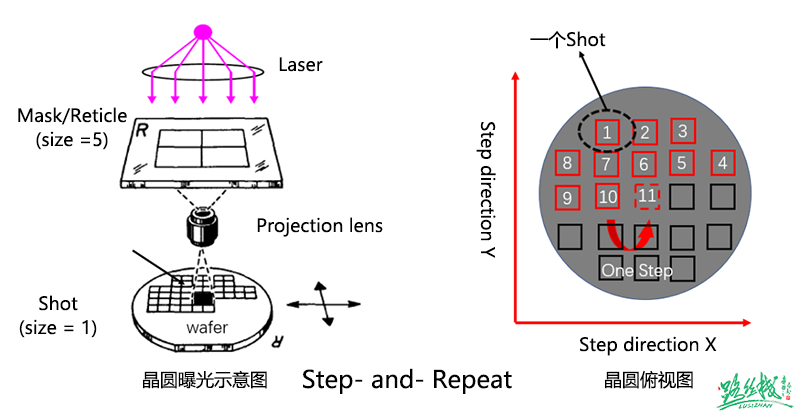

實(shí)則不然,這就需要和晶圓的生產(chǎn)流程的光刻技術(shù)相關(guān)了;現(xiàn)階段的光刻技術(shù)DUV/EUV等,大多采用縮影的方式進(jìn)行曝光,如下圖所示:

采用1:5 放大的mask,對(duì)晶圓進(jìn)行曝光,一次曝光的矩形區(qū)域通常稱為一個(gè)shot,完成曝光后,自動(dòng)調(diào)整晶圓位置,對(duì)下個(gè)shot進(jìn)行曝光,如此循環(huán)(Step-and-Repeat),直到整個(gè)晶圓完成曝光,而這一個(gè)Shot的區(qū)域,則是大家一起分擔(dān)SEAT的區(qū)域;

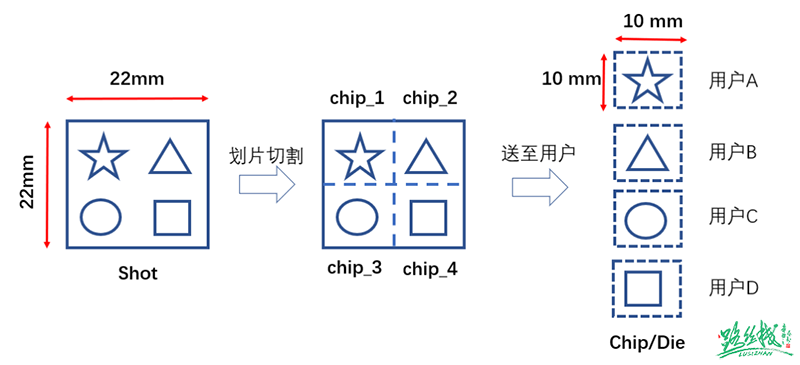

如下示意圖中,一個(gè)Shot里面劃分4個(gè)小格,每個(gè)格子給到一家廠商的設(shè)計(jì),MPW晶圓一般20個(gè)以內(nèi)用戶。

三、芯片ECO流程

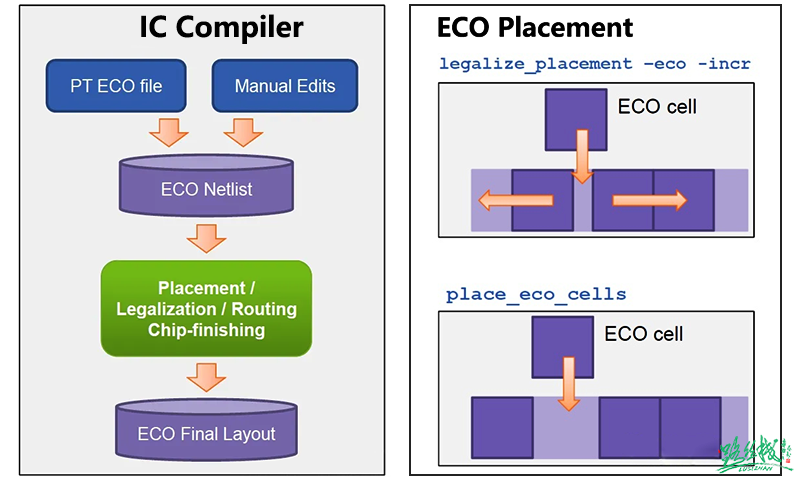

ECO 指的是Engineering Change Order,即工程變更指令。ECO可以發(fā)生在Tapeout之前,過程中,或者之后;Tapeout之后的ECO,改動(dòng)少的可能僅需要改幾層Metal layer,改動(dòng)大可能需要?jiǎng)邮畮讓覯etal layer,甚至重新流片。ECO 的實(shí)現(xiàn)流程如下圖所示:

如果MPW或者FullMask的芯片,驗(yàn)證有功能或者性能缺陷,通過ECO對(duì)電路和標(biāo)準(zhǔn)單元布局進(jìn)行小范圍調(diào)整,保持原設(shè)計(jì)布局布線結(jié)果基本不變的前提下做小規(guī)模優(yōu)化,修復(fù)芯片的剩余違例,最終達(dá)到芯片的簽核標(biāo)準(zhǔn)。不能通過后端布局布線的流程來修復(fù)違例(重新走一遍流程太費(fèi)時(shí)了),而要通過ECO的流程來進(jìn)行時(shí)序、DRC、 DRV以及功耗等優(yōu)化。

四、流片Corner

1.Corner是芯片制造是一個(gè)物理過程,存在著工藝偏差(包括摻雜濃度、擴(kuò)散深度、刻蝕程度等),導(dǎo)致不同批次之間,同一批次不同晶圓之間,同一晶圓不同芯片之間情況都是不相同的。

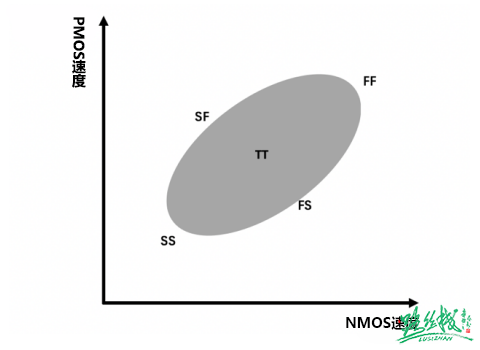

在一片wafer上,不可能每點(diǎn)的載流子平均漂移速度都是一樣的,隨著電壓、溫度不同,它們的特性也會(huì)不同,把他們分類就有了PVT(Process,Voltage,Temperature),而Process又分為不同的corner:TT:Typical N Typical P FF:Fast N Fast P SS:Slow N Slow P FS:Fast N Slow P SF:Slow N Fast P 第一個(gè)字母代表NMOS,第二個(gè)字母代表PMOS,都是針對(duì)不同濃度的N型和P型摻雜來說的。NMOS和PMOS在工藝上是獨(dú)立做出來的,彼此之間不會(huì)影響,但是對(duì)于電路,NMOS和PMOS是同時(shí)工作的,會(huì)出現(xiàn)NMOS快的同時(shí)PMOS也快,或者慢,所以會(huì)出現(xiàn)FF、SS、FS、SF四種情況。通過Process注入的調(diào)整,模擬器件速度快慢,同時(shí)根據(jù)偏差大小設(shè)定不同等級(jí)的FF和SS。正常情況下大部分是TT,而以上5種corner在+/-3sigma可以覆蓋約99.73%的范圍,這種隨機(jī)性的發(fā)生符合正態(tài)分布。

2.Corner wafer的意義在工程片流片的時(shí)候,F(xiàn)AB會(huì)pirun關(guān)鍵層次調(diào)整inline variation,有的還會(huì)下backup wafer以保證出貨的wafer器件on target,即在TT corner附近。如果單純是為了做一些樣品出來,只進(jìn)行工程片流片,那可以不驗(yàn)證corner,但如果為了后續(xù)量產(chǎn)準(zhǔn)備,是必須要考慮corner的。由于工藝在制作過程中會(huì)有偏差,而corner是對(duì)產(chǎn)線正常波動(dòng)的預(yù)估,F(xiàn)AB也會(huì)對(duì)量產(chǎn)芯片的corner驗(yàn)證有所要求。所以在設(shè)計(jì)階段就要滿足corner,在各種corner和極限溫度條件下對(duì)電路進(jìn)行仿真,使其在各種corner上都能正常工作,才能使最終生產(chǎn)出的芯片良率高。

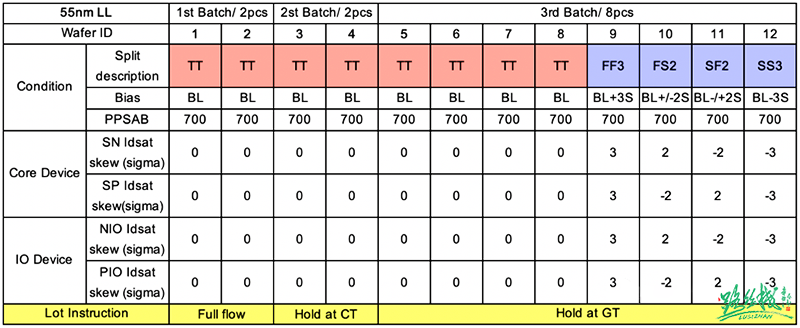

3.Corner Split Table策略 對(duì)于產(chǎn)品來講,一般corner做到spec上,正常情況下spec有6個(gè)sigma,如FF2(或2FF)表示往快的方向偏2個(gè)Sigma,SS3(或3SS)表示往慢的方向偏3個(gè)Sigma。Sigma主要表征了Vt的波動(dòng),波動(dòng)大sigma就大,這里3個(gè)sigma就是在工藝器件的spec線上,可以允許超出一點(diǎn)點(diǎn),因?yàn)榫€上波動(dòng)不可能正正好好做到spec上。

如下是55nm Logic工藝片的例,擬定的corner split table:

①#1 & #2 兩片pilot wafer,一片盲封,一片測(cè)CP;

②#3 & #4 兩片hold在Contact,為后道改版預(yù)留工程wafer,可以節(jié)省ECO流片時(shí)間 ;

③#5~#12 八片hold在Poly,等pilot的結(jié)果看是否需要調(diào)整器件速度,并驗(yàn)證corner;

④除了留有足夠的芯片用于測(cè)試驗(yàn)證,Metal Fix,還應(yīng)根據(jù)項(xiàng)目需求,預(yù)留盡可能多的wafer作為量產(chǎn)出貨。

4.確認(rèn)Corner結(jié)果

首先,大部分都應(yīng)該落于四個(gè)corner決定的window范圍內(nèi),如果出現(xiàn)大的偏差,那可能是工藝shift。如果各個(gè)corner的良率都沒影響符合預(yù)期,那說明工藝窗口充分。如果有個(gè)別條件良率低,那就需要調(diào)整工藝窗口。Corner wafer的目的是驗(yàn)證設(shè)計(jì)余量,考察良率是否有損失。大體上,超出這個(gè)corner約束性能范圍內(nèi)的芯片報(bào)廢。

Corner驗(yàn)證對(duì)標(biāo)的是WAT測(cè)試結(jié)果,一般由FAB主導(dǎo),但是corner wafer的費(fèi)用是由設(shè)計(jì)公司承擔(dān)的。一般成熟穩(wěn)定的工藝,同一片wafer上的芯片,同一批次的wafer甚至不同批次的wafer參數(shù)都是很接近的,偏差的范圍相對(duì)不會(huì)很大。工藝角(Process Corner)PVT(Precess Voltage Temperature)工藝誤差與雙極晶體管不同,在不同的晶片之間以及在不同的批次之間,MOSFETs參數(shù)變化很大。

為了在一定程度上減輕電路設(shè)計(jì)任務(wù)的困難,工藝工程師們要保證器件的性能在某個(gè)范圍內(nèi),大體上,他們以報(bào)廢超出這個(gè)性能范圍的芯片的措施來嚴(yán)格控制預(yù)期的參數(shù)變化。

①M(fèi)OS管的快慢分別指閾值電壓的高低,快速對(duì)應(yīng)閾值低,慢速對(duì)應(yīng)閾值高。GBW=GM/CC ,其它條件相同情況下,vth越低,gm值越高,因此GBW越大,速度越快。(具體情況具體分析)

②電阻的快慢。fast對(duì)應(yīng)的是方塊電阻小,slow對(duì)應(yīng)的是方塊電阻大。

③電容的快慢。fast對(duì)應(yīng)的是電容最小,slow對(duì)應(yīng)的是容值最大。

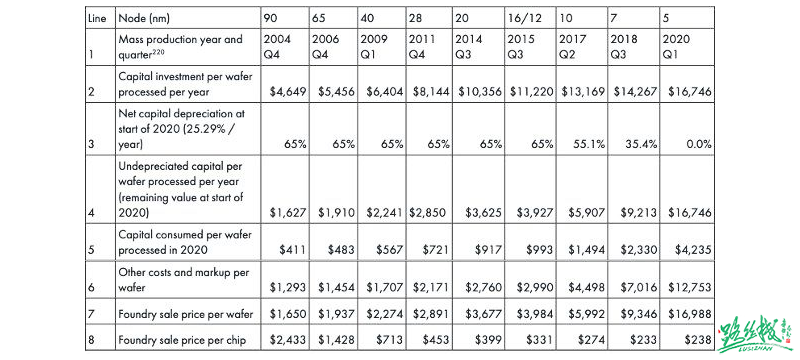

五、流片成本和晶圓價(jià)格

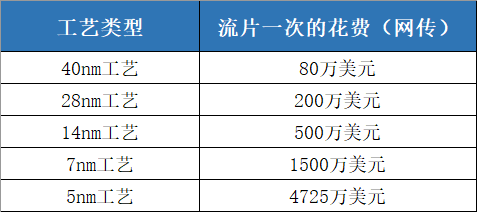

40nm的流片Mask成本大概在80-90萬美元,晶圓成本每片在3000-4000美元左右,加上IP merge,七八百萬人民幣跑不掉了。

28nm工藝流片一次需要200萬美元;14nm工藝流片一次需要500萬美元;7nm工藝流片一次需要1500萬美元;5nm工藝流片一次4725萬美元;3nm工藝流片可能要上億美元;掩膜版、晶圓這兩項(xiàng)主要流片成本中,掩膜版最貴。

越先進(jìn)的工藝節(jié)點(diǎn),所需要的掩膜版層數(shù)就越多;因?yàn)槊恳粚印把谀ぐ濉睂?duì)應(yīng)涂抹一次光刻膠、曝光、顯影、刻蝕等操作,涉及材料成本、儀器折舊成本,這些成本都需要fabless客戶買單!

28nm大概需要40層,14nm工藝需要60張掩膜版;7nm工藝需要80張甚至上百?gòu)堁谀ぐ妫灰粚覯ask 8萬美金,因此芯片必須量產(chǎn),拉低成本!

40nm MCU工藝為例:如果生產(chǎn)10片晶圓,每片晶圓成本(90萬+ 4000*10)/10=9.4萬美元;生產(chǎn)10000片晶圓,每片晶圓成本(90萬+4000*10000)/10000=4090美元。(晶圓量越大越便宜,不同產(chǎn)家報(bào)價(jià)也不一樣。)

晶圓代工價(jià)格來源于網(wǎng)絡(luò)

臺(tái)積電今年給的最新報(bào)價(jià):最先進(jìn)的制程3nm,每片晶圓19865美元,折合人民幣大概14.2w左右。

結(jié)語

芯片從設(shè)計(jì)到成品有幾個(gè)重要環(huán)節(jié),分別是設(shè)計(jì)->流片->封裝->測(cè)試,但芯片成本構(gòu)成的比例確大不相同,一般為人力成本20%,流片40%,封裝35%,測(cè)試5%。

芯片流片是高風(fēng)險(xiǎn)的事情,這個(gè)風(fēng)險(xiǎn)有多高,這個(gè)概率在15%-35%左右;不同的團(tuán)隊(duì)和芯片種類概率也不一樣。有模擬芯片公司即使在團(tuán)隊(duì)完備、思路清晰的情況下,還是耗了8年時(shí)間,歷經(jīng)18次流片,才最終完成了傳感器模擬計(jì)算IP驗(yàn)證,打造出了理想中的那顆超低功耗、超近傳感芯片。

-

晶圓

+關(guān)注

關(guān)注

52文章

4973瀏覽量

128313 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1028瀏覽量

55005 -

芯片驗(yàn)證

+關(guān)注

關(guān)注

5文章

34瀏覽量

47274 -

流片

+關(guān)注

關(guān)注

0文章

28瀏覽量

9794

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

流片的時(shí)間與金錢成本

片上網(wǎng)絡(luò)核心芯片的驗(yàn)證

原型驗(yàn)證即服務(wù)助力芯片設(shè)計(jì)

講講芯片的流片制造那些事兒

是德科技使用數(shù)字孿生信令實(shí)現(xiàn)先進(jìn)的半導(dǎo)體流片原型設(shè)計(jì)

國(guó)芯科技:正在流片驗(yàn)證chiplet芯片高性能互聯(lián)IP技術(shù)

聊聊芯片設(shè)計(jì)、流片、驗(yàn)證、制造、成本的那些事

聊聊芯片設(shè)計(jì)、流片那些事

芯片設(shè)計(jì)流片、驗(yàn)證、成本的那些事

芯片設(shè)計(jì)流片、驗(yàn)證、成本的那些事

評(píng)論