基本概念

建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

電路中的建立時間和保持時間其實跟生活中的紅綠燈很像,建立時間是指在綠燈(clk的上升沿)亮起之前行人或者車輛(data數據)在路口提前等待的時間(只允許綠燈亮起的一剎那在路口的車輛才允許通行),而保持時間,則是綠燈亮起后必須保持的時間,這樣行人或者數據才能夠通過這個十字路口,否則hold時間就不滿足。

同時,紅綠燈默認都是周期性的(clk也是周期性的),車輛不允許在兩個相鄰的紅綠燈之間通過的時間超過一個clk的周期(組合邏輯時延不能過大)。

建立時間(Tsu) :是指在時鐘沿到來之前數據從不穩定到穩定所需的時間,如果建立的時間不滿足要求,在時鐘上升沿,寄存器將不能正確采到數據值。如下圖(左)所示:

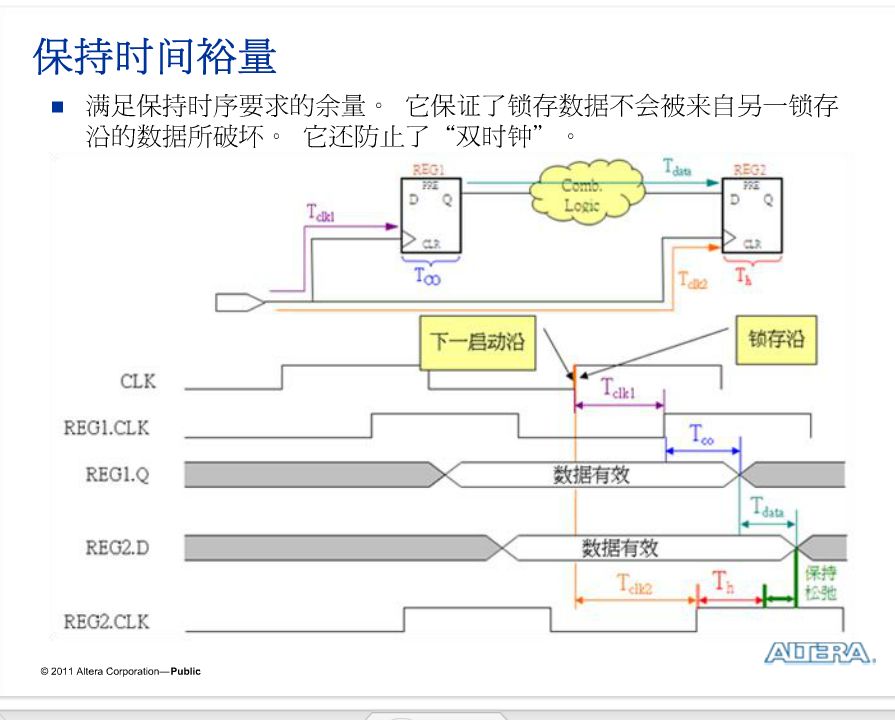

保持時間(Th) :是指在時鐘上升沿后數據保持穩定的時間,如果保持時間不滿足要求那么數據同樣也不能被正確采集到。保持時間示意圖如下圖(右)所示:

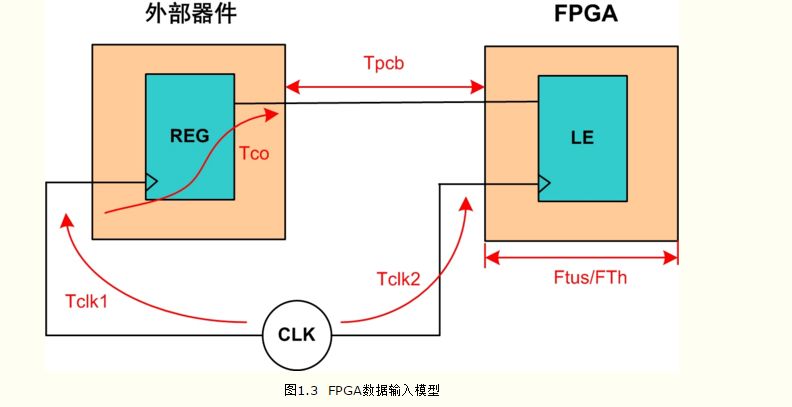

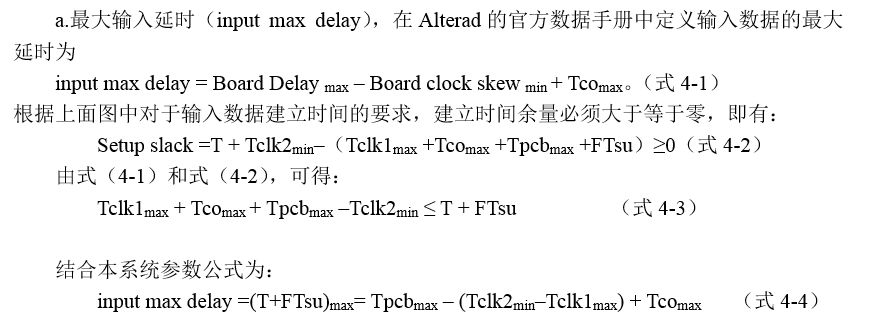

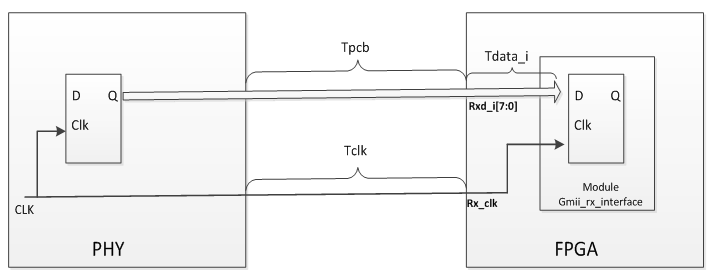

如圖1.3,這是一個FPGA輸入數據的模型,輸入端口到第一個寄存器之間的路徑需要進行時序約束。

一般我們需要告知FPGA輸入輸出接口的最大最小延遲,使EDA工具在進行布局布線時能夠盡可能的優化輸入端口到第一級寄存器之間的延遲,使FPGA中時鐘的上升沿能夠正確采集到輸入的數據。

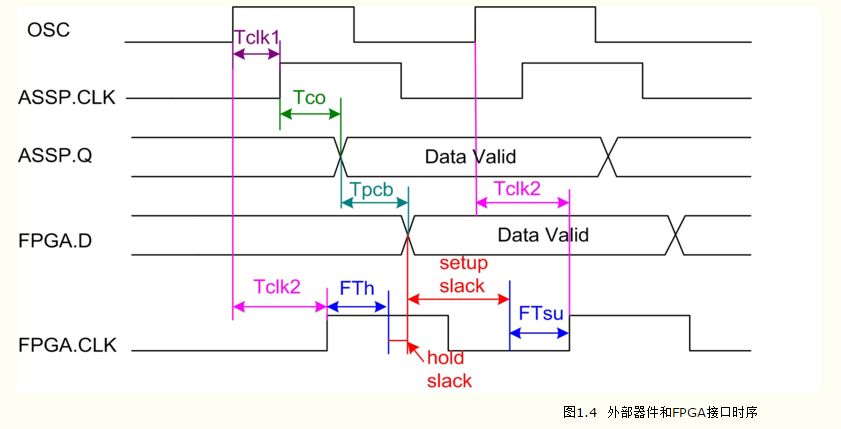

在sdc約束中,輸入延時是從上游器件發出數據到FPGA輸入端口的延時時間。如圖,1.4所示,輸入接口時序清楚反應了FPGA在接收數據時應滿足的建立和保持時間要求。

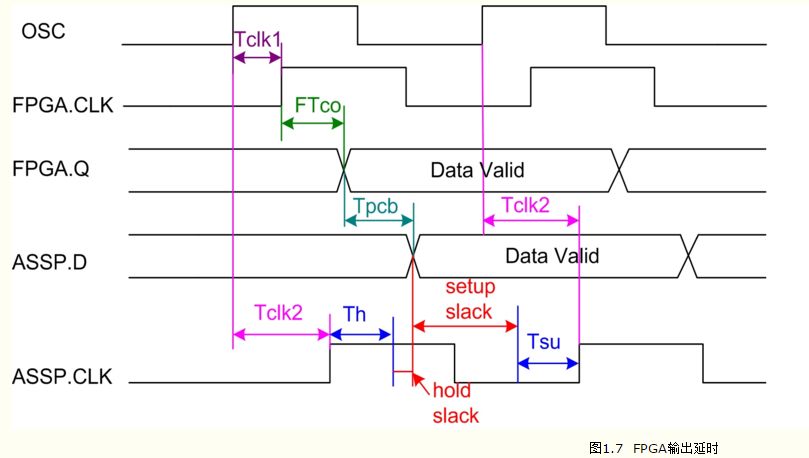

說明:

OSC :系統時鐘

ASSP.CLk :外部器件寄存器的時鐘

ASSP.Q :外部器件數據輸出

FPGA.D :FPGA數據輸入

FPGA.CLK :FPGA內部寄存器的時鐘

Tclk1 :系統時鐘到外部器件之間的延時

Tclk2 :系統時鐘到FPGA之間的延時

Tco :數據經過外部器件寄存器輸出后相對于ASSP.CLK的偏移

Tpcb :數據在pcb電路板上的延時

FTsu :FPGA上寄存器的建立時間要求

FTh :FPGA上寄存器的保持時間要求

setup slack :建立時間余量,必須大于等于0才能滿足建立時間的時序要求

hold slack :保持時間余量,必須大于等于0才能滿足保持時間的時序要求

T: 系統時鐘頻率

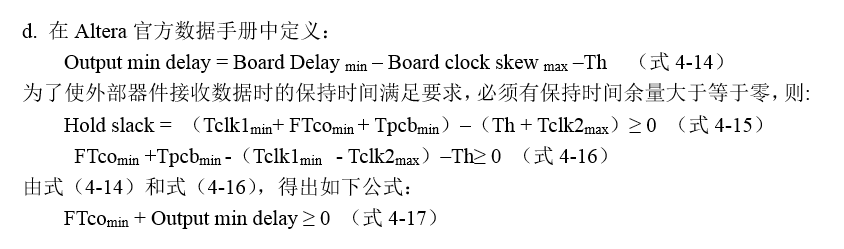

c. 輸出延時即為FPGA輸出數據后到達外部器件的延時時間。如1.7所示,為FPGA和外部器件接口時序圖。

系統同步和源同步接口

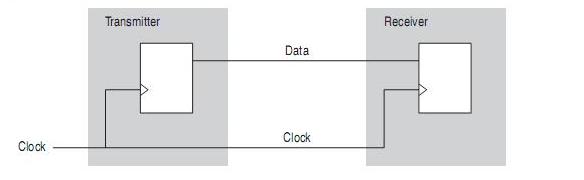

系統同步中數據發送器和數據接收器在同一時鐘源下同步工作,發送器和接收器之間只傳遞數據,數據的時序關系以系統時鐘作為參考。

所謂源同步接口是指發送器和接收器之間傳送數據時同時傳一個和數據保持特定相位關系的時鐘,接收器就可以根據這個時鐘的相位來準確采集相應的數據。如圖所示,分別是系統同步和源同步接口示例圖。

在系統同步接口中,系統時鐘到發送器和接收器之間的時延很難確定,所以接收器比較難確定時鐘和數據之間的相位關系,采集到的數據很難保證正確。

所以系統時鐘只適用于低速時鐘低速數據的收發。而源同步接口的好處就在于可以以較高的頻率高速收發數據,數據和時鐘由發送器同步給出,在電路板上數據和時鐘布線等長,時延相等,接收器接收到的數據和時鐘的相位關系基本保持不變。

所以對于源同步接口的時序約束也較為簡單,我們只需要告訴FPGA上游芯片發送端口數據和時鐘的相對關系,FPGA布局布線時就會調整時鐘和數據的布線長度,使接收數據時滿足時序要求。

GMII的數據收發就是一個典型的源同步接口。MAC接收數據的時鐘Rx_clk和數據Rxd由上游PHY同步給出;MAC發送數據時發送時鐘Gtx_clk和數據Txd也是同步給到PHY,所以我們對于GMII接口的時序約束就可以按照源同步接口的方法。

SOC系統的時序接口及約束

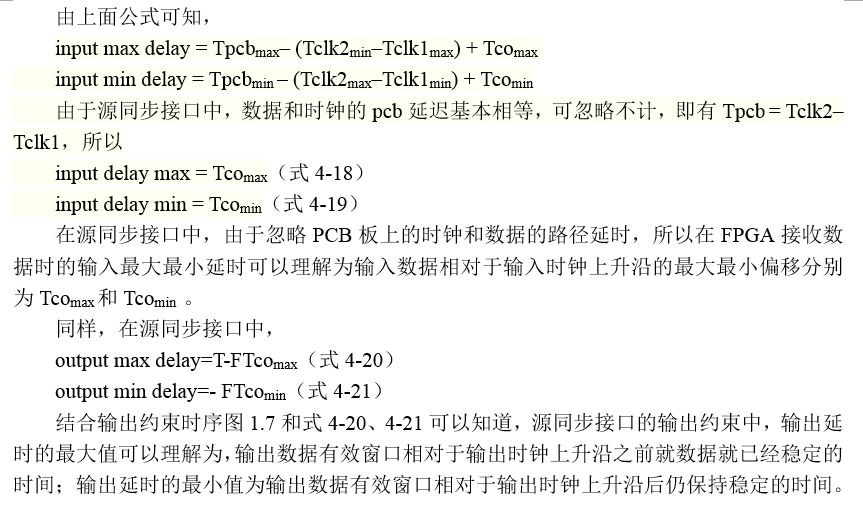

若系統外部PHY芯片的型號是RTL8211EG,其芯片手冊中給出了PHY接口處的時序,如圖所示:

RTL8211EG芯片GMII接口時序關系

對于輸入時鐘的約束

時鐘輸入接口約束

GMII接口的Rx_clk時鐘是125MHZ,頻率較高。這時由外部器件進入FPGA內部的時鐘可能不穩定,采集Rxd數據時會有影響,這時我們應先對輸入的時鐘進行約束。

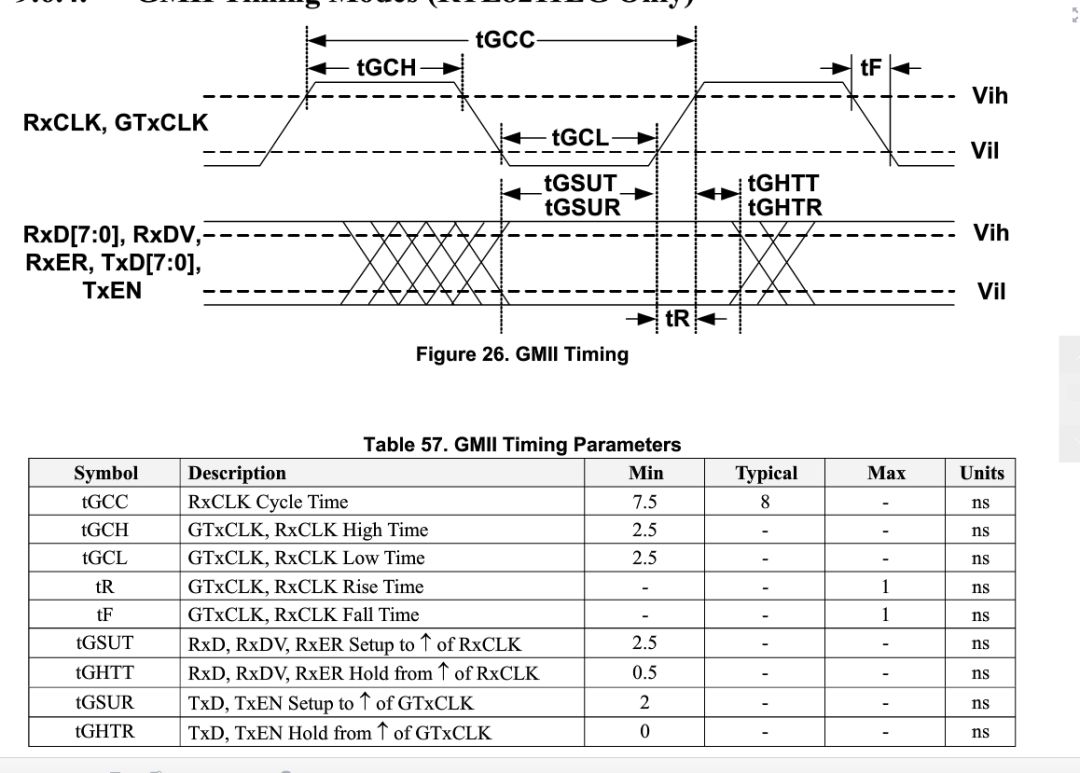

如果不加PLL,即直接時鐘模式,一般不改變時鐘特性直接進行數據采集,這通常適用于低速輸入且中心對齊的單速率源同步接口;如果在輸入端加一個PLL,即采用PLL時鐘模式,PLL可對時鐘與數據的關系進行精確調整,適用于高速輸入的中心對齊和邊沿對齊的源同步接口。因此,使用PLL時鐘對調整FPGA的接口時序有很大幫助。

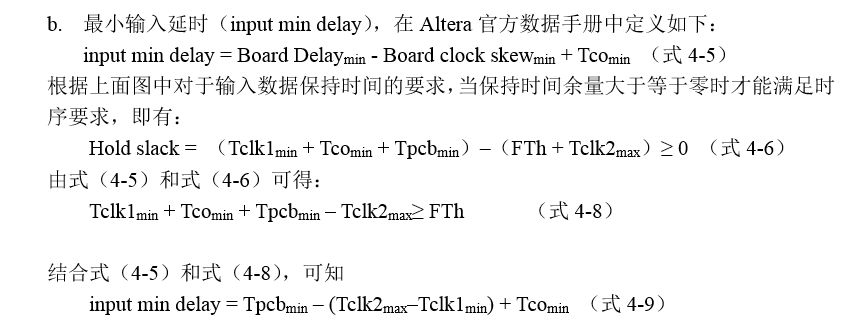

由圖1.4中輸入時序接口可以看出Tco即為時鐘上升沿與數據的偏移,則RTL8211EG中MAC接收端口Tco(max) =T-tR/2-tGSUT=8-0.5-2.5=5ns,最小Tco(min)=tGHTT+ tR/2=1ns,

故相對于Rx_clk的輸入最大最小延時

input delay max = Tco(max) =5ns

input delay min = Tco(min) =1ns

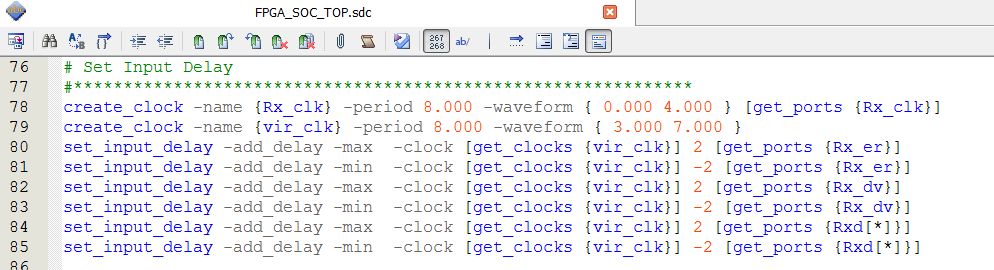

以上的約束的輸入延時是相對于輸入時鐘Rx_clk的約束,在sdc約束中我們還可以設置一個虛擬時鐘(可以假設是上游器件寄存器的驅動時鐘,用于計算源器件的啟動沿),源同步接口輸入數據以這個虛擬時鐘為參考輸入FPGA,所以當我們聲明輸入延時時就可以以這個虛擬時鐘作為啟動時鐘。使用虛擬時鐘約束輸入延時的好處是可以是約束更加方便、更加精確。

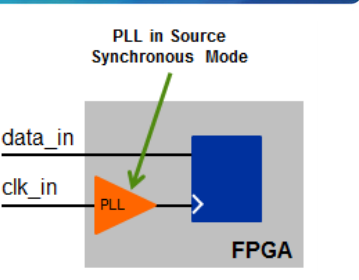

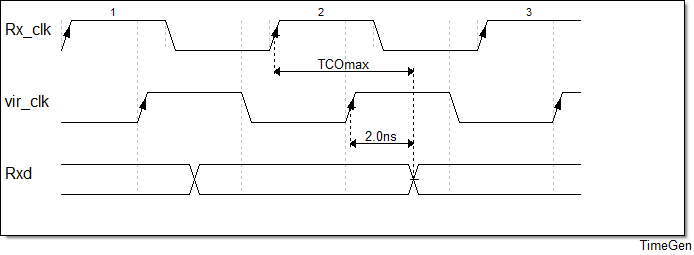

輸入約束的時延值可以理解為有效數據沿相對于時鐘的偏移,如果時延值為正說明數據相對于時鐘向后偏移,時延為負說明數據相對于時鐘向前偏移。根據上面描述輸入數據相對于輸入時鐘Rx_clk的最大最小延時分別為1ns和5ns,下面我們計算輸入數據相對于虛擬時鐘vir_clk的延時值。

取Rx_clk的上升下降時間分別為0、4ns(周期8ns),取數據時延Tco的平均值3ns為vir_clk相對于Rx_clk的偏移,即vir_clk的上升下降時間分別為3、7ns。

根據下圖所示,當Tco取1ns時,Rxd有效時相對于Rx_clk上升沿偏移1ns,相對于vir_clk上升沿偏移-2ns;當Tco取5ns時,Rxd有效時相對于Rx_clk上升沿偏移5ns,相對于vir_clk偏移2ns。

Tco取最小值時Rxd相對于vir_clk關系圖

Tco取最大值時Rxd相對于vir_clk關系圖

根據上述描述,我們以虛擬時鐘vir_clk為參考時鐘,約束如下:

sdc中的輸入延時約束

當然,我們也可以用Rx_clk作為參考來約束輸入延時,但是quartus在布局布線時,以輸入時鐘為參考的約束不夠精確,有時仍會出現時序錯誤。

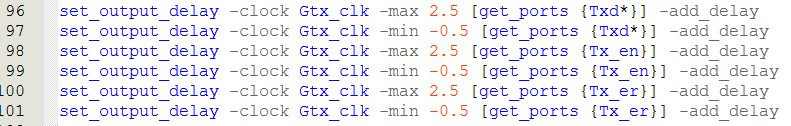

對于GMII發送數據約束時,由于發送時鐘和發送數據布線時延可忽略,故FPGA發送端口和PHY接收端口數據時鐘相位關系相似。結合圖1.4中發送接口時序和RTL8211EG的圖表可以看出:

FTco(max)+tGSUR+tR/2=Tclk,FTco(min)=tGHTR+ tR/2

故有

output delay max=Tclk- FTco(max)=tGSUR+tR/2=2.5ns

output delay min=- FTco(min)= -(tGHTR+tR/2)=-0.5ns

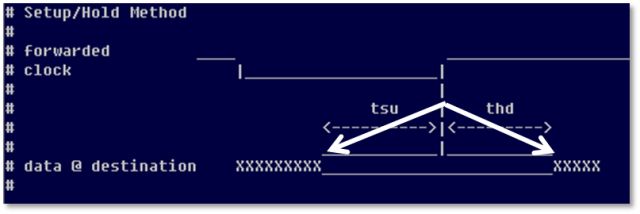

SDR接口輸出約束含義

所以,在sdc中我們如下約束輸出接口:

在上面的輸出約束中,我們可以理解為:

根據outputdelay中max/-min的定義,源同步接口中輸出最大最小延時為輸出時鐘上升沿到達之前最大與最小的數據有效窗口。如圖所示,用于建立時間分析的set output delay –max的值為正數2.5ns,表示數據窗口在Gtx_clk上升沿之前2.5ns時間內有效,

而用于保持時間分析的 -min之后跟著負數-0.5ns,表示數據在Gtx_clk上升沿之后0.5ns內有效,即相對于Gtx_clk輸出數據有效窗口為-0.5ns到2.5ns,這個范圍大于等于PHY芯片手冊中給出的Txd相對于Gtx_clk的窗口范圍時,才能滿足PHY芯片采集Txd時的時序要求。

Quartus的邏輯分區約束

既然是FPGA和外部接口的時序問題,也就是輸入輸出的寄存Rxd/Txd的寄存器到外部器件寄存器的時序問題。

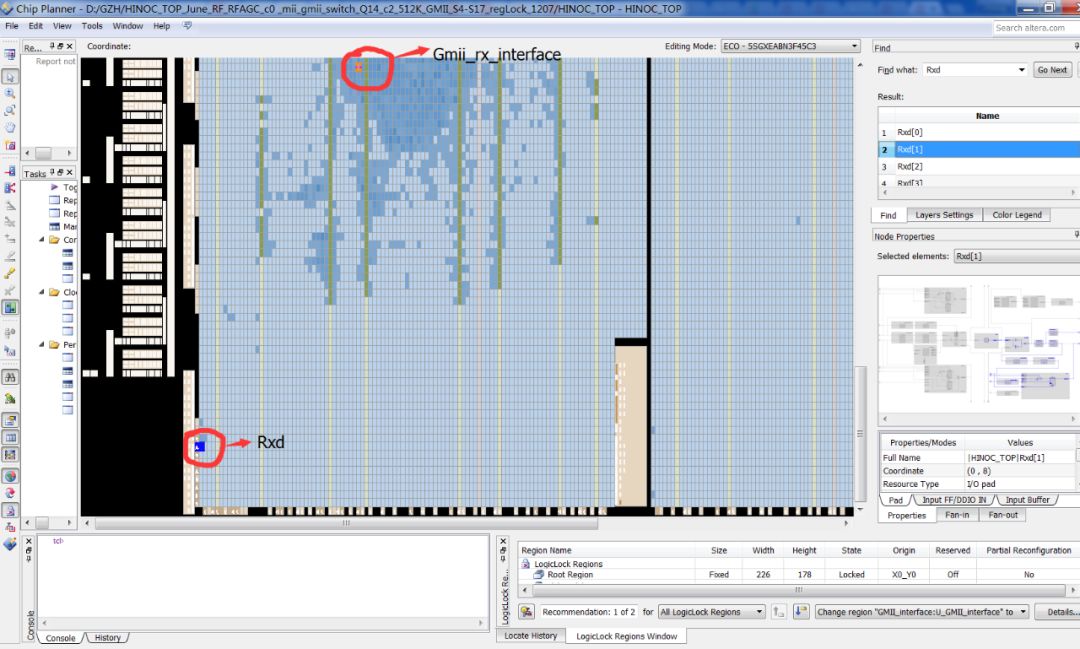

GMII接收數據路徑分析

Tpcb是外部PCB板上數據的延時,Tdata_i是數據的輸入延時,Gmii_rx_interface相當于Rxd進入FPGA后的第一個寄存器模塊(可以專門寫一個接口模塊,將Rxd數據打一拍,用于接收數據)。

如果Gmii_rx_interface距離接口Rxd較遠,Tdata_i的路徑較長,布局布線時Rxd的八根線時延相差可能就比較大,所以我們應讓這個模塊放在距離Rxd接口較近的地方。

Quartus軟件中有一個LogicLock(物理分區)功能,把Gmii_rx_interface模塊建立成一個LogicLock分區但并不對分區位置和大小進行固定,然后重新編譯工程。

布局布線后就可以在chipplaner工具中看到這個分區的位置,如下圖所示(放大可以看清),Gmii_rx_interface模塊距離Rxd接口位置很遠,布局布線時,輸入信號要繞很長一段距離才會到達輸入的寄存器,資源占用很多時,Rxd的8根數據線長度不一,很容易造成時序問題。

未固定分區位置時布局布線結果

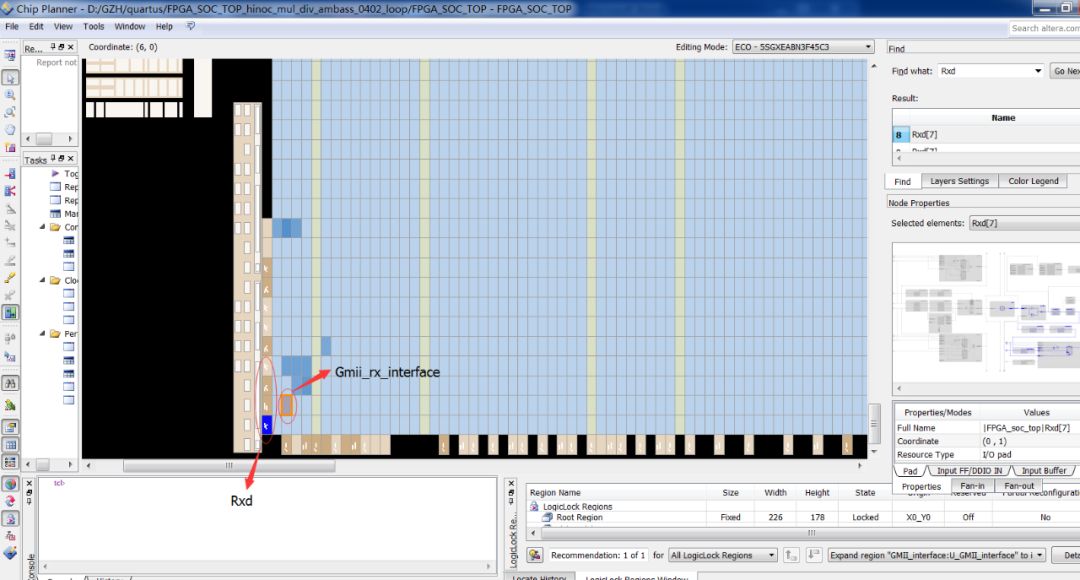

把Gmii_rx_interface模塊分區移動到Rxd接口附近進行固定然后重新編譯工程,布局布線后該邏輯分區就會在Rxd接口附近,從而保證輸入數據接口進入FPGA的第一個寄存器的時延在一定范圍內,保證時序要求。

采用LogicLock后,GMII寄存器接口位置

內部寄存器到寄存器時序問題

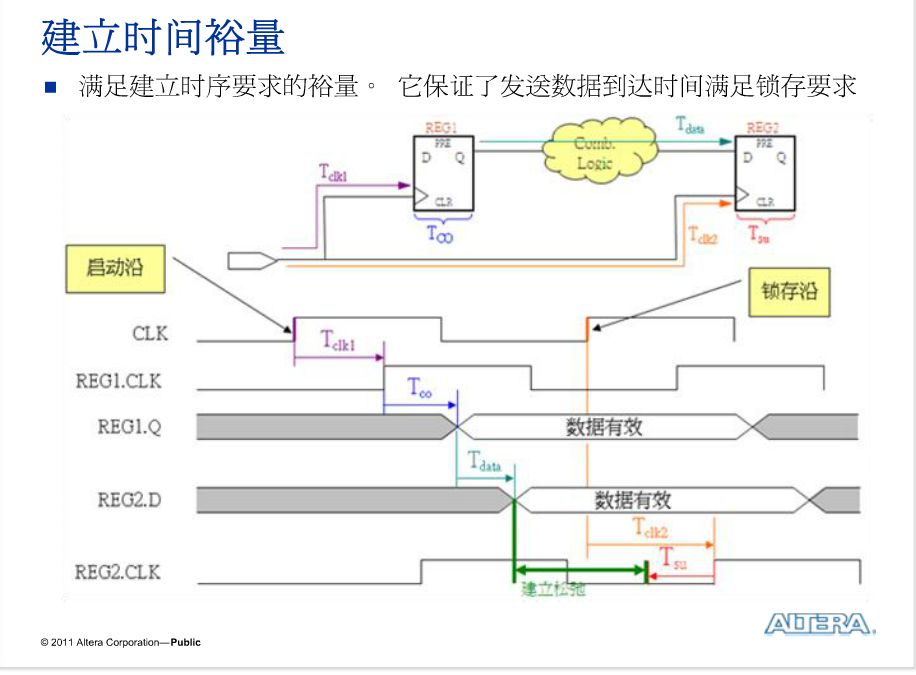

寄存器到寄存器之間建立和保持時間時序要求

在FPGA的設計中除了應該考慮到輸入輸出接口的時序,還應該考慮到內部寄存器到寄存器的時序問題。內部寄存器之間同樣要滿足建立和保持時間要求,如上圖所示

其中Tdata為組合邏輯在電路中的延時。

建立時間余量=T+Tclk2-Tclk1-Tco-Tdata-Tsu>=0

保持時間余量=Tclk1+Tco+Tdata-Tclk2-Th>=0

通常在FPGA中忽略時鐘的skew(偏移),即有Tclk2-Tclk1=0

則

建立時間余量=T-Tco-Tdata-Tsu>=0

保持時間余量=Tco+Tdata -Th>=0

為了使FPGA設計的電路正常,就必須滿足以上的建立和保持時間要求,根據建立時間余量公式可知

T>=Tco+Tdata+Tsu

F=1/T

在FPGA中Tco、Tsu等的數值由所使用FPGA的特性決定,所以時序電路之間的組合電路延時決定了整個電路的速度,即決定了整個電路的最大工作時鐘頻率。

若FPGA工作頻率為130MHZ,如果在做設計時,組合邏輯的過于復雜,寄存器到寄存器之間的延時Tdata過大,如果系統仍工作在130MHZ的頻率下就有可能出現時序問題。所以在設計時我們應盡可能減小組合邏輯的復雜度,以提高工作頻率。下面討論提高系統工作頻率的方法。

a. 通過減小Tdata值來提高頻率

在quartus的sdc約束中有關于寄存器到寄存器之間組合邏輯時延的約束,通過設置從REG1到REG2之間組合邏輯延時的最大最小值,來約束FPGA的布局布線,從而來提高系統的工作頻率。

但這種方法通常只能提高5%左右的工作頻率,不能過多的限制組合邏輯的時延,否則不利于EDA工具的布局布線。

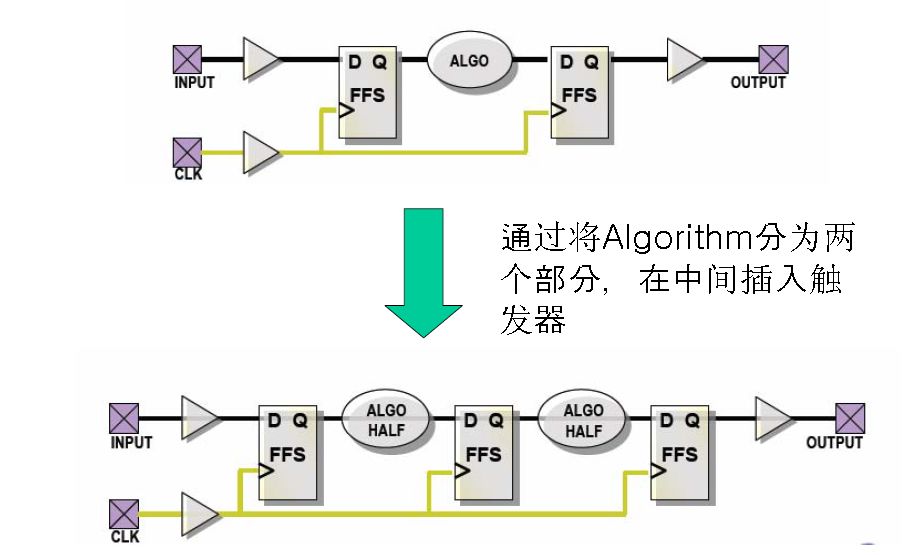

b. 采用流水線設計來提高頻率

流水線分割組合邏輯

通過約束減小組合邏輯延時的方法并不能夠十分有效的提高系統的工作頻率,所以在設計時我們應盡量減少大規模組合邏輯的使用。

如圖所示,采用流水線的設計思想,將兩個寄存器之間的組合邏輯拆分成兩級組合邏輯,從而減小組合邏輯的復雜度。采用流水線技術可以很好地提高系統運行時鐘的工作頻率。

假設原來路徑延時為t,加入兩級流水線并且假設路徑切割均勻,則路徑延時減少到約t/3,從而系統的工作頻率提高到原來3倍左右。

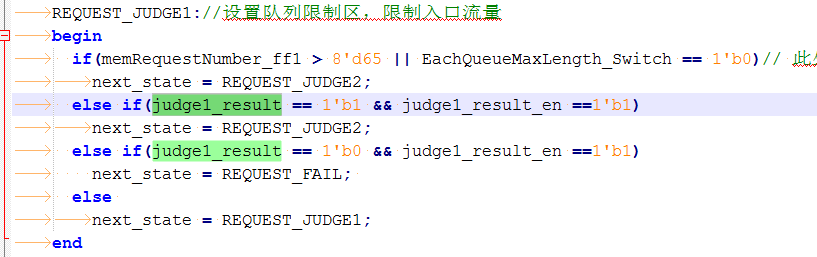

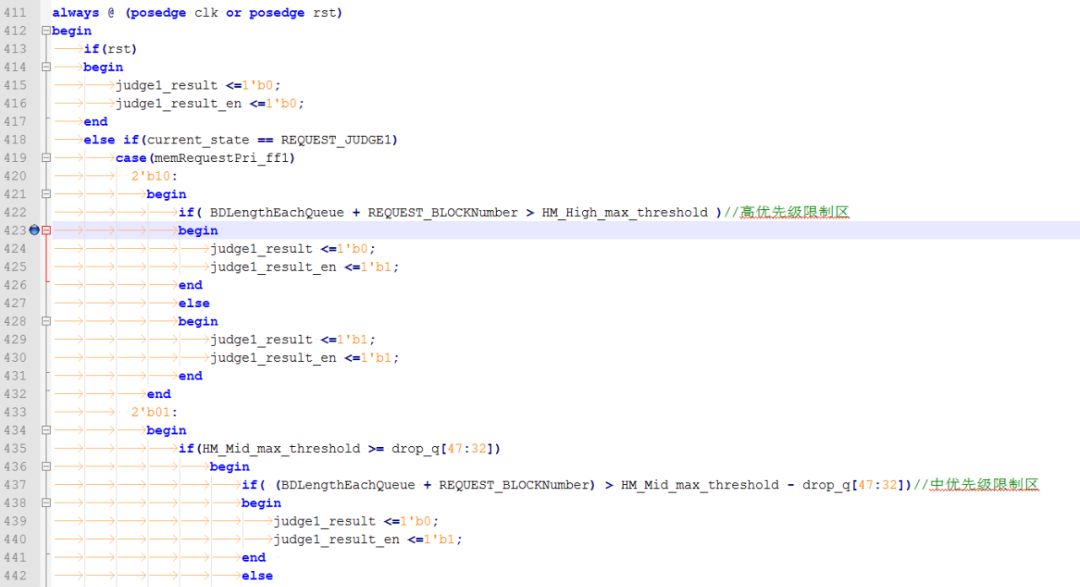

如上圖所示,在我們做FPGA設計過程中,原來的judge_result是一個很大的組合邏輯,信號產生的路徑時延很大,很難滿足時序要求,在FPGA編譯完做驗證時,出現if條件不正確的情況,狀態機不能正確跳轉。

修改:將if中復雜的組合邏輯信號在時鐘的上升沿,賦值給中間變量寄存器judge_result和judge_result_en,這樣在做if判斷時就不用判斷原來的復雜組合邏輯值,只需判斷judge_result和judge_result_en的值。即采用流水線分割的方法把原來十分復雜的組合邏輯分成兩部分,這樣FPGA在編譯后就不會出現時序錯誤的情況。

實例:使用vivado進行簡單的時鐘約束

之所以要進行時鐘約束是因為:當時鐘進入了FPGA器件,通過時鐘樹傳遞時,時鐘邊沿會有延時,通常稱作時鐘網絡延遲;噪聲或硬件表現會導致時鐘隨時可能發生變化,通常稱作時鐘不確定性,包括時鐘抖動、相位錯位等等。

增加時鐘約束可以一定程度上減少時鐘延時帶來的問題,比如大位寬數據(128位)從ram中讀出時由于路徑延時導致數據錯誤的問題。

這里介紹一下簡單進行時鐘約束的辦法(以vivado2018.2為例):

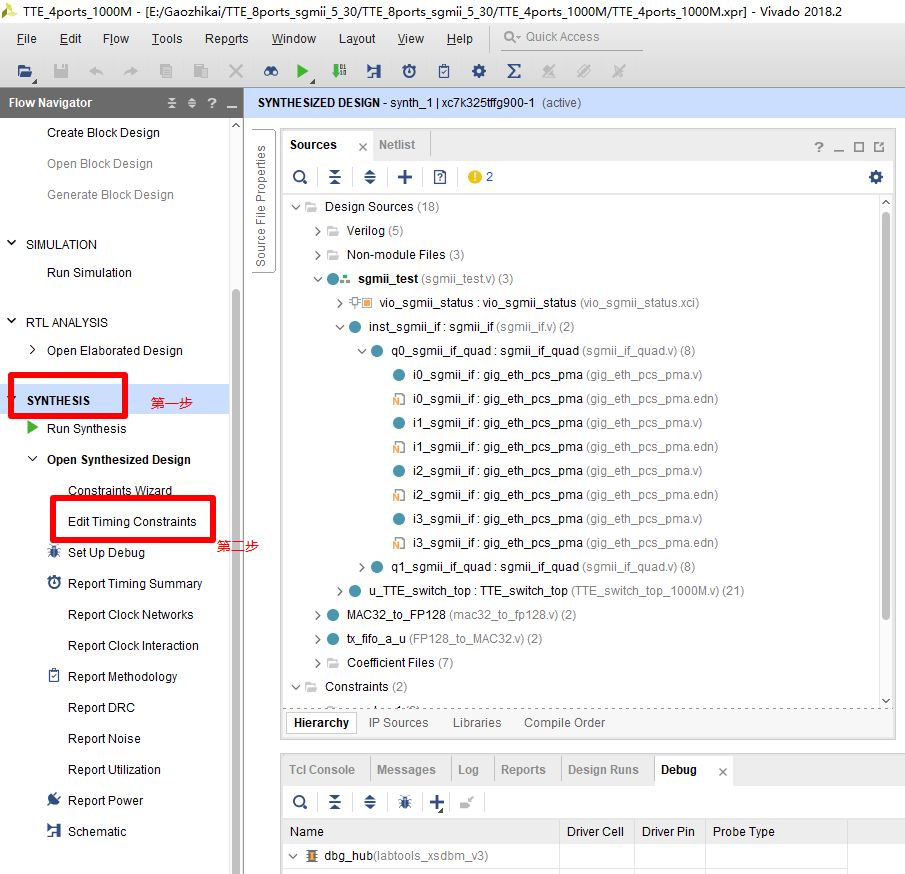

第一步:對工程進行綜合,綜合之后點擊“Edit Timing Constraints”

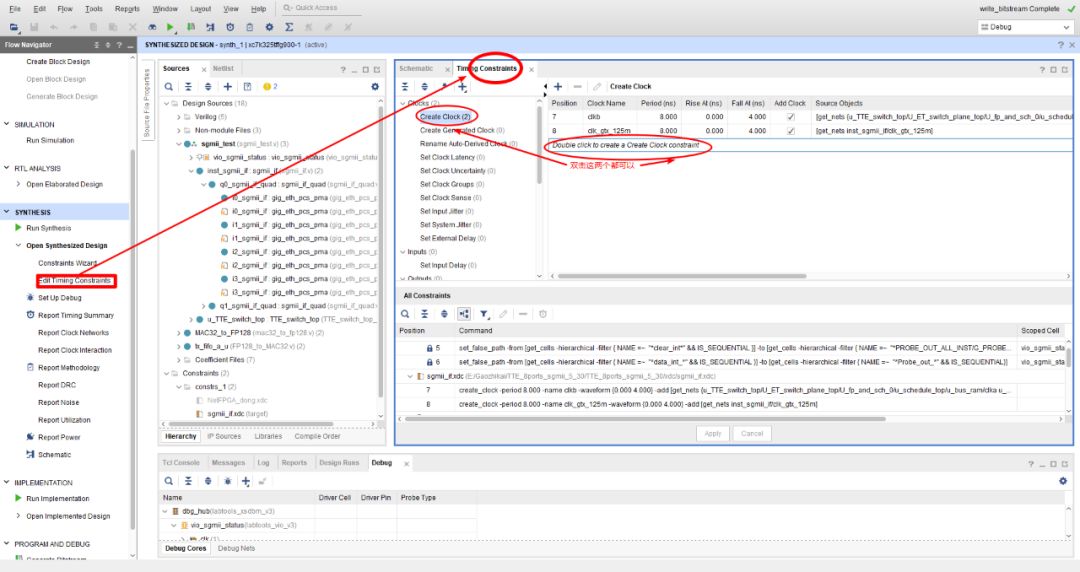

第二步,打開之后看到如下界面:

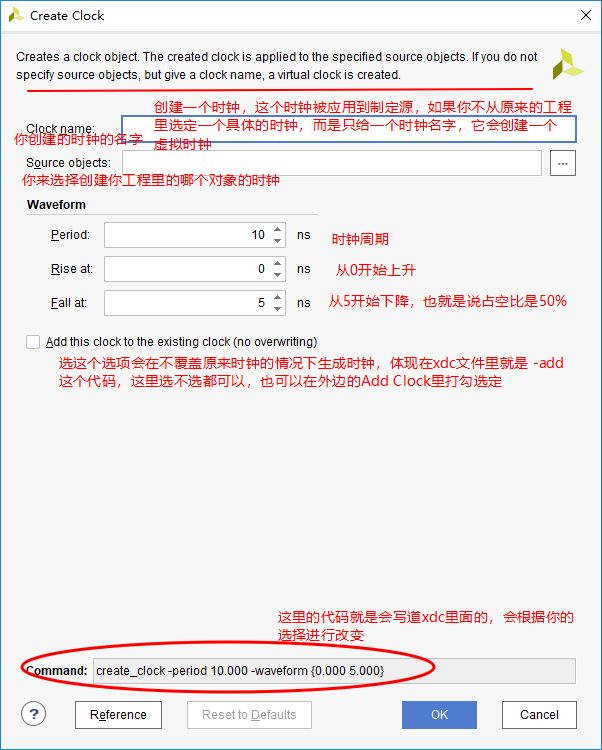

第三步,雙擊create clock,打開如下界面:

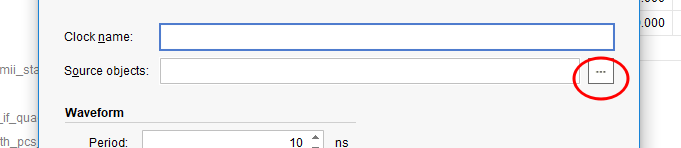

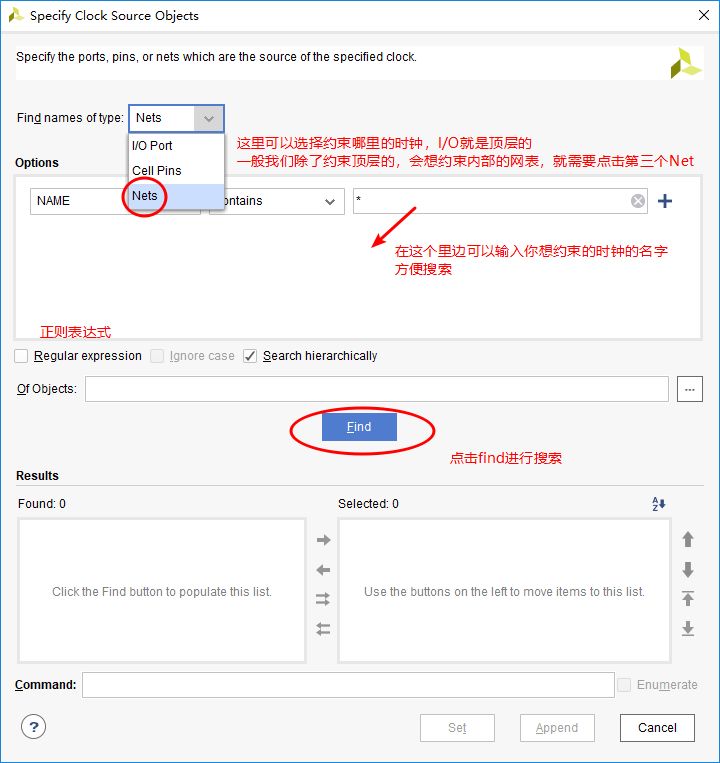

第四步,一般會點擊sourcesobjects 旁邊的這個按鈕來選擇你要約束的時鐘:

點擊之后彈出如下界面:

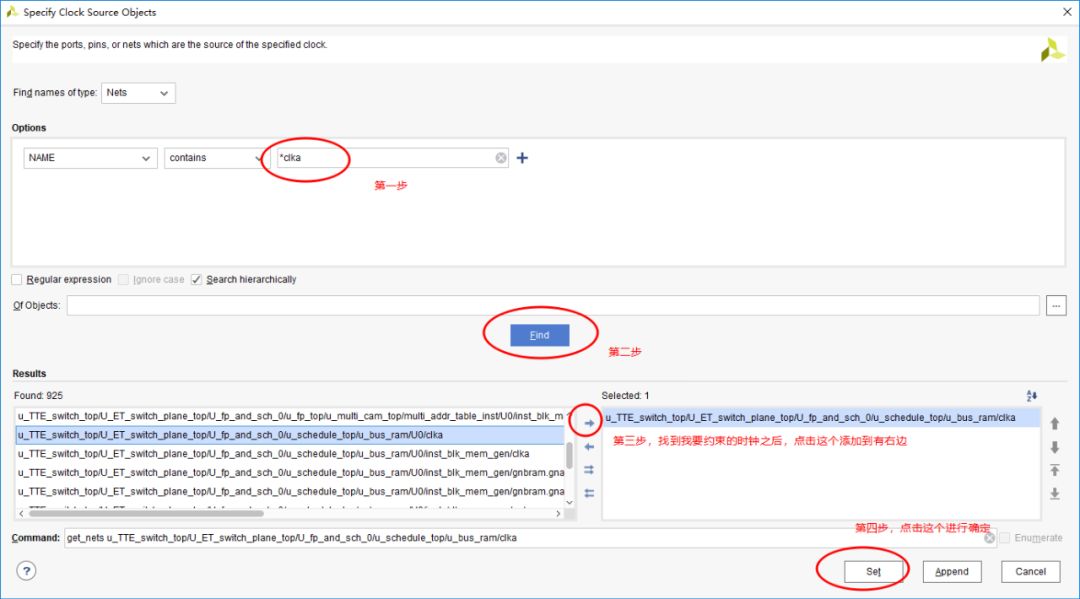

第五步,輸入你要約束的時鐘,然后進行查找,找到之后按照如下添加到右側框內,然后點擊set:

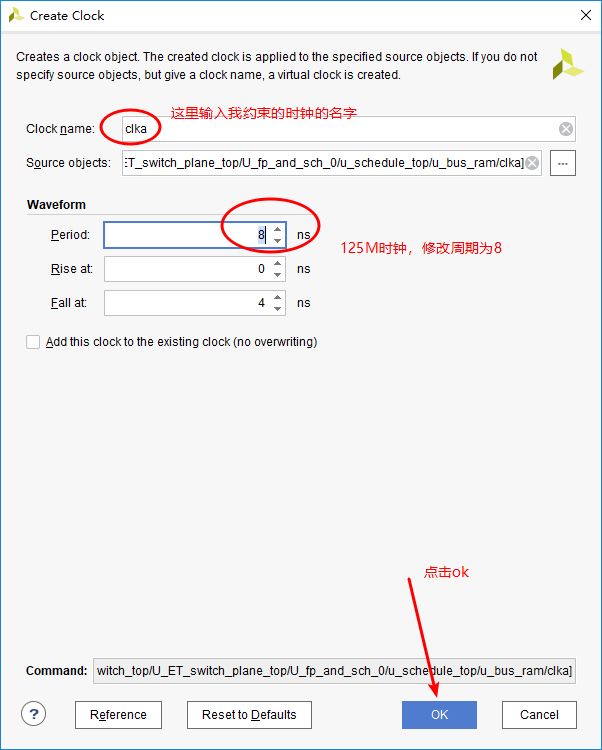

第六步,然后set之后會返回到這個界面,你需要在這個界面輸入時鐘名,不然會生成一個虛擬時鐘:

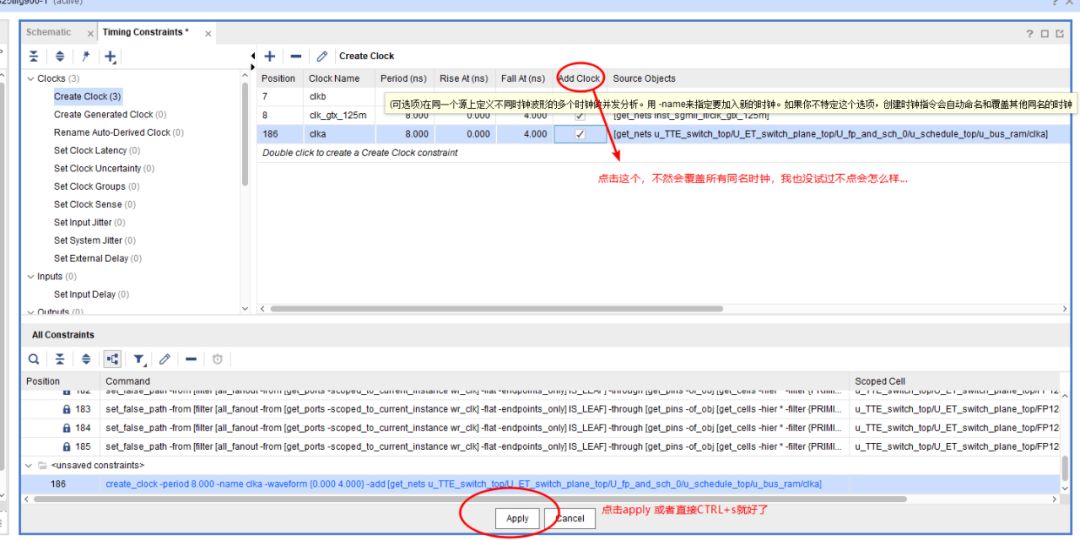

第七步,然后到這個界面,按照圖片進行操作:

一般來說要點擊add clock,然后按crtl+s保存你設置的時鐘約束,之后再點擊apply(或者直接點擊apply)。

然后你打開你的xdc文件,會發現已經有了這么一個約束了,然后再重新綜合和實現就好了。

create_clock -period 8.000-name clkb -waveform {0.000 4.000} -add [get_nets{u_TTE_switch_top/U_ET_switch_plane_top/U_fp_and_sch_0/u_schedule_top/u_bus_ram/clkau_TTE_switch_top/U_ET_switch_plane_top/U_fp_and_sch_0/u_schedule_top/u_bus_ram/clkb}]

create_clock -period 8.000-name clk_gtx_125m -waveform {0.000 4.000} -add [get_netsinst_sgmii_if/clk_gtx_125m]

全文完。

來源:本文轉載自網絡交換FPGA公眾號

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605996 -

寄存器

+關注

關注

31文章

5363瀏覽量

121158 -

時序分析

+關注

關注

2文章

127瀏覽量

22615 -

時序約束

+關注

關注

1文章

115瀏覽量

13457

原文標題:FPGA中的時序約束--從原理到實例

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA主時鐘約束詳解 Vivado添加時序約束方法

深入了解時序約束以及如何利用時序約束實現FPGA 設計的最優結果

詳解FPGA的時序input delay約束

深度解析FPGA中的時序約束

深度解析FPGA中的時序約束

評論