當(dāng)柵與襯底之間存在壓差時(shí),它們之間存在電場(chǎng),靜電邊界條件使多晶硅靠近氧化層界面附近的能帶發(fā)生彎曲,并且電荷耗盡,從而形成多晶硅柵耗盡區(qū)。該耗盡區(qū)會(huì)在多晶硅柵與柵氧化層之間產(chǎn)生一個(gè)額外的串聯(lián)電容。當(dāng)柵氧化層厚度減小到 2nm 以下,此電容的影響也會(huì)變得越來越嚴(yán)重,已經(jīng)不再可以忽略。

多晶硅柵耗盡的寬度不像襯底量子效應(yīng)那么復(fù)雜,它只需要采用簡(jiǎn)單的靜電學(xué)就可以估算柵耗盡區(qū)的寬度。重?fù)诫s的柵的摻雜濃度比輕摻雜的溝道的摻雜濃度要高,在亞閾值區(qū),氧化層界面電位移的連續(xù)性意味著柵極的能帶彎曲小于襯底的能帶彎曲。考慮一個(gè)偏置到反型區(qū)的NMOS 的n型重?fù)诫s的多晶硅,平帶電壓(VFB)和襯底電壓降(Φs)、柵電壓降(Φg)、氧化層電壓降(Vox)之和等于柵壓(Vg):

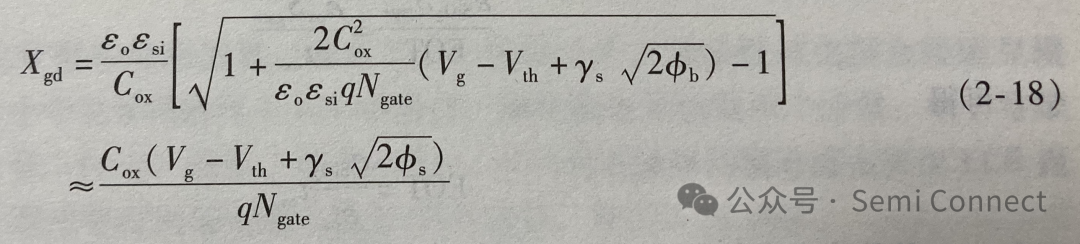

利用柵氧化層的邊界條件和高斯定理對(duì)公式(2-17)進(jìn)行化簡(jiǎn)求解,當(dāng)Vg>Vth時(shí),求得柵耗盡的寬度Xgd的公式如下:

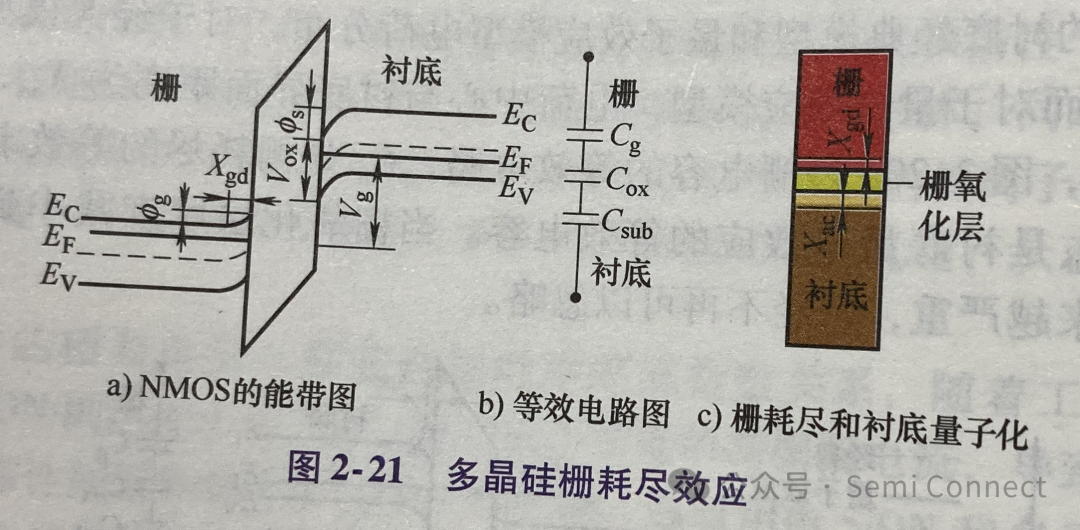

圖2~21a所示為柵極耗盡層的寬度Xgd,圖2-21b所示為柵耗盡的等效電容、柵氧化層的等效電容和襯底量子效應(yīng)的等效電容的等效電路圖,圖2-21c所示為柵耗盡和襯底量子化的示意圖。

-

多晶硅

+關(guān)注

關(guān)注

3文章

241瀏覽量

29382 -

靜電

+關(guān)注

關(guān)注

1文章

508瀏覽量

36494 -

NMOS

+關(guān)注

關(guān)注

3文章

296瀏覽量

34572

原文標(biāo)題:多晶硅柵耗盡效應(yīng)

文章出處:【微信號(hào):Semi Connect,微信公眾號(hào):Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【轉(zhuǎn)】一文看懂MOS器件的發(fā)展與面臨的挑戰(zhàn)

分析MOS管未來發(fā)展與面臨的挑戰(zhàn)

低溫多晶硅的工作原理是什么?

什么是多晶硅

多晶硅光電池

低溫多晶硅,低溫多晶硅是什么意思

多晶硅上市公司有哪些_國(guó)內(nèi)多晶硅上市公司排名

多晶硅生產(chǎn)流程是什么_單晶硅與多晶硅的區(qū)別

多晶硅柵(Poly-Si Gate)

多晶硅內(nèi)摻雜物的擴(kuò)散效應(yīng)

多晶硅柵工藝的制造流程

多晶硅柵耗盡效應(yīng)簡(jiǎn)述

多晶硅柵耗盡效應(yīng)簡(jiǎn)述

評(píng)論