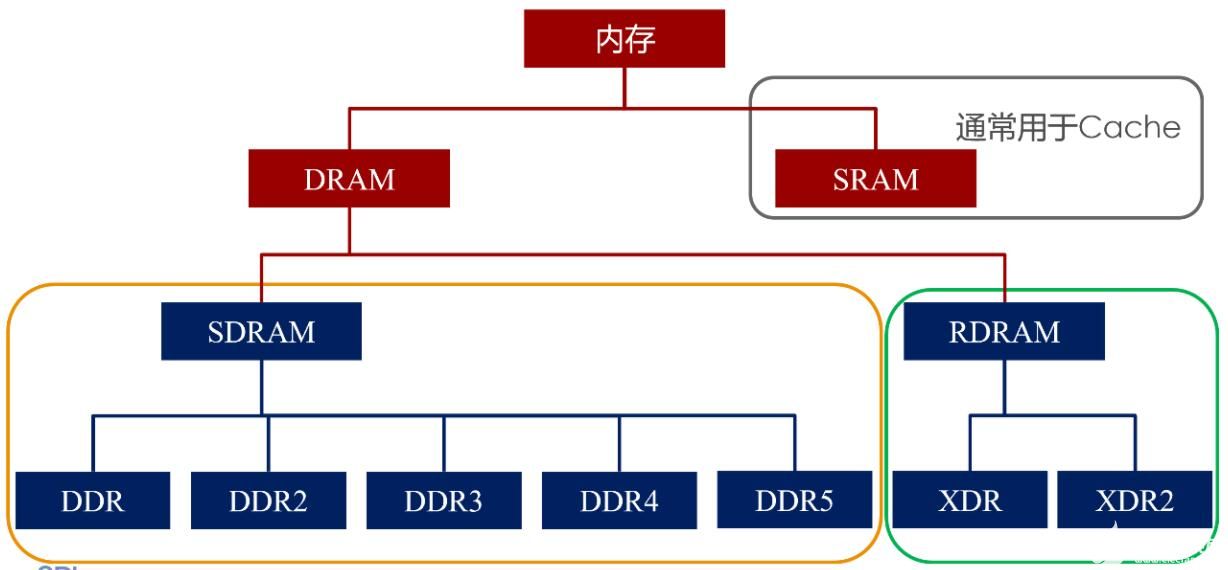

DRAM從20世紀70年代初到90年代初生產,接口都是異步的,其中輸入控制信號直接影響內部功能。

同步DRAM(SDRAM)設備比DRAM設備有顯著的改進。在兩個方面與前幾代DRAM設備不同:

1.增加了時鐘信號;因此,SDRAM具有同步接口,也就是說是命令而不是信號在控制存儲單元。?

2.SDRAM包含多個獨立bank。

3.SDRAM支持burst突發模式傳輸。

SDRAM有一個時鐘信號,所有內部動作都發生在其邊沿。

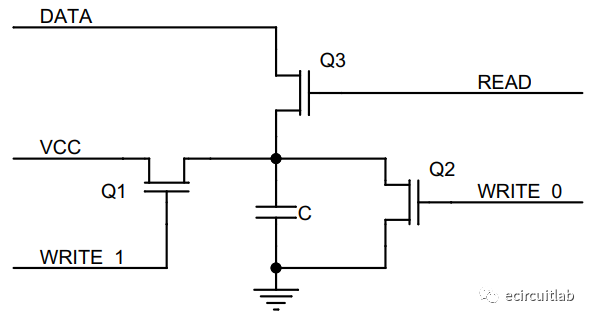

在DRAM中,來自內存控制器的RAS、CAS和WE信號直接控制內部latch和輸入/輸出buffer,這些信號可以隨時到達DRAM的引腳。然后,DRAM立即響應RAS、CAS和WE信號。

相反,在SDRAM中,RAS、CAS和WE信號不能直接控制內部latch 和buffer。在SDRAM中,這些信號形成一個命令總線,用于將命令傳輸到內部狀態機,該狀態機在時鐘信號的邊沿執行命令。通過這種方式,內部latch和輸入/輸出buffer的控制從外部內存控制器移動到SDRAM控制邏輯中的狀態機。

每個SDRAM中存在多個獨立bank,這意味著當一個bank忙于行激活命令或預充電命令時,內存控制器可以向不同的bank發送新命令。現在可以在單個SDRAM中將內存請求交錯到不同的bank。SDRAM包含2、4或8個獨立bank。BA0、BA1和BA2決定了命令指的是哪個bank。

功能描述

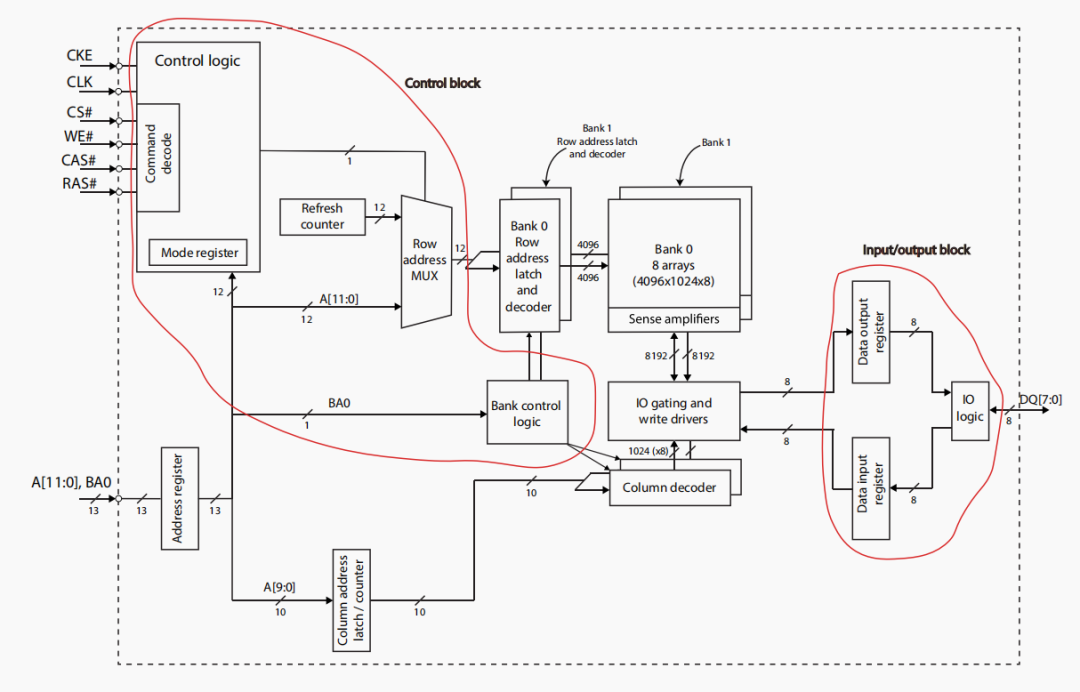

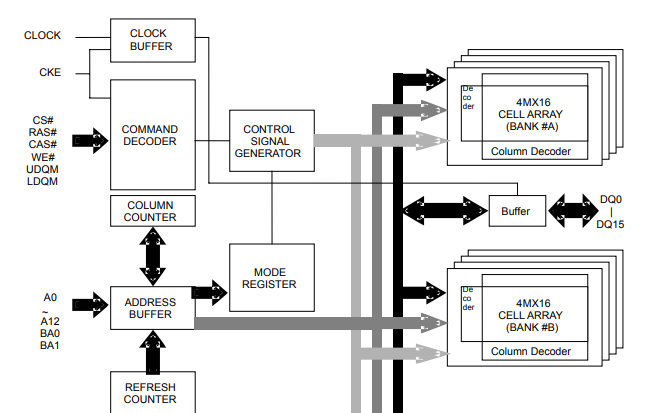

下圖顯示了具有兩個獨立bank的SDRAM的簡化框圖。

每個bank都有其行地址latch和解碼器、列解碼器和靈敏放大器。圖中SDRAM中的每個bank由8個大小為4096x1024位的DRAM陣列組成。該地址現在由bank號碼(BA)、行地址(A[11:0])和列地址(A[9:0])組成。

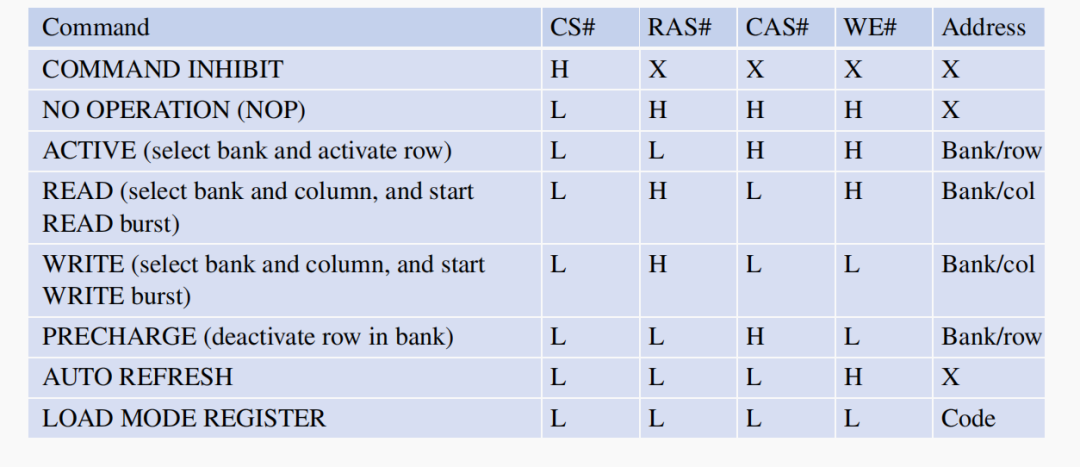

在SDRAM中,命令在時鐘信號(CLK)的上升邊沿解碼,如果芯片選擇信號(CS)處于有效狀態。該命令由外部內存控制器在命令總線上發起。命令總線由WE、CAS和RAS信號組成。所有這些信號都是低有效。

下表顯示了SDRAM的命令集合。只要CS不處于有效狀態,SDRAM就會忽略命令總線上的信號。

圖中框出來的SDRAM控制模塊由控制邏輯、選擇行地址的多路復用器、刷新計數器和存儲體控制邏輯組成。其中刷新計數器跟蹤要刷新的行,多路復用器用于選擇要傳送到行地址鎖存器和解碼器的行地址。地址可以是來自刷新計數器的地址(用來控制邏輯執行刷新周期),也可以是來自DRAM控制器的外部地址總線上的地址。

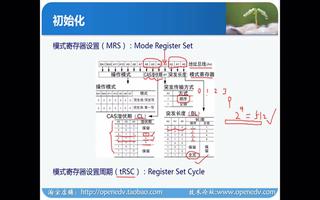

控制邏輯包含命令解碼器、執行命令的有限狀態機和模式寄存器。模式寄存器是一個可編程的10位寄存器,其決定:

·CAS延遲(CL)

·burst傳輸的長度

·以及內存數據在burst傳輸中的順序。等等

控制邏輯從命令總線接收命令,然后根據命令類型和模式寄存器相應字段中的值執行特定的操作序列。這些操作由內部狀態機在連續的時鐘周期上執行,而不需要來自memory控制器的時鐘控制。

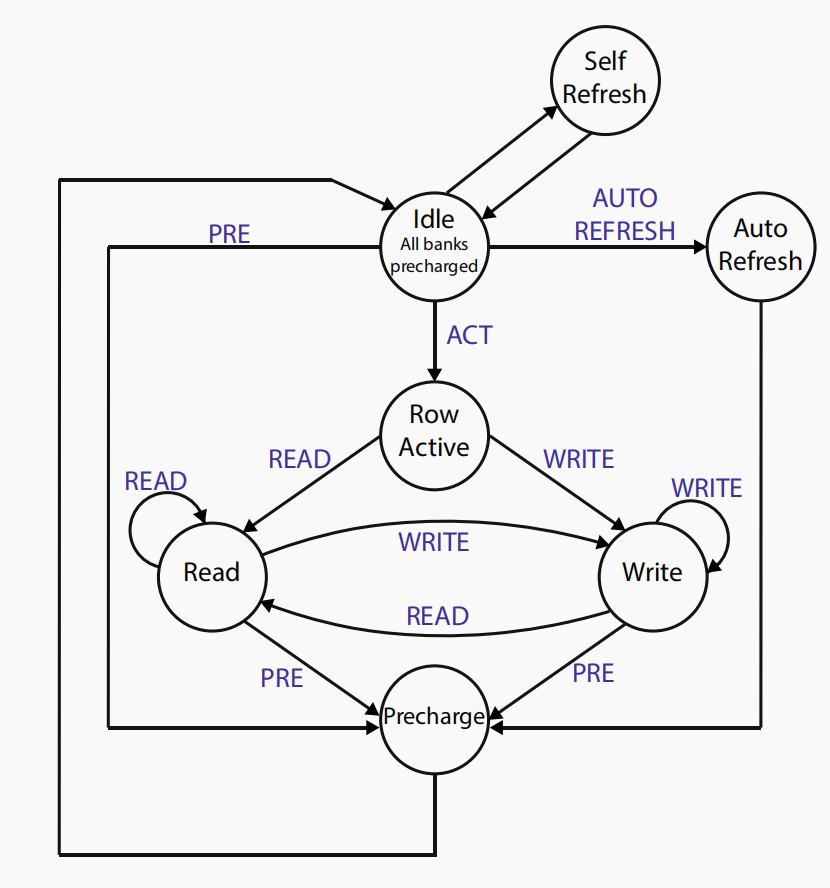

上圖顯示了內部狀態機的簡化狀態圖。在初始化模式寄存器后,內部狀態機處于idle狀態,所有行和列均預充電。如果沒有向SDRAM發出命令,SDRAM芯片將定期執行自刷新操作。內部計數器驅動自刷新操作。

開始內存訪問時,內存控制器應首先發出ACTIVE命令。這將打開某些bank/行,內部狀態機在active狀態下等待其他命令。

要讀取數據,內存控制器應發出READ命令,要將數據寫入內存,內存控制器應發出WRITE命令。然后內部狀態機進入讀或寫狀態,并使用列地址生成適當的內部信號來訪問列。

READ或WRITE命令后面可以跟任意數量的READ或WRITE命令,或者可以發出PRECHARGE命令來恢復數據并關閉打開的bank/行。

在執行預充電操作后,內部狀態機將恢復到IDLE狀態。

例如,在 ACTIVE 命令的情況下,狀態機通過多路復用器將行地址傳遞到行地址鎖存器和譯碼器。地址位BA確定要訪問的行,然后打開選定的行,并將其內容傳輸到靈敏放大器。

當存儲器控制器發起讀取命令時,內部狀態機驅動行控制邏輯,根據 BA 位選擇適當的列,然后從所選行的靈敏放大器中選擇數據。

每個bank都有自己的列解碼器-當從更多bank進行交錯傳輸時,就特別有用,可以隱藏RAS到CAS延遲和行預充電時間。當第一次發送指定新bank的地址時,必須打開該行。 但是當后續的訪問指定已經打開的bank中的同一行時,訪問可以很快發生,只發送列地址,而無需等待 tRCD。此功能要求每個bank都有自己的行地址鎖存器、靈敏放大器和列解碼器。

-

DRAM

+關注

關注

40文章

2326瀏覽量

183868 -

SDRAM

+關注

關注

7文章

430瀏覽量

55371 -

內存控制器

+關注

關注

0文章

40瀏覽量

8941

原文標題:同步DRAM(SDRAM)介紹

文章出處:【微信號:數字芯片實驗室,微信公眾號:數字芯片實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SDRAM的介紹及設計應用

DRAM,SRAM,SDRAM的關系與區別

EEPROM、EPROM、FLASH、SRAM、DRAM、SDRAM的區別.

求大佬詳細介紹一下DRAM、SDRAM及DDR SDRAM的概念

從DRAM到廣泛使用的SDRAM

有關arm裸機SDRAM的相關知識介紹

DRAM SRAM SDRAM內存精華問題匯總

DRAM、SDRAM及DDR SDRAM之間的概念詳解

正點原子開拓者FPGA視頻:SDRAM簡介

正點原子開拓者FPGA:SDRAM時序操作

EM63A165 SDRAM高速CMOS同步DRAM的數據手冊免費下載

SDRAM與DDR之間的主要差異是什么

同步DRAM(SDRAM)介紹

同步DRAM(SDRAM)介紹

評論