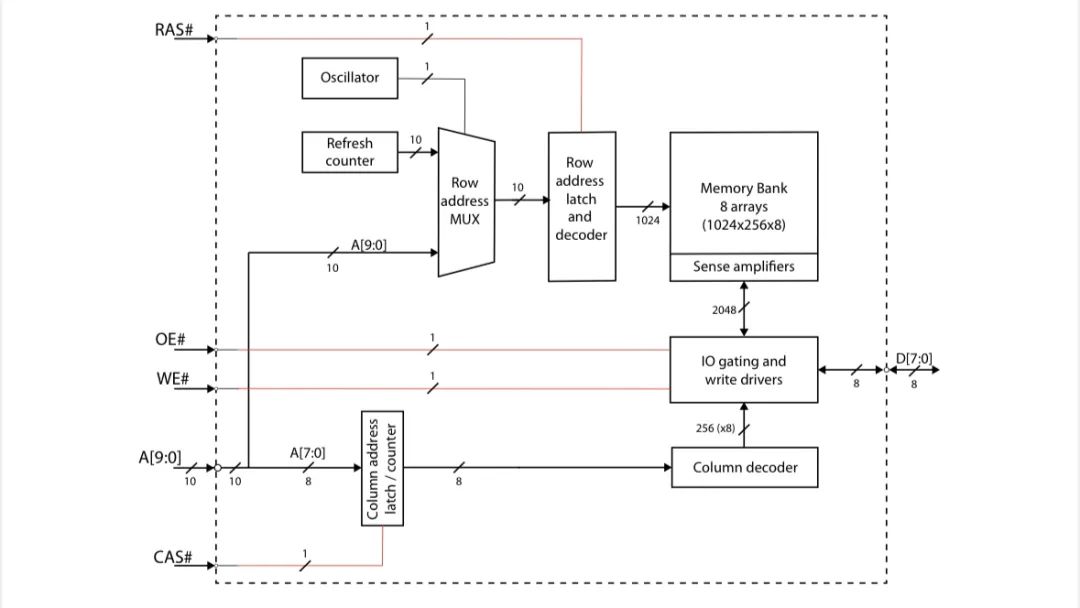

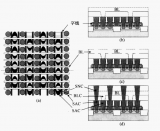

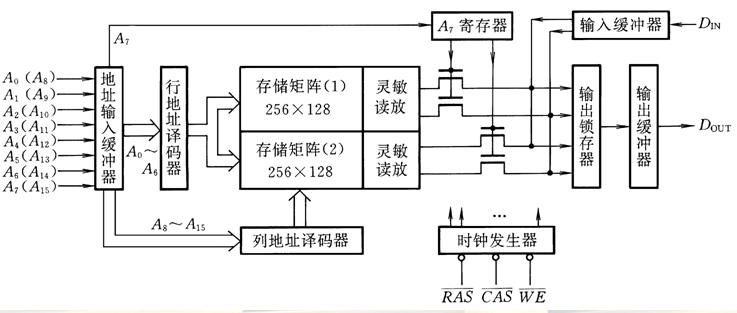

如果內存是一個巨大的矩陣,那么DRAM芯片就是這個矩陣的實體化。如下圖所示,一個DRAM芯片包含了8個array,每個array擁有1024行和256列的存儲單元。

當訪問這些存儲單元時,芯片可以一次性讀取或傳輸8個比特(D0到D7)。這個過程涉及到兩個關鍵的組件:行地址解碼器和列選擇器。行地址解碼器負責激活與給定行地址對應的字線,而列選擇器則用于從給定的列地址中選擇正確的列。

地址線的復用

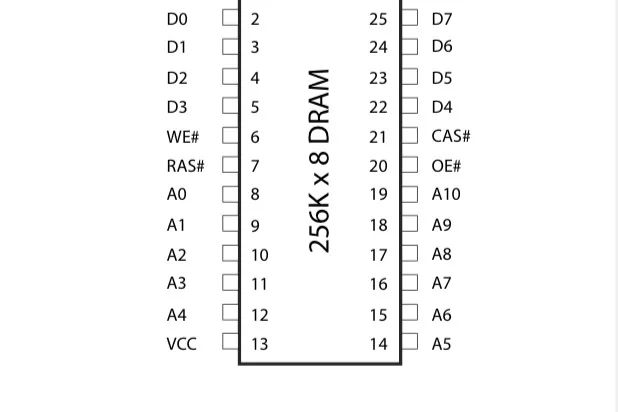

由于DRAM的容量巨大,如果直接為每一行和每一列分配地址線,那么所需的地址線數量將會非常龐大。例如,在一個32256行1024列的array中,我們需要15位來選擇一個字,10位來選擇一個列。為了解決這個問題,地址線采用了復用技術。首先,行地址被應用到地址線上,然后是列地址。這樣,所需的地址引腳數量幾乎減半。

控制信號的作用

在數據傳輸過程中,還需要兩個額外的控制信號來指示當前總線上是哪種地址:行訪問選通row access strobe(RAS)和列訪問選通column access strobe(CAS)。當RAS信號被激活時,地址位A0到A9被鎖存到行地址鎖存器中。類似地,當CAS信號被激活時,地址位A0到A7被鎖存到列地址鎖存器中。

此外,還需要兩個控制信號來正確地將數據傳輸到DRAM芯片或從芯片中讀取數據。寫使能(WE)信號用于選擇讀或寫操作。低電平表示需要寫操作;高電平則用于選擇讀操作。

在讀操作期間,輸出使能(OE)信號用于防止數據在需要之前出現在輸出端。當OE為低時,數據一旦可用就會出現在數據輸出上。在寫操作期間,OE則需要一直保持高電平。

最后,讓我們來澄清一個常見的誤解:許多人認為內存在物理上是可以以線性向量的形式組織的,而不是以行和列的矩形陣列。實際上,這種組織方式在理論上可能是理想的,但在物理上卻是不可能的。因為如果內存以這種方式組織,位線會非常長,電容也會非常大,這將使得檢測微小的電壓變化變得不可能,也就是無法判斷電容存儲的是0還是1。

-

解碼器

+關注

關注

9文章

1147瀏覽量

40931 -

存儲單元

+關注

關注

1文章

63瀏覽量

16185 -

DRAM芯片

+關注

關注

1文章

84瀏覽量

18058

原文標題:DRAM芯片的基本結構

文章出處:【微信號:數字芯片實驗室,微信公眾號:數字芯片實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【內存知識】DRAM芯片工作原理

DRAM存儲原理和特點

DRAM芯片中的記憶單元分析

基于SRAM和DRAM結構的大容量FIFO的設計與實現

DRAM 原理 2 :DRAM Memory Organization

DRAM:產業結構變化孕育中國玩家進場良機

堆疊式DRAM存儲節點相關部分的結構分析

DRAM芯片的基本結構

DRAM芯片的基本結構

評論