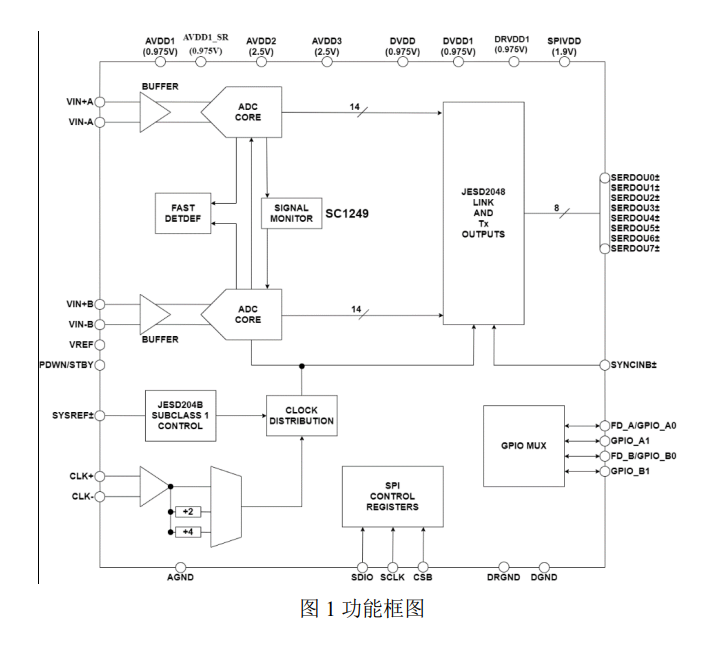

SC1249 是一款雙通道、14 位、3GSPS 模數(shù)轉(zhuǎn)換器ADC。該器件內(nèi)置片內(nèi)緩沖器和采樣保持 電路,專門針對(duì)低功耗、小尺寸和易用性而設(shè)計(jì)。該產(chǎn)品設(shè)計(jì)支持通信應(yīng)用,能夠?qū)崿F(xiàn)高達(dá) 5GH z 的寬帶寬模擬信號(hào)直接采樣。SC1249 在多方面進(jìn)行了優(yōu)化,其中包括寬輸入帶寬、高采樣速 率、出色的線性度以及小封裝低功耗。 這款雙通道 ADC 內(nèi)核采用多級(jí)、差分流水線架構(gòu),并集成了輸出糾錯(cuò)邏輯。每個(gè) ADC 均具 有寬帶寬輸入。集成基準(zhǔn)電壓源可簡(jiǎn)化設(shè)計(jì)考量。模擬輸入和時(shí)鐘信號(hào)均為差分輸入信號(hào)。 SC1249 利用 ADC 的寄存器(0x0245)中的快速檢測(cè)控制信號(hào),可編程閾值檢測(cè)器可以監(jiān)控輸 入信號(hào)功率。如果輸入信號(hào)電平超過(guò)可編程閾值,快速檢測(cè)指示器就會(huì)變?yōu)楦唠娖健S捎谠撻撝?指示器的延遲極短,因此用戶能夠快速調(diào)低系統(tǒng)增益,從而避免 ADC 輸入端出現(xiàn)超量程現(xiàn)象。除 了快速檢測(cè)輸出外,SC1249 還具有信號(hào)監(jiān)控能力。信號(hào)監(jiān)控模塊可提供 ADC 進(jìn)行數(shù)字化處理信 號(hào)的其它信息。 用戶可將 JESD204B(子類 1)的高速串行輸出設(shè)置為各種單通道、雙通道、四通道和八通道 配置,具體取決于接收邏輯器件的可接受通道速率。SYSREF±和 SYNCINB±輸入引腳支持多芯片 同步。 SC1249 具有靈活的關(guān)斷選項(xiàng),在需要時(shí)可以大幅降低功耗。所有這些特性均可通過(guò)三線串行 接口(SPI)進(jìn)行編程。 SC1249 采用 196 引腳 BGA 封裝,額定溫度范圍為?40°C 至+85°C。 產(chǎn)品特色 ? 支持約 5 GHz 的直接射頻(RF)信號(hào)采樣。 ? SPI 控制各種產(chǎn)品特性和功能,滿足特定系統(tǒng)要求。 ? 可編程的快速超范圍檢測(cè)和信號(hào)監(jiān)測(cè)。 ? 196 球 BGA 封裝(12mmx12mm) 無(wú)需散熱器

操作原理 SC1249 具有兩個(gè)模擬輸入通道和八個(gè) JESD204B 輸出通道對(duì)。 ADC 能接受的采樣帶寬最高達(dá) 5GHz。SC1249 有著寬輸入帶寬、高采樣率、出色的線性度 及小封裝和低功耗等特點(diǎn)。 雙 ADC 內(nèi)核采用多級(jí)差分流水線架構(gòu),帶有集成的輸出糾錯(cuò)邏輯。每個(gè) ADC 都具有寬帶寬 輸入,支持各種用戶可選擇的輸入范圍。集成電壓基準(zhǔn)簡(jiǎn)化了設(shè)計(jì)考慮。 SC1249具有多種功能,可簡(jiǎn)化通信接收器中的AGC功能。可編程閾值檢測(cè)器允許使用ADC 的快速檢測(cè)信號(hào)來(lái)監(jiān)控輸入信號(hào)功率。如果輸入信號(hào)電平超過(guò)可編程閾值,則快速檢測(cè)指示器變 高。由于該閾值指示器具有低延遲,因此用戶可以快速調(diào)低系統(tǒng)增益以避免 ADC 輸入出現(xiàn)超量 程情況。 基于 JESD204B(子類 1)的高速串行輸出數(shù)據(jù)通道可以配置為單通道 (L = 1)、雙通道 (L =2)、 四通道 (L =4) 和八通道 (L = 8) 配置,取決于采樣率和抽取率。通過(guò) SYSREF± 和 SYNCINB±輸 入引腳支持多器件同步。SC1249 中的 SYSREF±引腳還可用作數(shù)據(jù)通過(guò) ADC 并從 JESD204B 接 口輸出時(shí)的時(shí)鐘指示信號(hào)。 ADC 架構(gòu) SC1249 的由一個(gè)輸入緩沖流水線 ADC 組成。輸入緩沖器為模擬輸入信號(hào)提供端接阻抗。該 終端阻抗設(shè)置為 200Ω。輸入緩沖器針對(duì)高線性度、低噪聲和低功耗進(jìn)行了優(yōu)化。 模擬輸入注意事項(xiàng) SC1249 的模擬輸入是一個(gè)差分緩沖器。緩沖器的內(nèi)部共模電壓為 1.5V。時(shí)鐘信號(hào)在采樣模 式和保持模式之間交替切換輸入電路。 可以在輸入端放置一個(gè)差分電容或兩個(gè)單端電容(或兩者的組合)以提供匹配的無(wú)源網(wǎng)絡(luò)。 這些電容最終會(huì)形成一個(gè)低通濾波器,以限制不需要的寬帶噪聲。 通常,精確的前端網(wǎng)絡(luò)組件值取決于應(yīng)用程序。 差分輸入配置 有多種驅(qū)動(dòng) SC1249 的方法,可以是主動(dòng)的,也可以是被動(dòng)的。通過(guò)差分模擬輸入實(shí)現(xiàn)最佳 性能。 對(duì)于要求 SNR 和 SFDR 關(guān)鍵參數(shù)的應(yīng)用,推薦使用差分變壓器耦合作為輸入配置(見(jiàn)圖 30 和表 7),因?yàn)榇蠖鄶?shù)放大器的噪聲性能不足以實(shí)現(xiàn) SC1249 的真實(shí)性能。

審核編輯 黃宇

-

adc

+關(guān)注

關(guān)注

99文章

6533瀏覽量

545757 -

雷達(dá)

+關(guān)注

關(guān)注

50文章

2966瀏覽量

118022 -

GSPS

+關(guān)注

關(guān)注

0文章

48瀏覽量

16987

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ADC12DJ5200SE 10.4GSPS單通道或5.2GSPS雙通道12位射頻采樣模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC12DJ2700 5.4GSPS單通道或2.7GSPS雙通道12位射頻采樣模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC12DJ3200 6.4GSPS單通道或3.2GSPS雙通道12位射頻采樣模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC08DJ3200 6.4GSPS單通道或3.2GSPS雙通道8位射頻采樣模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

AD9208雙通道、14位、3 GSPS模數(shù)轉(zhuǎn)換器(ADC)英文手冊(cè)

ADC12DJ4000RF 8GSPS單通道或4GSPS雙通道、12位射頻采樣模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC12DL3200 6.4GSPS單通道或3.2GSPS雙通道12位模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC32RF5x雙通道14位2.6至3GSPS射頻采樣數(shù)據(jù)轉(zhuǎn)換器數(shù)據(jù)表

ADC34RF55四通道14位3GSPS射頻采樣數(shù)據(jù)轉(zhuǎn)換器數(shù)據(jù)表

ADC12DJ5200-SP 10.4GSPS單通道或5.2GSPS雙通道12位射頻采樣模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

雙通道3GSPS ADC SC1249替代ADI的AD9208用于測(cè)繪雷達(dá)

雙通道3GSPS ADC SC1249替代ADI的AD9208用于測(cè)繪雷達(dá)

評(píng)論