工程苗小兵

先楫資深FAE工程師

電力電子與電力傳動專業碩士研究生,一個從事了20多年的功率控制的工程小兵,有多年的電機驅動和電源控制經驗,專注電力電子控制方向。

簡 介

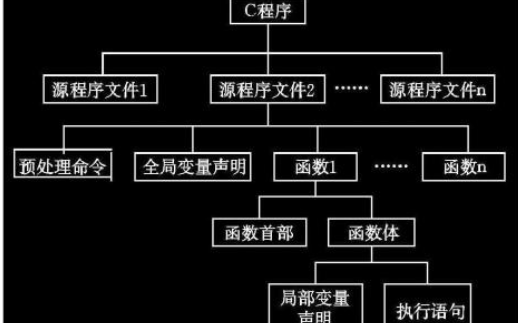

先楫半導體為客戶提供了480MHz - 1GHz的不同主頻高性能MCU,適用于不同高算力、實時控制要求的場合。在電機、電源應用場合,需要us級響應和運算,對響應時間的一致性、快速性都有非常高的要求。隨著MCU主頻提高,MCU的存儲方式和總線頻率也更加多樣化,先楫MCU中內部有ILM、DLM、AXI_SRAM、flash等多種存儲空間,但同時不同存儲需要的時鐘也不同,給軟件工程師設計帶來很大困擾。先楫在官網已經提供了優化DSP和FFT運算、使用片上SRAM等相關應用文檔。

本文重點簡述基于電機、電源應用的具體代碼優化方案。

經驗分享

1

ILM程序優化

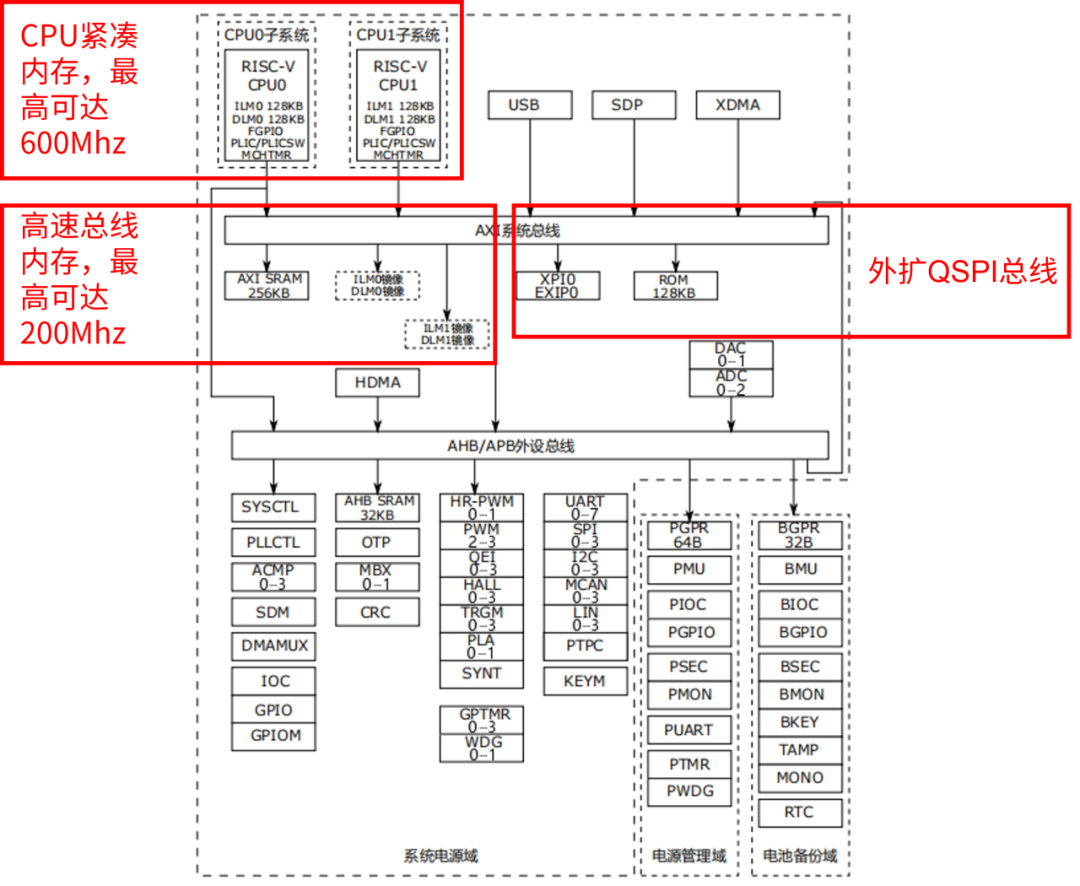

以下展示的是HPM6280的系統框圖

CPU內部包含了ILM、DLM、cache,這些內存都可達 600Mhz主頻。AXI總線上有AXI_SRAM和ILM_SLV、DLM_SLV,訪問頻率可達200MHz,總線寬度64bit,可以cache緩存。XPI接口為QSPI總線,最高頻率133Mhz,雙沿采樣,通常只有4bit寬度。其中AHB總線還有32kbyte SRAM,但主要用于外設存儲,這里不做贅述。

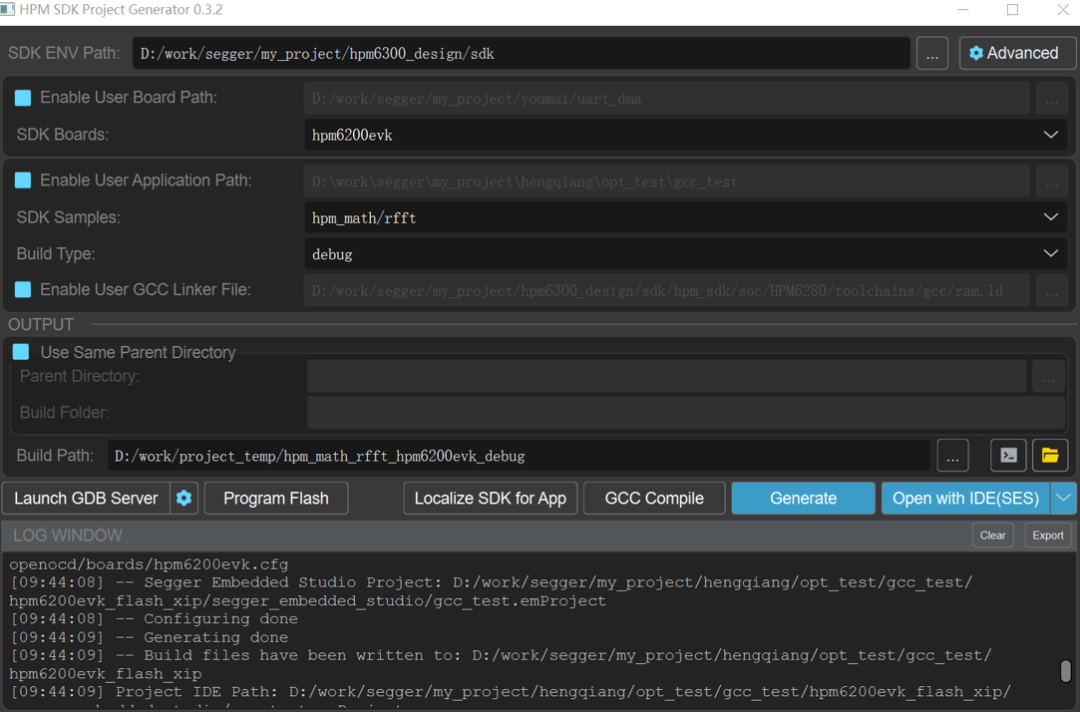

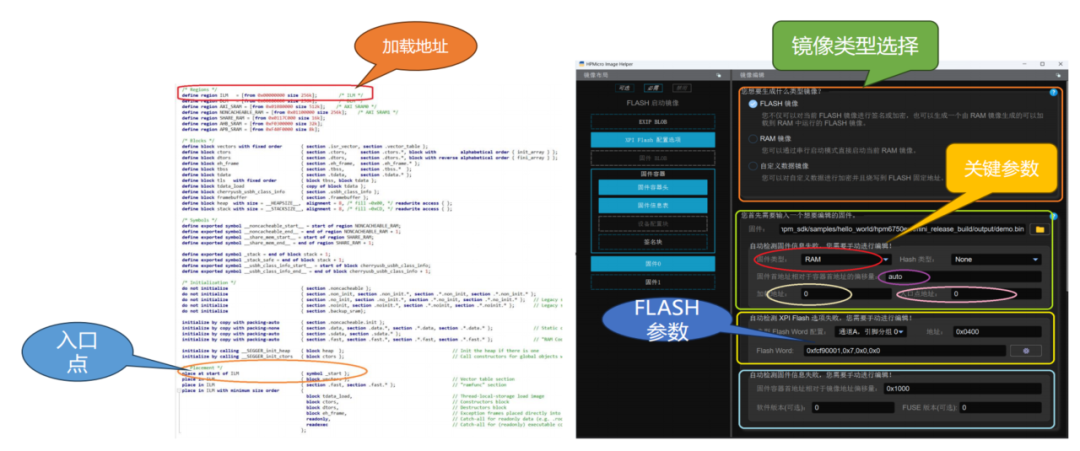

實際應用中程序都會放到flash中存儲,而XPI的接口速度極大限制了代碼執行效率。此外,由于XPI接口是可以cache緩存,導致XPI執行時cache命中和沒有命中的運行時間差別非常大,代碼一致性很差。為了方便客戶使用,可以生成工程時選用debug/release模式,指定程序在ILM中執行。隨后通過先楫manufacture tool可以實現鏡像功能,即生成在從FLASH 加載的RAM啟動鏡像。通過這種方式實現代碼完全在ILM中執行。

鏡像助手可將SDK中的debug/release 構建的應用轉化為FLASH啟動鏡像。

關鍵參數:

固件首地址相對容器首地址偏移

加載地址

入口點地址

2

SEGGER編譯優化在AXI_RAM執行

由于ILM空間限制,很多電源或電機復雜應用無法將程序全部放到ILM中執行,會導致因讀取存儲速度限制了CPU算力。

HPM6200、HPM6E00系列在AXI總線的大容量SRAM可以配置成程序存儲,其中HPM6260、HPM6E60還可以將CPU1的ILM、DLM配置到AXI總線上,基本滿足了絕大部分應用。AXI RAM主頻可達200Mhz,64bit位寬,有cache緩存,可以大大減少程序讀取對CPU性能的影響。

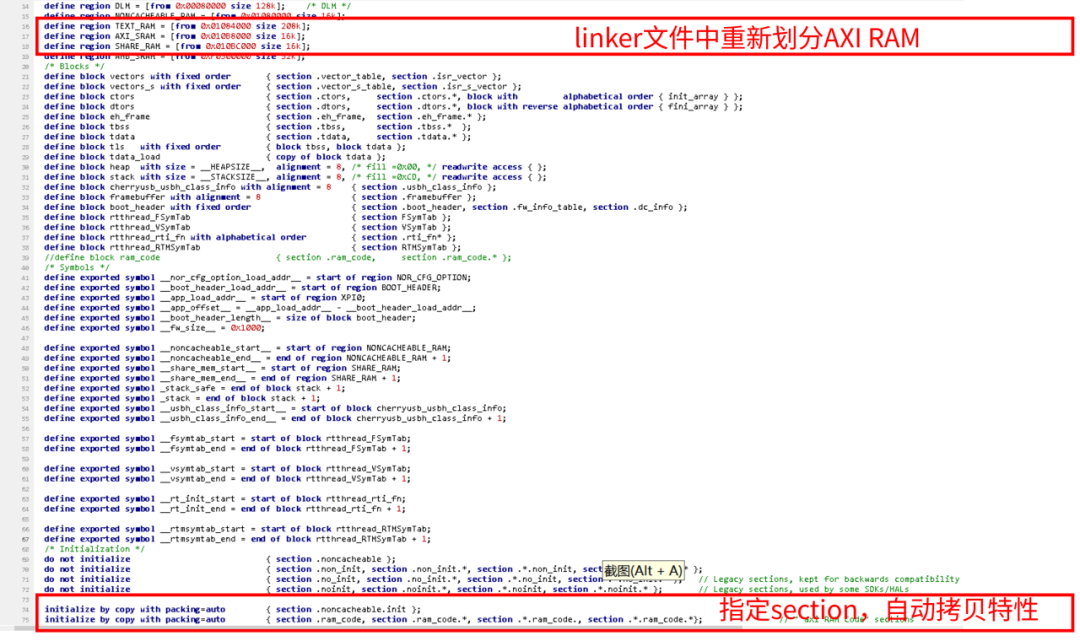

segger編譯器可以自動生成flash加載到RAM的拷貝代碼,只要在linker文件中配置相應特性,不需要額外修改flash拷貝代碼。

在linker文件中重新劃分AXI RAM,增加代碼區域。在軟件中指定代碼生成后存放區域。

通過SDK GUI直接指定修改后的linker文件,即可實現代碼在ILM+AXIRAM中執行。

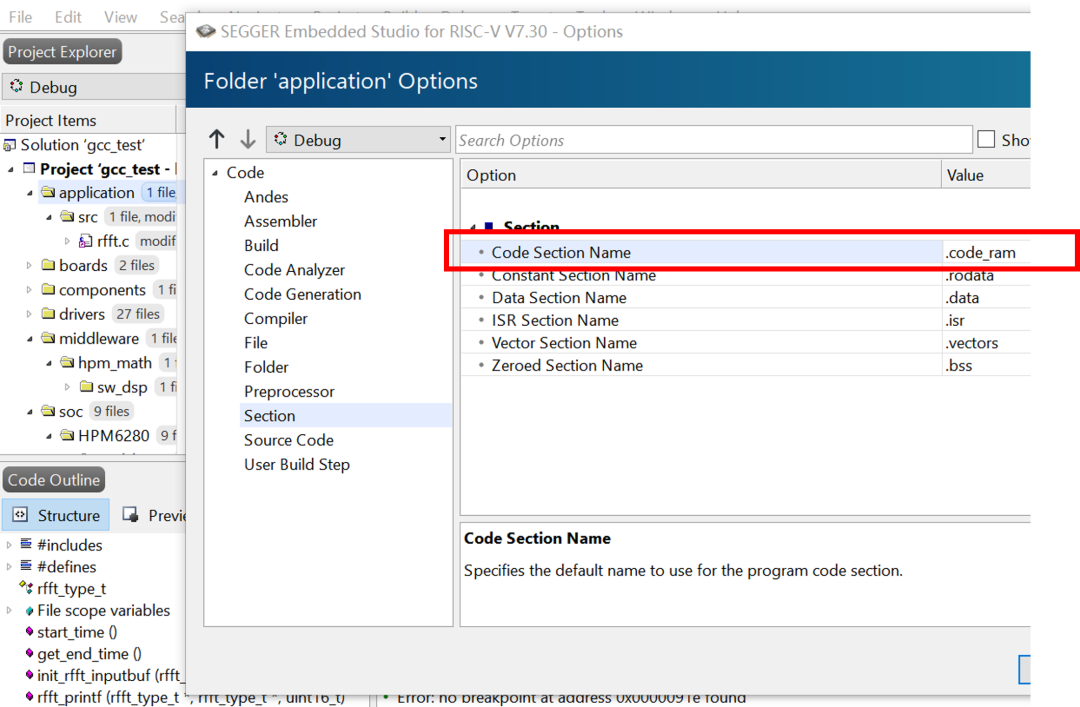

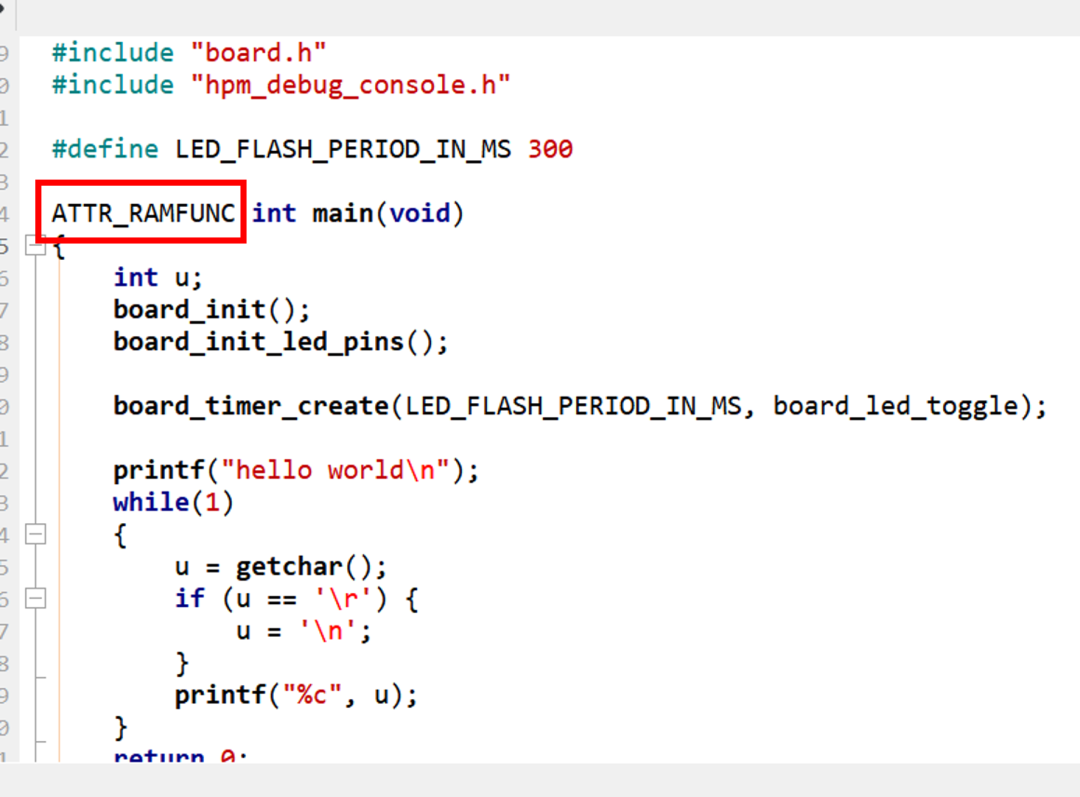

代碼指定區域可以通過SEEGER IDE批量指定文件或文件夾的程序放置區域,也可以在函數名前面增加函數宏定義。

3

GCC編譯優化在AXI_RAM執行

先楫產品支持Andes加速指令,可以加速三角函數、指數運算等復雜運行速度,但同時需要GCC編譯器支持。

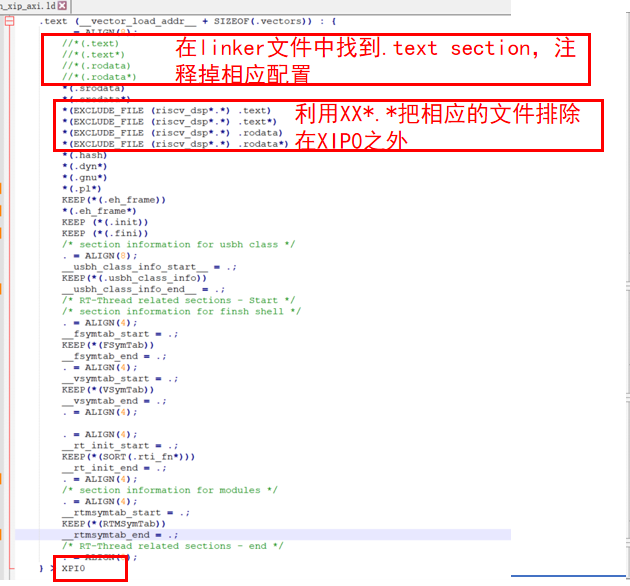

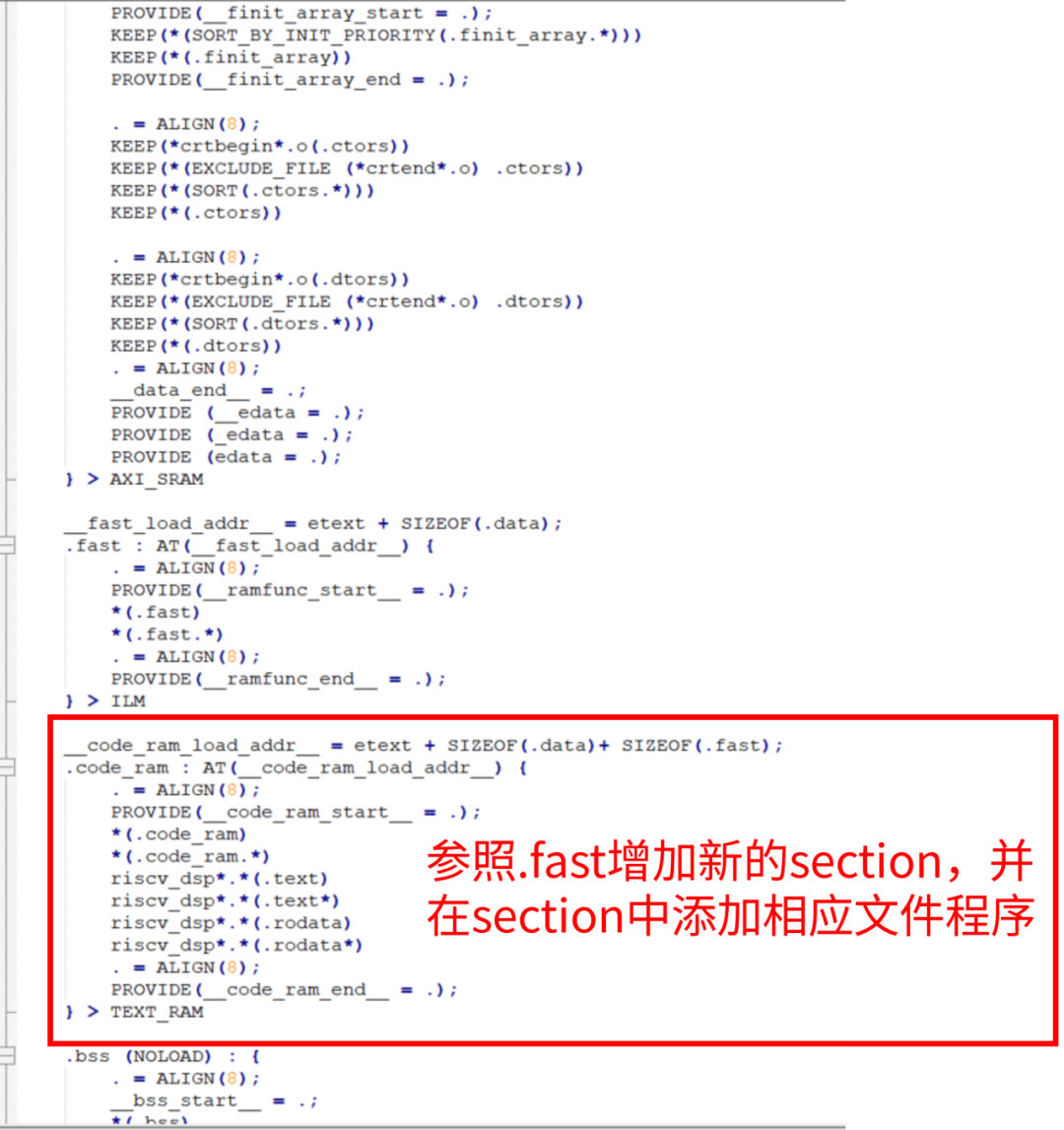

在linker文件中重新劃分AXI RAM,增加代碼區域。在軟件中指定代碼生成后存放區域。

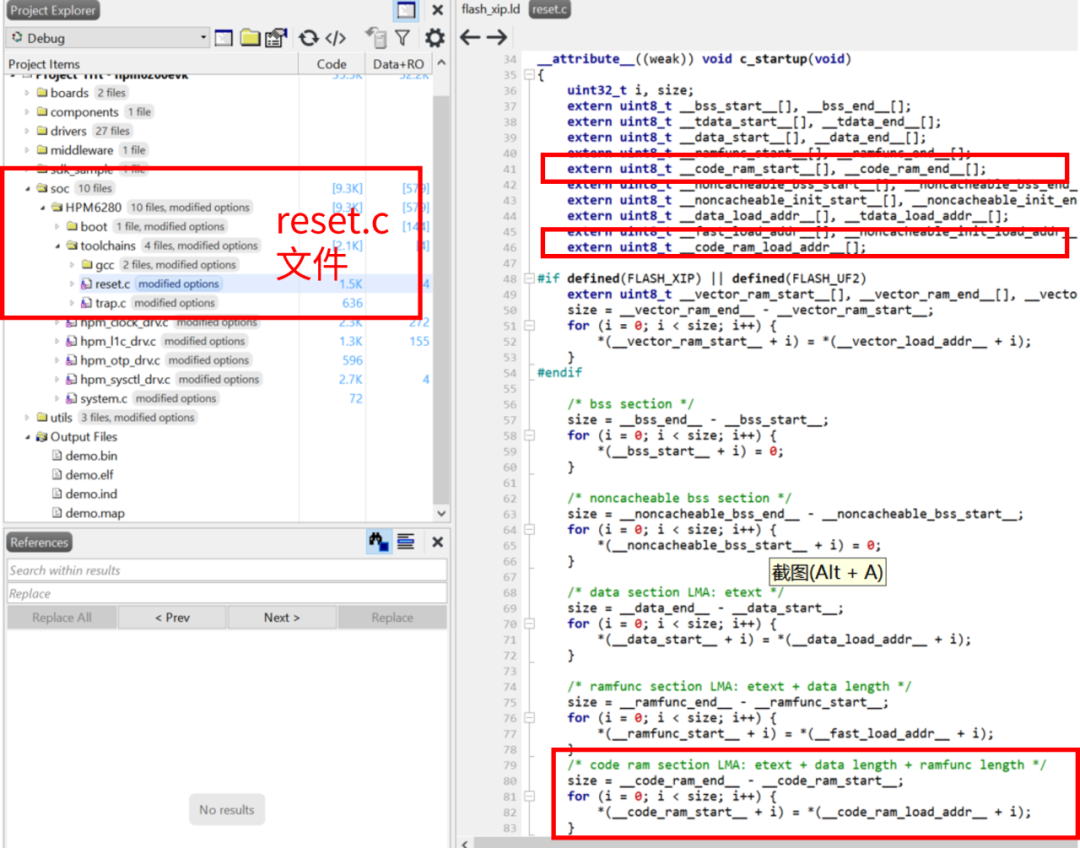

與segger編譯器不同,GCC編譯需要增加額外代碼實現flash加載到RAM的拷貝,需要修改相應的reset.c文件。

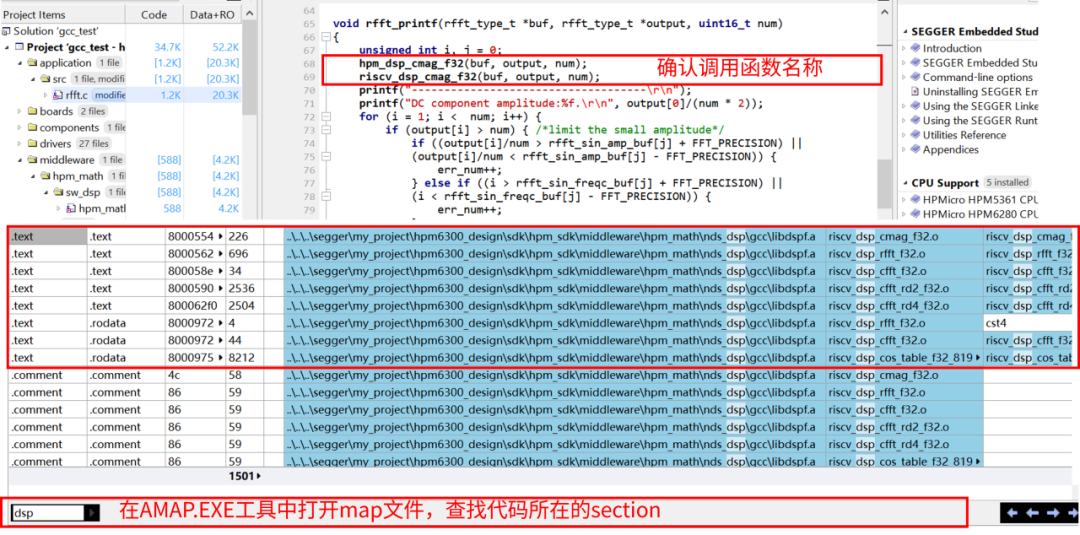

支持Andes加速指令需要引用hpm_math.h庫文件,會調用libdspf.a、libdspd.a、libdsp.a等封裝庫。由于封裝庫非明文代碼,無法通過常規方法指定代碼存放區域,導致調用該代碼時會因代碼放置在flash降低整體執行速度。需要在linker文件中額外配置響應代碼區域分配。

GCC編譯后無法像segger一樣編譯后通過圖形顯示生成代碼的占有率,且map文件閱讀性差。對gcc編譯的map文件需要引用AMAP.EXE工具。

GCC編譯需要增加額外代碼實現flash加載到RAM的拷貝,相應代碼位于 SOC/HPM6XXX/TOOLCHAINS/GCC/reset.c中。

在reset.c中函數c_startup實現flash到RAM程序的拷貝。

程序運行時,會以start.s開始,進入main函數之前先調用c_startup 函數完成程序搬移,在客戶的應用代碼中不會因程序放置位置不同而增加額外操作。

4

優化小知識

segger編譯器會將所有常數默認為定點數,即使該常數為小數,也需要在對應常數前加強制浮點轉換或者在常數后面加“f”做說明。

函數的inline定義在optimization level=0時是無效的,需要把優化等級設為1或更高。

建議將常用函數或變量通過attribute屬性定義到“.fast”和“.fast_ram”。

先楫MCU為多總線系統,當CPU讀寫外設時會有時鐘同步問題,建議在配置外設時盡量提高外設頻率,減少時鐘同步延遲。

HPM6260以及HPM6E60可以通過ILM_SLV、DLM_SLV接口可以將CPU1的內部存儲作為AXI_RAM使用。

-

mcu

+關注

關注

146文章

17317瀏覽量

352638 -

cpu

+關注

關注

68文章

10902瀏覽量

213005 -

程序優化設計

+關注

關注

0文章

3瀏覽量

1203

發布評論請先 登錄

相關推薦

關于uCos實時性的疑惑

SHT30程序可移植性不強的問題怎么優化

Zephyr與FreeRTOS實時性測試比較

嵌入式實時程序設計中C/C++代碼的優化

基于RTSJ的實時嵌入式系統API的優化研究

車輛工程基于某MATLAB地動力性仿真分析報告及優化設計程序

xenomai實時性的影響因素及優化措施

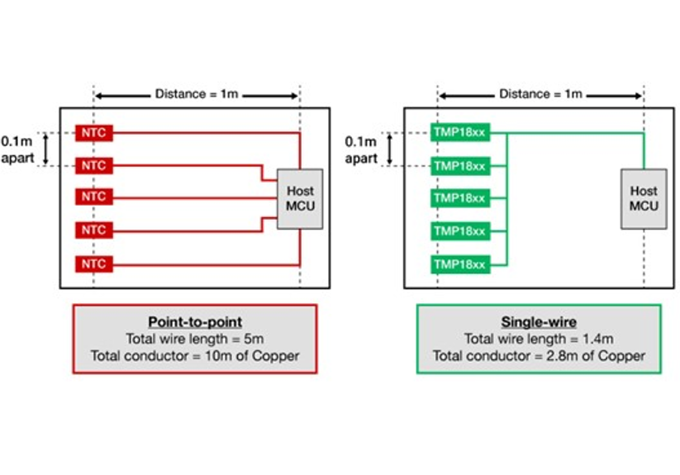

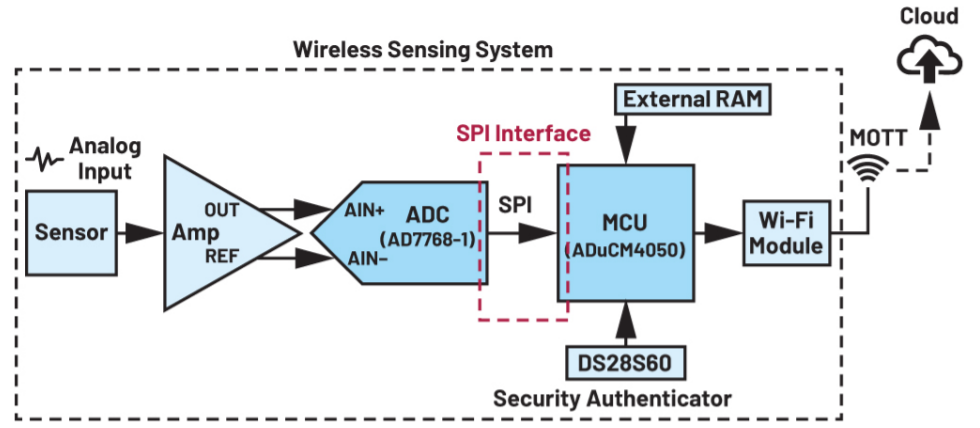

在實時控制系統中使用傳感器優化數據可靠性的3個技巧

在實時控制系統中使用傳感器優化數據可靠性的3個技巧

高實時性程序優化設計

高實時性程序優化設計

評論