電子發燒友網報道(文/李寧遠)人工智能、機器學習、大數據是現在蓬勃發展的領域,這些技術的飛速發展拉動了對高性能計算和存儲的需求。在這些背景下,憶阻器獨特的性能展現出其廣泛的應用前景。

憶阻器的全稱是記憶電阻器,是一種表示磁通和電荷關系的電路元件。通過測定憶阻的阻值,可知道流經它的電荷量,從而有記憶電荷的作用。憶阻器可以組成類似矩陣的結構,既可以存數據,也可以做計算,數據不再需要搬來搬去,可以大大降低存算所帶來的消耗。

憶阻器為計算帶來新未來

我們可以簡單地把憶阻器理解成一種具有記憶功能的非線性電阻,通過控制電流的變化可改變其阻值,記憶電荷的特性可以利用來實現存儲數據的功能。這種器件最早在1971年被推斷出應該在自然界中存在,后續被證實。記憶電阻器也被認為是繼電阻、電容、電感之后的第四種電路基本元件。

高性能、高密度的計算是與存儲系統密切相關的,處理器和內存之間的性能差距是制約計算能力的一大瓶頸。在目前所有各類存儲器件中,憶阻器是一種非常適合存算一體應用的器件,其非易失性、多電導水平、低能耗、快速切換、可擴展性以及適用于神經形態計算的特點,都很契合現在的需要。

當然,目前的憶阻器件仍舊存在成品率低和性能不可靠的問題,不過憶阻器的技術進步沒有停止。去年TetraMem實現了將數千個導電水平的憶阻器集成在CMOS上,突破性的在CMOS技術上成功實現了高密度、多水平的憶阻器集成。

該成果在完全集成芯片中實現了2048個可區分的電導等級,能夠為存儲和計算任務提供更高的性能和能效,將憶阻器的落地推進了一大步。

清華大學也曾官宣了在支持片上學習的憶阻器存算一體芯片領域取得重大突破,研制出了全球首顆全系統集成的、支持高效片上學習的憶阻器存算一體芯片。測試結果顯示,該芯片包含支持完整片上學習所必需的全部電路模塊,在多個任務中,該芯片的能耗僅為先進工藝下ASIC系統的3%,能效指數級提升。

今年安徽大學集成電路學院提出了一種基于具有可調節衰減時間核的LiCoO2動態憶阻器的硬件神經元,實現了具有低功耗、高能效計算的輕量級脈沖神經網絡模型的語音識別硬件系統。

憶阻器的技術突破,讓市場看到了低功耗、高能效計算行之有效的解決方案,雖然還需要時間沉淀,當時憶阻器的確為未來的計算打開了大門。

從傳統憶阻器到自旋憶阻器

憶阻器的具體分類其實是很多的,現在市面上采用較多的是采用ReRAM抵抗變化型和PCM相變型這些憶阻器元件。尤其是ReRAM,基于ReRAM設計的存算一體技術路線已經得到了很多廠商的認同。

但其實這類元件作憶阻器時,響應性能實現起來較為復雜,并且難以控制器件電阻值會隨時間漂移的問題,需要復雜的電路或算法補償來彌補這些缺陷。因此也不是完美無缺的憶阻器方案。

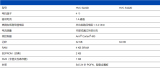

為此TDK正在推進基于自旋憶阻器的人工智能技術,根據TDK的介紹,自旋憶阻器基于最新磁阻效應原理,結合了HDD磁頭和磁性傳感器的設計,可以自由移動上下磁化的磁邊界,電阻值隨磁邊界位置變化,寫入操作通過橫向電流實現,讀取操作通過縱向電流實現,能夠兼具磁體的數據保持性和可控性。

該技術一是為了改進不利于實時學習的傳統憶阻器復雜補償,二是為了改進漂移帶來的AI性能不穩定。自旋憶阻器不需要復雜的補償就能實現電導率的精確控制,電阻的一致性也不會對AI性能帶來負面影響。根據TDK給出的預期,該器件未來可幫助芯片大幅降低功耗,并同時實現AI的學習功能和推理功能。

小結

自被發現開始,憶阻器的研究就沒有中斷過,其自動記憶能力和狀態轉換特性,在不斷的技術突破下將大力推動人工智能和模擬存儲的發展。

-

憶阻器

+關注

關注

8文章

73瀏覽量

19946

發布評論請先 登錄

相關推薦

憶芯科技榮獲長城科技“卓越服務獎”

憶聯榮獲2024年度閃存控制器金獎

導熱界面材料對降低接觸熱阻的影響分析

憶阻器誘導的超混沌、多渦旋和極端多穩態小數階HNN:鏡像加密和FPGA實現

本田聯手IBM創新研發下一代計算技術,專為無人駕駛和高級駕駛輔助系統

進一步解讀英偉達 Blackwell 架構、NVlink及GB200 超級芯片

小數據低能耗AI:智慧AI時代的開啟

TDK進一步擴充Micronas嵌入式電機控制器系列HVC 5x

憶阻器通向計算新未來,自旋憶阻器進一步降低能耗

憶阻器通向計算新未來,自旋憶阻器進一步降低能耗

評論