近期,臺積電將其高性能計算與 AI 芯片封裝技術亮相于國際固態電路大會(簡稱 ISSCC 2024),據悉,此技術有望將芯片晶體管數目由現有的1000億級躍升至1萬億級。

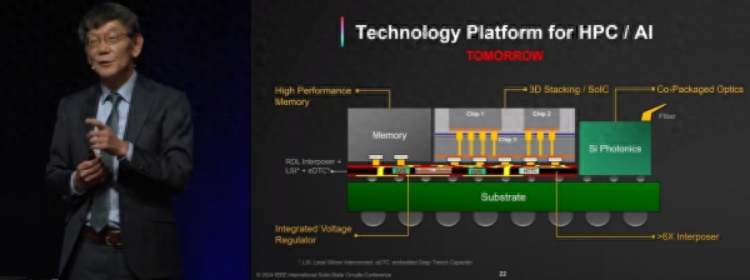

臺積電高級研發副總裁張曉強指出,本項新技術主要針對AI芯片性能增強。新型HBM高帶寬存儲器與Chiplet架構小芯片的引入需求大量組件及IC基板,由此引發的連通性及能源消耗等問題難免產生。他特別強調,借助硅光科技與光纖替代傳統I/O電路,實現高效率的數據傳輸;此外,通過異質芯片堆疊和混合鍵合,最大限度優化I/O。值得注意的是,這項封裝技術將運用集成穩壓器應對供電問題,但具體商用時間尚未透露。

臺積電透露,當前全球前沿芯片最多可容納1000億晶體管,然而新的封裝平臺能使之增加到1萬億級別。盡管該封裝內將搭載集成穩壓器解決供電問題,但未來商業化仍待進一步確認。此外,張曉強還暗示臺積電的3nm制程技術很可能迅速應用于汽車領域。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

存儲器

+關注

關注

38文章

7528瀏覽量

164347 -

AI芯片

+關注

關注

17文章

1906瀏覽量

35217 -

chiplet

+關注

關注

6文章

434瀏覽量

12632

發布評論請先 登錄

相關推薦

臺積電超大版CoWoS封裝技術:重塑高性能計算與AI芯片架構

一、技術前沿探索:從微小到宏大的CoWoS封裝技術演進 在半導體技術的浩瀚星空中,每一次技術的革新都如同星辰般璀璨奪目。去年臺積電在歐洲開放創新平臺

臺積電分享 2nm 工藝深入細節:功耗降低 35% 或性能提升15%!

下),同時其晶體管密度是上一代3nm制程的1.15倍。這些顯著優勢主要得益于臺積電的全柵極(Gate-All-Around, GAA)納米片

臺積電推出“超大版”CoWoS封裝,達9個掩模尺寸

圓上芯片)封裝技術,該技術將提供高達9個掩模尺寸的中介層尺寸和12個HBM4內存堆棧。新的封裝方法將解決性能要求最高的應用,并讓AI(人工智

臺積電CoWoS產能將提升4倍

在近日于臺灣舉行的SEMICON Taiwan 2024國際半導體展會上,臺積電展示了其在先進封裝技術領域的雄心壯志。據

臺積電跨制程整合晶體管架構并引入CFET,發布新一代芯片技術

張曉強強調,半導體產業的黃金時代已然來臨,未來AI芯片的發展幾乎99%都依賴于臺積電的先進邏輯技術和先進

臺積電總裁缺席技術論壇,看好AI和高性能計算前景

臺積電2024年技術論壇于5月23日在中國臺灣舉行,但由于總裁魏哲家缺席,由亞太業務處長萬睿洋代為發言。他表示,人工智能(AI)正引領第四次

世界第一AI芯片發布!世界紀錄直接翻倍 晶體管達4萬億個

和相同的價格下,WSE-3的性能是之前的世界記錄保持者Cerebras WSE-2的兩倍。 該公司稱,WSE-3芯片是專為訓練業界最大的AI模型而構建的,臺

臺積電推新封裝平臺,提升高性能計算與人工智能芯片互聯與性能

臺積電業務開發高級副總裁張曉強在會議發言中指出該項技術主要致力于提升AI加速器性能。隨著HBM高帶寬存儲

臺積電創新推出萬億晶體管封裝平臺,專注于高性能計算和AI芯片應用

臺積電創新推出萬億晶體管封裝平臺,專注于高性能計算和AI芯片應用

評論