電源的作用是為系統提供穩定的電壓及電流。電源完整性問題是指電源的電壓、紋波及噪聲不滿足系統的工作要求,通過合理的電源供電網絡設計可以減小電源塌陷等電源完整性問題,提高系統的穩定性。

1.電源分配網絡

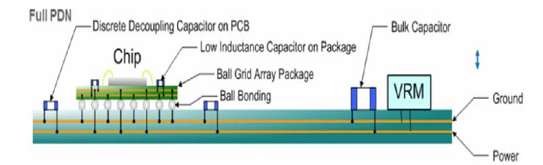

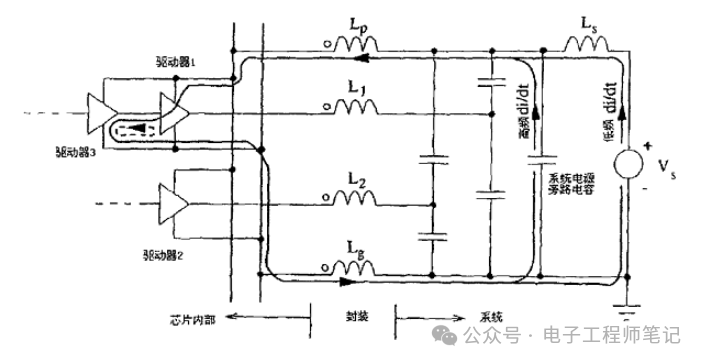

電流從供電模塊輸出,流經PCB板、芯片封裝,最終到達負載芯片給其供電的完整供電路徑稱之為電源分配網絡(PDN),除此之外,它還包含有大量PCB板及芯片封裝上的去耦電容。即電源分配網絡是電流所經過的所有結構和器件組成的系統,如下圖所示。

在上圖所示的電源分配網絡中,電流從電源模塊(VRM)輸出后經PCB板上的走線、過孔等結構,通過BGA焊球到達芯片封裝,然后經過芯片封裝上的走線,進入到封裝內部的Die上,給芯片進行供電,其路徑中還包括電阻、去耦電容、電感等無源器件。走線、過孔、電阻和去耦電容等都會給電源供電網絡帶來寄生電感、寄生電容和寄生電阻的影響,導致電源供電網絡并不是理想的供電網絡。另外,芯片內部的開關速度變得越來越高,供電電壓變得越來越低,其對電源配送網絡的設計提出了更高的要求。

2.同步開關噪聲

在高速數字電路中,當數字集成電路加電工作時,它內部的門電路輸出會發生從高到低或者從低到高的狀態轉換,這時會產生一個瞬間變化的電流△i,這個電流在流經回流路徑上存在的電感時會形成交流壓降,從而引起噪聲,當同時發生狀態轉換的輸出緩沖器較多時,這個壓降將足夠大,從而導致電源完整性問題,我們將這種噪聲稱為同步開關噪聲(SSN),也叫△i 噪聲。

同步開關噪聲主要是伴隨著器件的同步開關輸出(Simultaneous Switch Output,SSO)而產生,開關速度越快,瞬間電流變化越顯著,電流回路上的電感越大,則產生的SSN越嚴重。基本公式為:VSSN=NLLoop(di/dt),其中N是同時開關的驅動器的數目,LLoop為整個回流路徑上的電感,i是每個驅動端的電流,而VSSN就是同步開關噪聲的大小。這個公式看起來簡單,但真正分析起來卻不是那么容易,因為不但需要對電路進行合理的建模,還要判斷各種可能的回流路徑,以及分析不同的工作狀態。

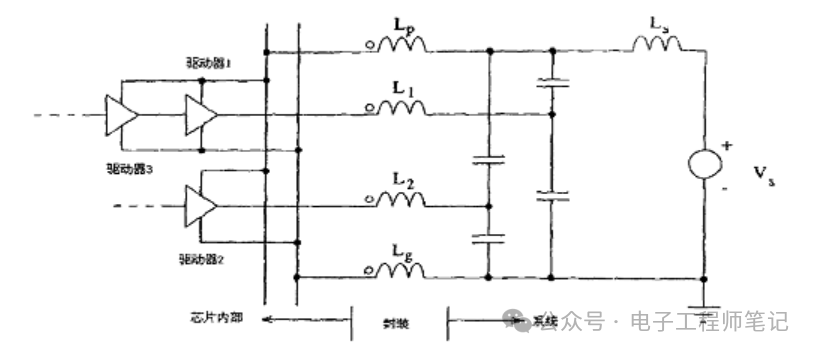

同步開關噪聲的產生可以通過下圖所示的原理圖來解釋,其中,封裝模型包括自身的電感和封裝之間的互電感(互電感沒有在圖中標出),由于電阻對開關噪聲的影響很小,為了簡化討論,這里忽略其影響,系統的接收器用電容表示。

我們可以將同步開關噪聲分為兩種:芯片內部(on-chip)開關噪聲和芯片外部(off-chip)開關噪聲。當驅動器3開關輸出,驅動器1作為接收端時,產生的噪聲稱為芯片內部開關噪聲;當驅動器1或驅動器2開關輸出,將信號傳輸到系統的接收器時,產生的噪聲稱為芯片外部開關噪聲。兩種情況下封裝電感的影響各不相同。

2.1芯片內部開關噪聲

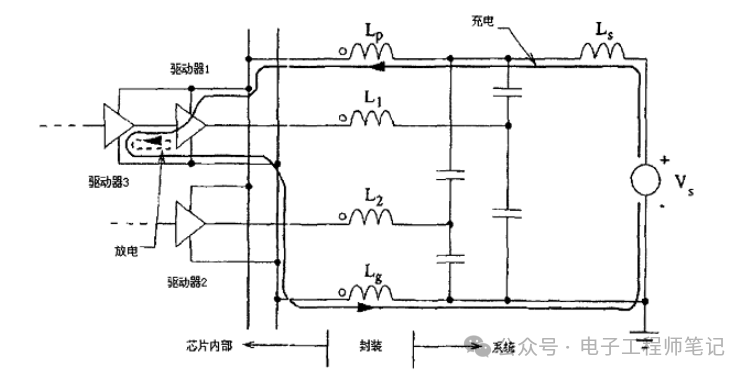

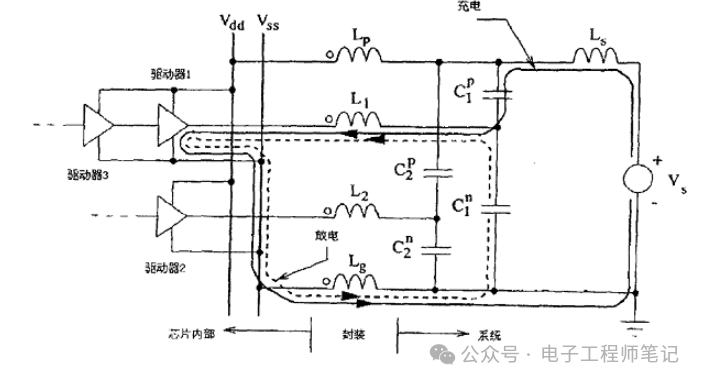

在上圖中,當驅動器3跳變時,它必須對驅動器1的輸入電容進行充放電。驅動器3由高電平到低電平轉換時的電流路徑如下圖所示,驅動器3對驅動器1下方的電容進行放電,放電回路如虛線所示,電流完全在芯片內部,不會產生互連噪聲;同時對驅動器1上方的電容充電,充電回路如實線所示。驅動器3出低到高轉換時,驅動器主上方的電容被放電,同時下方的電容被充電,電流路徑不變。

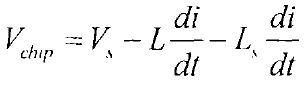

上圖中,充電電流流經了封裝中電源引腳電感Lp和地引腳電感Lg,而沒有流經信號線電感L1和L2。由于Lp和Lg上通過的電流是反向的,所以封裝總電感為:L=Lp+Lg-2Mpg,其中Mpg指Lp和Lg之間的互感。由于封裝電感L和系統電源電感Ls上產生壓降,則芯片實際得到的電源電壓為:

因而,在開關的瞬間,加在芯片上的電源電壓會下降,隨后圍繞Vs呈現阻尼振蕩。

要將供電下降限制到最小,需要通過減小電感或者電流變化速率來減小感應噪聲,通常可以采取的措施有:

⑴降低芯片內部驅動器的開關速率以減小di/di,但是當需要獲得很高的時鐘頻率時,這種方法不可取。

(2)使用電源平面和地平面,并讓電源平面和地平面盡量接近以獲得最小的系統電源供電電感Ls。

(3)增加電源/地的管腳數目,縮短電源/地的管腳引線長度,以降低芯片封裝中的電源和地路徑的電感。

(4)電源和地管腳應成對分布并盡量靠近放置,以增加封裝中電源和地路徑的互感,從而減小封裝總電感。

(5)給系統電源增加旁路電容,在此情況下驅動器3由高電平到低電平轉換時的電流路徑如下圖所示,旁路電容可以給高頻的瞬變交流信號提供低阻抗的旁路,而變化較慢的信號仍然走系統電源回路,因此產生的噪聲電壓變小。

(6)在芯片封裝內部使用旁路電容,這樣高頻電流的回路電感會非常小,能在很大程度上減小芯片內部的同步開關噪聲。

2.2芯片外部開關噪聲

驅動器1出高電平到低電平轉換時的電流路徑如下圖所示,驅動器1對進行放電,放電回路如虛線所示,同時對進行充電,充電回路如實線所示,充、放電電流都是從封裝的地引腳流出,從信號線流回,不經過電源引腳;反之,驅動器1由低電平到高電平轉換時,充、放電電流都是從信號線流出,從封裝的電源引腳流回,不經過地引腳。

上圖中,不考慮系統電源電感Ls,僅封裝電感造成的電壓降為:

所以,這時芯片地和系統地并不是保持同樣的零電位,而是存在Vgb的電壓波動,這種情況我們稱之為地彈(Ground Bounce)。同樣,低電平到高電平轉換時,由于感應電壓的影響,芯片內電源電壓將低于系統電源電壓,我們稱之為電源反彈。

要減小地彈,可采取以下幾種方法:

(1)降低驅動器的邊沿速率,滿足時序要求的最慢邊沿速率將產生最小的噪聲。

(2)減小封裝回路電感,即減小自感或者增大互感。

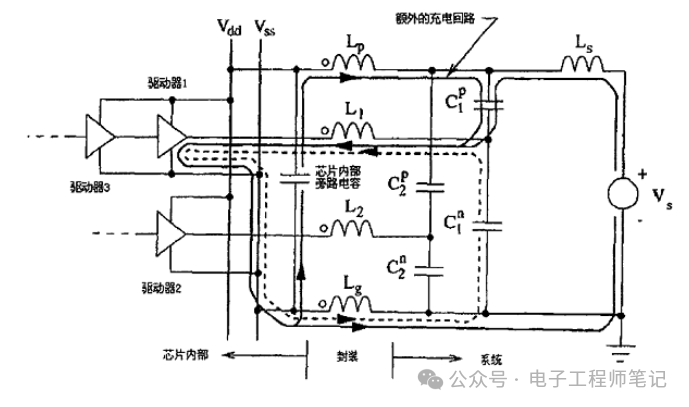

(3)在芯片封裝內部使用旁路電容,在這種情況下驅動器1從高電平到低平轉換時的電流路徑如下圖所示,增加了額外的充電回路,封裝的電源引腳和地引腳共同分擔充電電流回路,從而減小電壓波動。

對于電源反彈,可以采用類似的分析方法和抑制措施。

審核編輯:劉清

-

PCB板

+關注

關注

27文章

1449瀏覽量

51952 -

緩沖器

+關注

關注

6文章

1930瀏覽量

45639 -

BGA

+關注

關注

5文章

549瀏覽量

47045 -

去耦電容

+關注

關注

11文章

316瀏覽量

22472 -

電源完整性

+關注

關注

9文章

211瀏覽量

20775

原文標題:電源完整性分析

文章出處:【微信號:電子工程師筆記,微信公眾號:電子工程師筆記】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

信號完整性與電源完整性的仿真分析與設計

電源完整性分析

電源完整性設計分析

電源完整性問題是指什么?電源完整性分析

電源完整性問題是指什么?電源完整性分析

評論