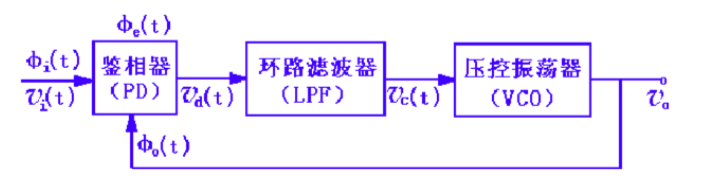

所謂鎖相環路,實際是指自動相位控制電路〔APC) ,它是利用兩個電信號的相位誤差,通過環路自身調整作用,實現頻率準確跟蹤的系統,稱該系統為鎖相環路,簡稱環路,通常用PLL表示。

鎖相環路是由鑒相器《簡稱PD》、還路濾波器〔(簡稱LPF或LE和壓控振蕩器(簡稱VCO〕三個部件組成閉合系統。這是一個基本環路,其各種形式均由它變化而來。

鎖相環鎖定時間取決于哪些因素

鎖相環(PLL)鎖定時間取決于多個因素。以下是一些主要因素:

1. 參考信號頻率穩定度:參考信號的頻率穩定度越高,PLL鎖定時間就越短。如果參考信號頻率出現較大的漂移或噪聲,PLL需要更長的時間來穩定。

2. 目標頻率與參考頻率之間的差異:如果目標頻率與參考頻率之間的差異較小,PLL可以更快地鎖定。當兩者之間的差異較大時,PLL需要更長的時間來捕捉到目標頻率。

3. 系統的帶寬:PLL的帶寬決定了系統對頻率變化的響應速度。較高的帶寬可以加快鎖定時間,但可能會引入噪聲和干擾。

4. 系統的阻尼系數:阻尼系數是衡量PLL響應速度和穩定性之間的折中因素。較高的阻尼系數可以增加穩定性,但可能會減慢鎖定時間。

5. 可用的控制電壓或電流:PLL中的控制電壓或電流的范圍和精度也會影響鎖定時間。更大的控制范圍可以更快地調整頻率,更高的控制精度可以提供更好的鎖定性能。

鎖相環鎖定狀態和失鎖狀態的特點是什么

鎖相環(PLL)有兩種主要狀態:鎖定狀態和失鎖狀態。它們具有不同的特點:

1. 鎖定狀態:

- 頻率同步:當PLL處于鎖定狀態時,輸出信號的頻率與參考信號的頻率是相等的,即它們保持同步。

- 相位同步:鎖定狀態還意味著輸出信號相位與參考信號相位具有固定的相對關系。

- 濾波效應:在鎖定狀態下,PLL的濾波器將對輸入信號進行濾波,以減小噪聲和干擾的影響。

- 穩定性:一旦PLL鎖定,它能夠保持較高的頻率和相位穩定性。

2. 失鎖狀態:

- 頻率偏差:失鎖狀態下,輸出信號的頻率與參考信號的頻率之間存在偏差,即它們不再同步。

- 相位偏差:失鎖狀態下,輸出信號的相位與參考信號的相位之間存在不確定的相對關系。

- 不穩定性:失鎖狀態下,輸出信號的頻率和相位可能會受到噪聲、干擾和其他外部因素的影響,從而產生不穩定的變化。

失鎖狀態通常是由于以下情況之一引起的:

- 環路濾波器參數不正確或環路帶寬設置不合適。

- 參考信號頻率發生了較大的漂移或噪聲。

- 環路中的噪聲或干擾過大,超過了PLL的穩定范圍。

- PLL輸入信號存在較大的干擾或失真。

特定PLL系統的鎖定狀態和失鎖狀態可能會有一些變化。在實際應用中,根據要求進行調整和優化以實現所需的性能和穩定性。

審核編輯:黃飛

-

鎖相環

+關注

關注

35文章

590瀏覽量

87897 -

濾波器

+關注

關注

161文章

7862瀏覽量

178936 -

pll

+關注

關注

6文章

781瀏覽量

135333 -

壓控振蕩器

+關注

關注

10文章

134瀏覽量

29370 -

控制電壓

+關注

關注

0文章

36瀏覽量

16146

發布評論請先 登錄

相關推薦

電荷泵鎖相環電路鎖定檢測的基本原理,影響鎖相環數字鎖定電路的關鍵因子是什么?

高頻鎖相環的可測性設計,不看肯定后悔

一種實現快速鎖定的鎖相環的研究

鎖相環驗證通行及鎖定的建立

詳解FPGA數字鎖相環平臺

利用開關的控制加速鎖相環鎖定的設計方法

鎖相環鎖定時間取決于哪些因素

鎖相環鎖定時間取決于哪些因素

評論