1. PCB疊層結(jié)構(gòu)與阻抗計算

1.1. Core 和 PP

PCB由Core和Prepreg(半固化片)組成。

Core是覆銅板(通常是FR4—玻璃纖維&環(huán)氧基樹脂),Core的上下表面之間填充的是固態(tài)材料;

常見半固化片類型:106,1080,2313,3313,2116,7628

PP原始厚度:7628(0.185mm/7.4mil),2116(0.105mm/4.2mil),1080(0.075mm/3mil), 3313(0.095mm/4mil )

實際壓制完成后厚度:通常會比原始值小10-15um左右

常用銅厚:1/3oz、1/2oz、1oz、2oz

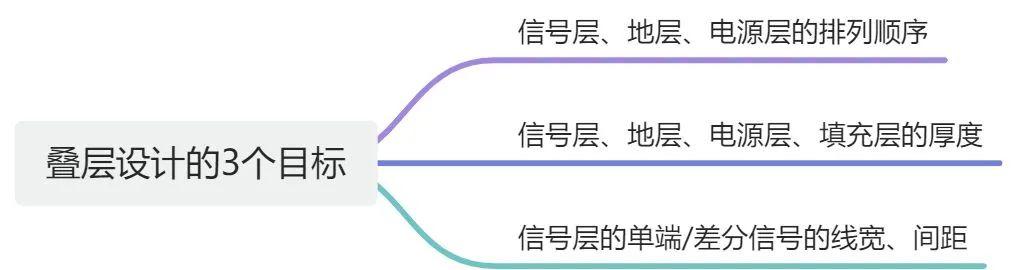

1.2. PCB的疊層機構(gòu)和阻抗設(shè)計

1.2.1. 層疊結(jié)構(gòu)設(shè)計的先決條件

1.2.2. 層疊結(jié)構(gòu)與阻抗設(shè)計的流程

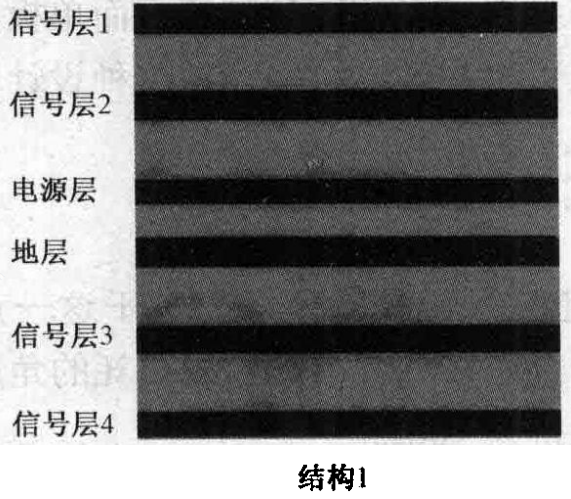

a. 對結(jié)構(gòu)1的分析

電源層與地層相鄰,且距離較近,可以很好地實現(xiàn)電源與地之間的耦合。

信號層3與地層相鄰,以完整的地層作為參考平面,因此信號完整性最好。

信號層2與電源層相鄰,若電源層是完整的平面,則同樣也能獲得較好的信號完整性,但若電源種類不止一種,則電源層需分塊,不完整的參考平面會導(dǎo)致信號回流路徑不通暢,對信號完整性存在一定影響。

信號層1,4與信號層2,3相鄰,很容易受到相鄰信號層的影響,因此完整性最差。

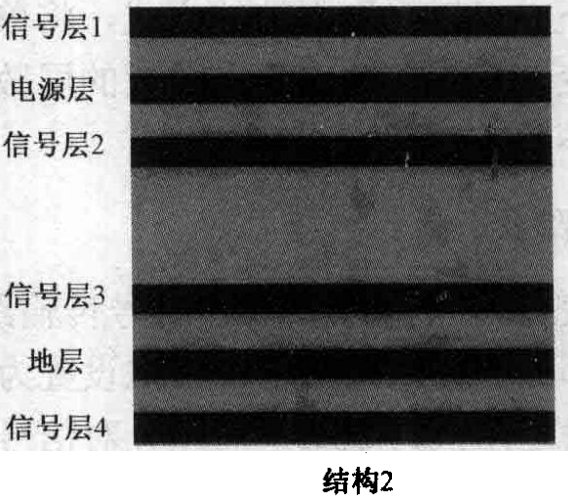

b. 對結(jié)構(gòu)2的分析

電源層與地層不相鄰,耦合較差,無法形成有效的寄生小電容。

信號層1,2,3,4相鄰層都能找到地層或電源層作為參考平面,信號質(zhì)量相對結(jié)構(gòu)1更好一些,其中,信號層1和4位于表層,而表層的阻抗控制比內(nèi)層更難。因此,從信號完整性而言,信號層2和3要好于1和4。

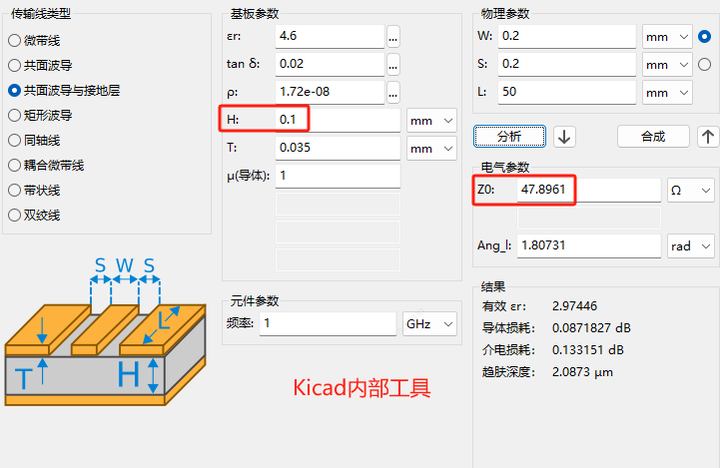

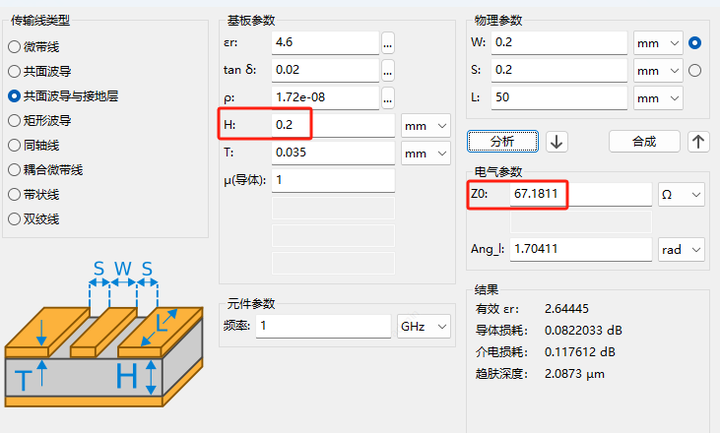

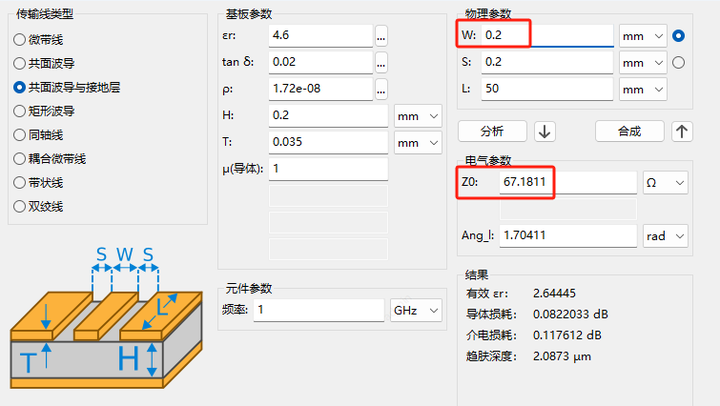

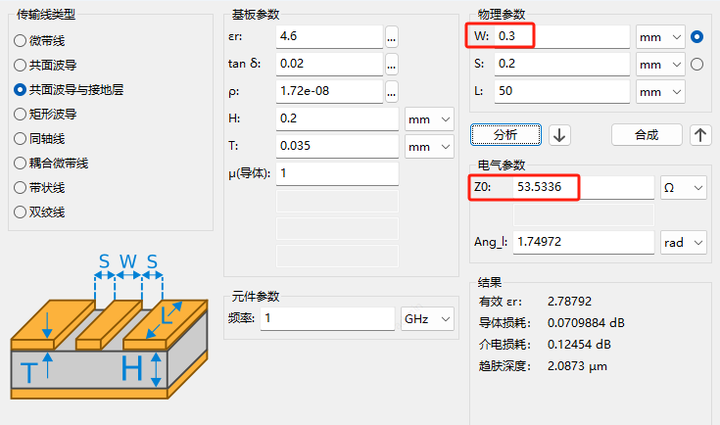

(2)線寬與層厚

a. 改變參考層厚度0.1mm為0.2mm,阻抗從47Ω增加到67Ω

b. 改變線寬0.2mm為0.3mm,阻抗從67Ω增加到53Ω

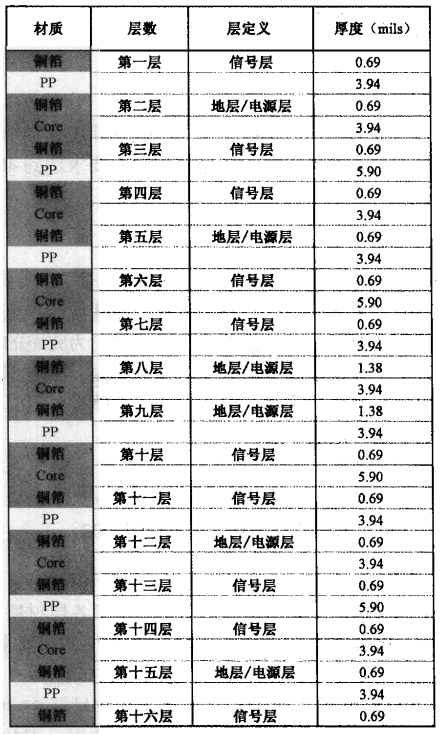

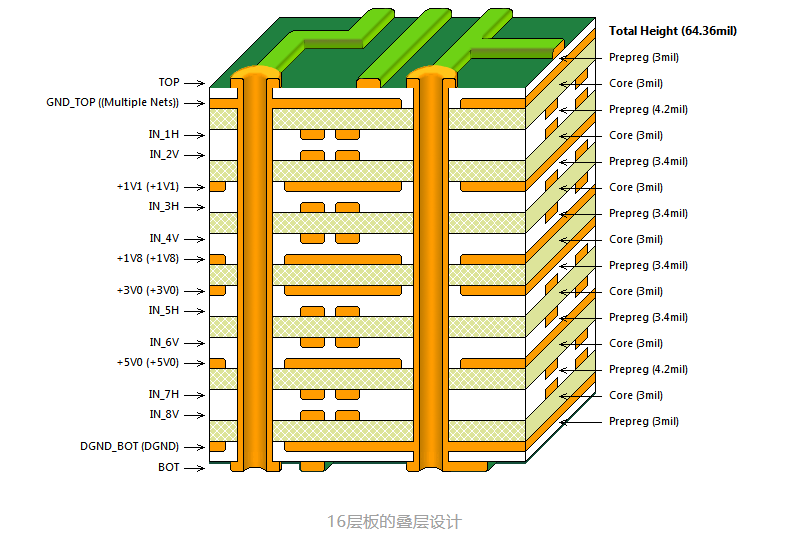

(3)疊層結(jié)構(gòu)與阻抗設(shè)計的示例(16層板、信號最高頻率400MHz)

a. 先決參數(shù)確定

單板層數(shù):信號層8個,3個電源層,3個地層,2個表層(器件+信號)

單板厚度:2mm

目標(biāo)阻抗:單端信號55±15Ω,差分信號100±15Ω

材質(zhì)選擇:FR4,Er=4.2,tanδ=0.002

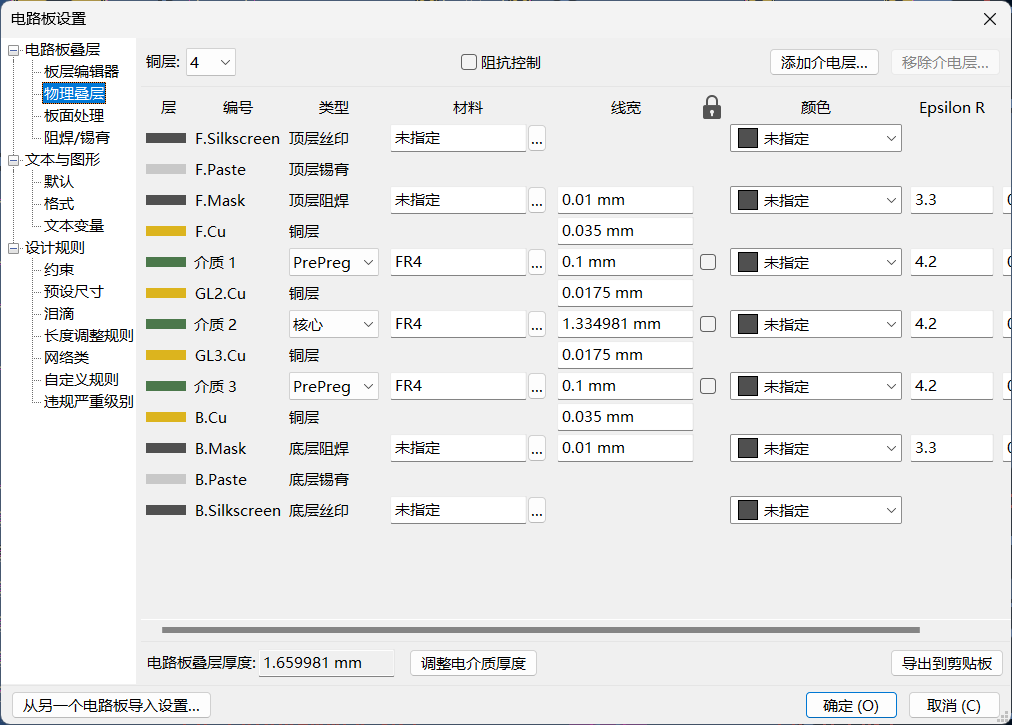

b. 層疊結(jié)構(gòu)與阻抗設(shè)計

層疊特征:PCB層疊結(jié)構(gòu)在材質(zhì)、厚度上完全對稱

確定每層厚度,正確選取Core ,PP,Cu:

5*Core1 : 0.69+0.69+3.94 mil=5.32 mil

2*Core2 : 0.69+0.69+5.9 mil=7.28 mil

6*PP1: 3.94 mil

2*PP2: 5.9 mil

Cu : 0.69 mil

總厚度:5*Core1+2*Core2+6*PP1+2*PP2+2*Cu=77.98 mil = 1.98 mm

確定每層厚度后,計算各層信號走線寬度:

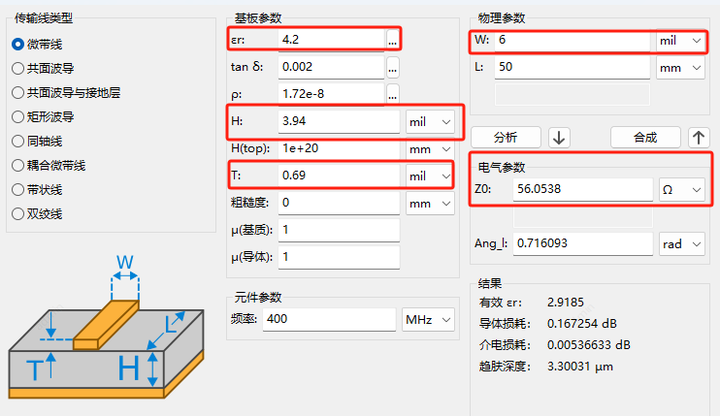

表層單端信號

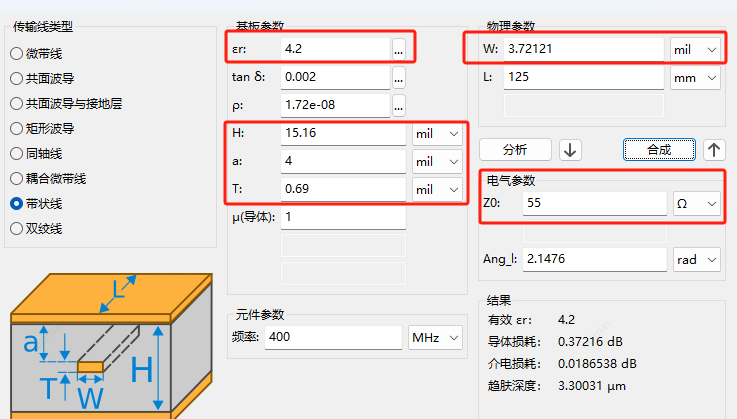

內(nèi)層單端信號

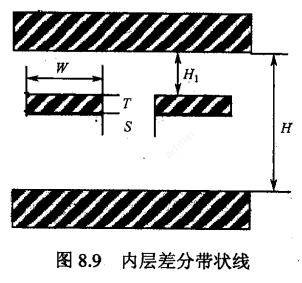

內(nèi)層差分信號(SI9000計算)

c. 電源層、地層的確定

層疊已經(jīng)確定了電源層或地層的位置,這一步確定第二、五、八、九、十二、十五層對應(yīng)電源層還是地層。

第八,九層位于PCB的中央,緊密相鄰,一層作為電源層,另一層作為地層,能起到很好的耦合效果。考慮到需分割的電源層(由四種電源共用)的電源平面較零碎,更需要與完整的地平面的耦合,因此,可確定第八層為地層,第九層為分割的電源層;

第二,十五層直接與表層相鄰,從EMC的角度考慮,應(yīng)選擇為地層;

第五,十二層用作為2.5V和3.3V的電源平面。

在確定好電源層和地層后,還需相應(yīng)地為信號層制定如下規(guī)則:

第十層的主要參考平面是第九層,而第九層是分割的電源層,對信號回流的影響較大,因此不建議在第十層走高速信號,對于一些非重要的信號,如控制信號,JTAG信號等,由于它們的阻抗控制要求較弱,可走在第十層。

第七層的主要參考平面是第八層,第八層是完整的地平面,可為第七層提供很好的回流路徑,但這兩層之間填充的材質(zhì)是PP,PCB制成后,在阻抗控制上可能存在一定偏差。因此,第七層可走高速信號,但對一些非常關(guān)鍵的高速信號,如單板上速率達到400MHz的差分對總線SPI4.2,不建議走在第七層。

第三層的主要參考平面是第二層,而第二層是完整的地平面,且兩層之間采用固態(tài)材質(zhì)填充,阻抗控制較好,適于走高速關(guān)鍵信號,同理,第十四層也適于走高速關(guān)鍵信號。

第四層的主要參考平面是第五層,第五層是完整的2.5V電源平面,兩層之間用固態(tài)材質(zhì)填充,可將高速關(guān)鍵信號走在第四層。在本設(shè)計中,有大量的DDR SDRAM接口信號線,其中,DDR SDRAM的地址,控制信號等都以2.5V為參考,建議將這些信號也走在第四層。

第十三層的主要參考平面是第十二層,第十二層是完整的3.3V電源平面,兩層之間用固態(tài)材質(zhì)填充,高速關(guān)鍵信號可走在第十三層,同時,建議將由3.3V供電的許多單端信號,如時鐘信號等,走在第十三層。

第六,十一層的主要參考平面分別是第五,十二層,與參考平面之間用PP填充,阻抗控制可能存在偏差,因此,在這兩層上可走高速信號,但不建議走非常關(guān)鍵的高速信號。

設(shè)計時需注意,第三,四層,第六,七層,第十,十一層,第十三,十四層,這四對信號層彼此相鄰,存在互相干擾的可能,因此在走線時,相鄰信號層應(yīng)正交走線,如第三層走線方向成橫向,則第四層走線應(yīng)成縱向。

【以上信息由艾博檢測整理發(fā)布,如有出入請及時指正,如有引用請注明出處,歡迎一起討論,我們一直在關(guān)注其發(fā)展!專注:CCC/SRRC/CTA/運營商入庫】

-

pcb

+關(guān)注

關(guān)注

4326文章

23161瀏覽量

399987 -

阻抗

+關(guān)注

關(guān)注

17文章

961瀏覽量

46265

發(fā)布評論請先 登錄

相關(guān)推薦

ADS8863輸入阻抗如何計算?

PCB 設(shè)計規(guī)則、層疊結(jié)構(gòu)的導(dǎo)入/導(dǎo)出

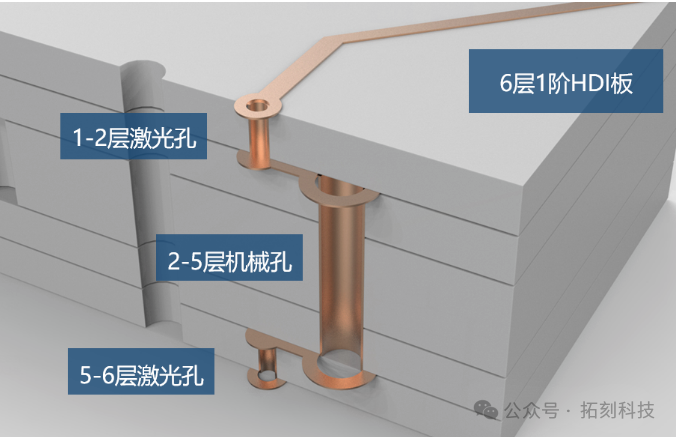

HDI的疊層結(jié)構(gòu)設(shè)計

如何根據(jù)貼片疊層電感參數(shù)進行選型

一文詳解九層板PCB結(jié)構(gòu)

PCB阻抗匹配過孔的多個因素你知道哪些?

PCB多層板為什么都是偶數(shù)層?奇數(shù)層不行嗎?

PCB阻抗設(shè)計12問,輕松帶你搞懂阻抗!

ROGERS高頻板阻抗設(shè)計要求有哪些?

什么是PCB疊層?PCB疊層設(shè)計原則

鈣鈦礦疊層電池:Topcon與HJT底電池性能對比研究

PCB疊層結(jié)構(gòu)與阻抗計算筆記分享

PCB疊層結(jié)構(gòu)與阻抗計算筆記分享

評論